1.CPU的组成

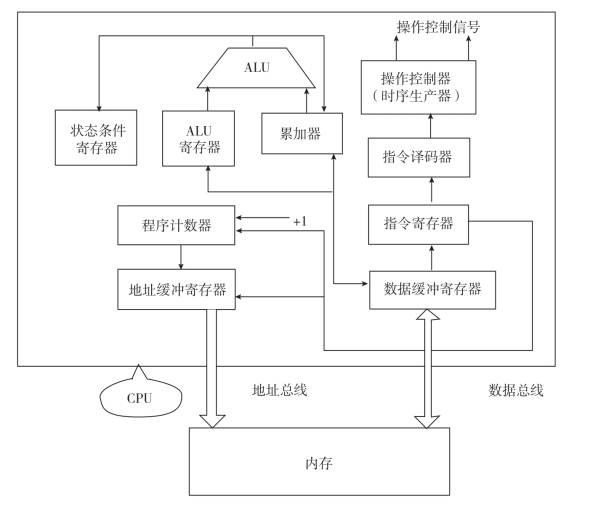

传统的CPU由运算器和控制器两部分组成,如图5-1所示。随着大规模集成电路技术的发展,早期放在CPU芯片外部的一些部件(主要是浮点处理器和Cache等)纷纷移入CPU内部,例如,Pentium系列CPU内部采用的1级(L1级)Cache,容量16KB,分成8KB指令Cache和8KB的数据Cache。现代CPU由运算器、控制器和cache三大部分组成,其中运算器和Cache已经作了介绍,这里我们主要叙述控制器部分。

(1)控制器

控制器由程序计数器(Pc)、地址缓冲寄存器(AR)、数据缓冲寄存器(DR)、指令寄存器(IR)、指令译码器、操作控制器(含时序产生器)组成,其核心是操作控制器(包括时序产生器),其他都是寄存器。控制器是发布命令的“决策机构”,即完成协调和指挥整个计算机系统的操作。它的主要功能包括以下几个方面。

图5-1 CPU的组成框图

①控制器负责从内存中取出一条指令,并指出下一条指令在内存中的地址。

②控制器对指令进行译码,产生相应的操作控制信号,发往运算、处理部件,控制完成规定的操作,如一个算术/逻辑运算操作、一次内存读/写操作或一个输入/输出操作。控制器指挥并控制CPU与内存和输入/输出设备之间的数据传送与处理。

(2)运算器

运算器由算术/逻辑单元(ALU)、ALU寄存器、累加器和状态条件寄存器组成,它是数据的加工/处理部件,执行算术运算和逻辑运算。相对控制器而言,运算器接受控制器的命令而进行动作,即运算器所进行的全部操作都是由控制器发出的控制信号来指挥的,所以它是执行部件。

2.CPU中的主要寄存器

CPU至少要有6类寄存器。

(1)数据缓冲寄存器

数据缓冲寄存器用来暂时存放从内存读出的一条指令(称为指令字)或一个数据(称为数据字);反之,当向内存存入一条指令或一个数据时,也暂时将它们存放在数据缓冲寄存器中。

缓冲寄存器的作用包括以下两方面。

①作为CPU与内存、输入/输出设备之间信息传送的中转站。(https://www.xing528.com)

②补偿CPU与内存、输入/输出设备之间在操作速度上的差别。

(2)指令寄存器

指令寄存器用来保存当前正在执行的一条指令,其中指令的操作码部分作为指令译码器的输入,指令译码器的输出通过操作控制器(包括时序发生器)发出具体的操作控制信号,控制运算、处理部件完成这条指令所规定的操作。指令寄存器中的指令来自数据缓冲寄存器。

(3)程序计数器

程序装入内存时,CPU自动得到程序的第一条指令地址(称为首地址)。为了保证程序能够连续地执行下去,CPU必须具有某些手段来确定下一条指令的地址。而程序计数器正是起到这种作用。在程序开始执行前,必须将它的起始地址,即程序的第一条指令所在的内存单元地址送人PC。当执行指令时,CPU将自动修改PC的内容,使其始终保持着下一条指令的地址。由于大多数指令都是按顺序来执行的,所以修改的过程通常只是简单的对PC加1(假定一条指令存放一个字节单元)。

但是,当遇到转移指令时,如JMP指令,那么后继指令的地址(即PC的内容)必须从指令的地址字段取得,而不是像通常一样按顺序对PC加1。因此程序计数器的结构应当是具有寄存和计数两种功能的结构,即既是计数器又是寄存器。

(4)地址缓冲寄存器

地址缓冲寄存器用来保存当前CPU所访问的内存单元的地址。由于在内存和CPU之间存在着操作速度上的差别,所以必须使用地址缓冲寄存器来保持地址信息,直到内存的读/写操作完成为止。

当CPU和内存进行信息交换时,都要使用地址缓冲寄存器和数据缓冲寄存器。地址缓冲寄存器和数据缓冲寄存器与其他寄存器一样,都是由若干位触发器组成,数据的存入一般采用电位/脉冲方式,即触发器的电位输入端连接数据信号,脉冲输入端连接控制信号,在控制信号作用下,瞬时地将数据打入寄存器。

(5)累加寄存器

累加寄存器(ACC或AC)通常简称为累加器,它是一个通用寄存器。其功能是:当运算器的算术/逻辑单元ALU执行算术或逻辑运算时,为ALU提供一个工作区,存放一个操作数或操作结果。

(6)状态条件寄存器

状态条件寄存器(PSW)保存由算术指令和逻辑指令执行结果所建立的各种标志,供CPU进行判断和测试,以便作进一步的处理。如运算结果进位标志(C)、运算结果溢出标志(V)、运算结果为零标志(Z)、运算结果为负标志(N)等。这些标志位通常分别由1位触发器保存,即0或1。通常,状态条件标志由ALU运算后自动填入,表示运算结果的状态,而不是运算结果。

除此之外,状态条件寄存器还保存中断和系统工作状态等信息,以便CPU能及时了解机器运行状态和程序运行状态。总之,状态条件寄存器是一个由各种状态条件标志拼凑而成的寄存器。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。