根据程序访问的局部性原理,可以在主存和CPU之间设置一个高速的、容量相对较小的存储器,如果当前正在执行的程序和数据存放在这个存储器中,当程序运行时,不必从主存储器取指令和取数据,只需访问这个高速存储器,以提高程序运行速度。这个存储器称作高速缓冲存储器Cache。

Cache由高速的SRAM组成,它的工作速度数倍于主存,全部功能由硬件实现,并且对程序员是透明的。

采用了“Cache-主存”存储体系以后,整个存储器的容量及单位成本能够与主存相当,而存取速度可以与Cache的读写速度相当,这就很好地解决了存储器系统的容量、存取速度及单位成本三个方面性能之间的矛盾。

在“Cache-主存”存储体系中,所有的程序代码和数据仍然都存放在主存中,Cache存储器只是在系统运行过程中,动态地存放了主存中的一部分程序块和数据块的副本。

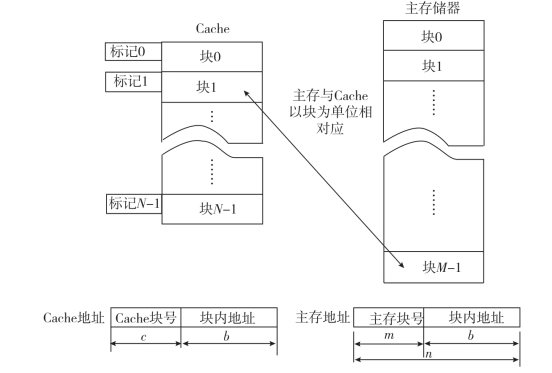

假设主存的地址为n位,则其共有2n个单元,将主存分块,每块有B个字节,则一共可以分成2n/B块。Cache也由同样大小的块组成,由于其容量小,所以块的数目小得多,也就是说,主存中只有一小部分块的内容可存放在Cache中,如图3-18所示。

图3-18 “Cache主存”存储体系(https://www.xing528.com)

在Cache中,每一块外加有一个标记,指明它是主存中哪一块的副本,所以该标记的内容包含了相应的主存中块的编号等相关信息。假定主存地址为n=m+b位,其中m称为主存的块地址,而b则称为主存的块内地址,即:主存的块数为M=2m,块内字节数为2b;同样,假定Cache地址为c+b位,其中c为Cache块地址,而b为Cache的块内地址,即Cache的块数为C=2c,块内字节数也为2b,通常使主存与Cache的块内地址码数量相同。

管理“主存-Cache”存储体系的部件称为Cache控制器,如图3-19所示。CPU与主存之间的数据传输必须经过Cache控制器进行。

图3-19 Cache存储系统基本结构

当CPU发出读请求时,Cache控制器将来自CPU的数据读/写请求转向Cache存储器,将主存地址的m位与Cache中块的标记在地址变换机构中相比较,根据其比较结果是否相等而分为两种情况,当比较结果相等时,说明需要的数据已在Cache中,称为“命中”,那么直接访问Cache就行了。在CPU与Cache之间,通常一次传送一个字,由于Cache速度与CPU速度相匹配,因此不需要插入等待状态,故CPU处于零等待状态。也就是说CPU与Cache达到了同步,为此,有时称高速缓存为同步Cache。当比较结果不相等时,说明需要的数据尚未调入Cache,称为“未命中”。则CPU需要对主存操作,那么就要把该数据所在的整个字块从主存一次调入Cache中。这时,CPU必须在其总线周期中插入等待周期。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。