1.逻辑代数、二进制

(1)逻辑代数

逻辑代数亦称布尔代数,是英国数学家乔治·布尔(George Boole)于1849年创立的。在当时,这种代数纯粹是一种数学游戏,没有物理意义,也没有现实意义,在其诞生100多年后才发现其应用价值。

逻辑是指事物的因果关系,或者说条件和结果的关系,这些因果关系可以用逻辑运算来表示,也就是用逻辑代数来描述。

事物往往存在两种对立的状态,例如“真”和“假”,在逻辑代数中可以抽象地表示为0和1,称为逻辑0状态和逻辑1状态。逻辑代数是按一定的逻辑关系进行运算的代数,是分析和设计数字电路的数学工具。在逻辑代数,只有0和1两种逻辑值,有与、或、非三种基本逻辑运算,还有与或、与非、与或非、异或等几种导出逻辑运算。

逻辑代数中的变量称为逻辑变量,用大写字母表示。逻辑变量的取值只有两种,即逻辑0和逻辑1,0和1称为逻辑常量,它们并不表示数量的大小,而是表示两种对立的逻辑状态。

与运算(逻辑与、逻辑乘)定义为

0·0=0

0·1=0

1·0=0

1·1=1

或运算(逻辑或、逻辑加)定义为

0+0=0

0+1=1

1+0=1

1+1=1

非运算的定义为0和1互换,即非0为1,非1为0。

(2)二进制

二进制是计算技术中广泛采用的一种数制。

二进制数据是用0和1两个数码来表示的数。它的基数为2,进位规则是“逢二进一”,借位规则是“借一当二”。二进制于18世纪由德国数理哲学大师戈特弗里德·威廉·凡·莱布尼茨(Gottfriend Wilhelm von Leibniz)发现。

当前的计算机系统使用的基本上都是二进制系统。计算机内部采用二进制是基于如下的原因:

1)技术实现简单,计算机是由逻辑电路组成,逻辑电路通常只有两个状态,开关的接通与断开,这两种状态正好可以用“1”和“0”表示。

2)简化运算规则,两个二进制数的和、积运算组合各有三种,运算规则简单,有利于简化计算机内部结构,提高运算速度。

3)适合逻辑运算,逻辑代数是逻辑运算的理论依据,二进制只有两个数码,正好与逻辑代数中的“真”和“假”相吻合。

4)易于进行转换,二进制与十进制数易于互相转换。

5)用二进制表示数据具有抗干扰能力强、可靠性高等优点,因为每位数据只有高低两个状态,当受到一定程度的干扰时,仍能可靠地分辨出它是高还是低。

二进制的缺点是表示一个数时位数多,因此实际使用中多采用送入数字系统前用十进制,送入机器后再转换成二进制数,让数字系统进行运算,运算结束后再将二进制转换为十进制供人们阅读。

为了克服二进制位数多的缺点,一般不直接显示二进制的数,而是把它们用八进制的数或十六进制的数显示。

2.基本逻辑门电路

(1)二极管门电路

用电子电路来实现逻辑运算时,它的输入输出量均为电位(或电平)。输入量作为条件,输出量作为结果,输入与输出量之间能满足某逻辑关系的电路,称为某门电路。

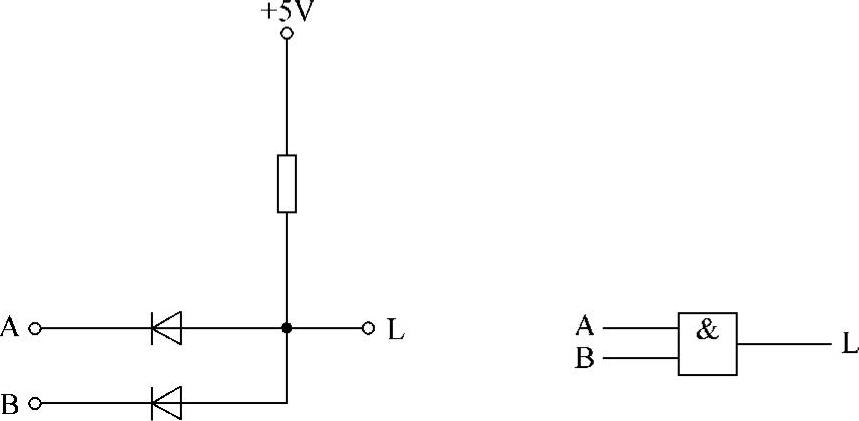

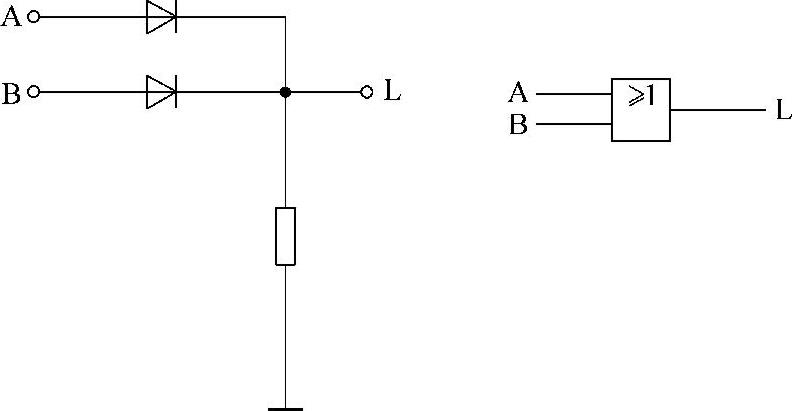

二极管本身就是一个开关器件,因此可直接构成门电路(见图4-15和图4-16)。

图4-15 二极管与门电路

图4-16 二极管或门电路

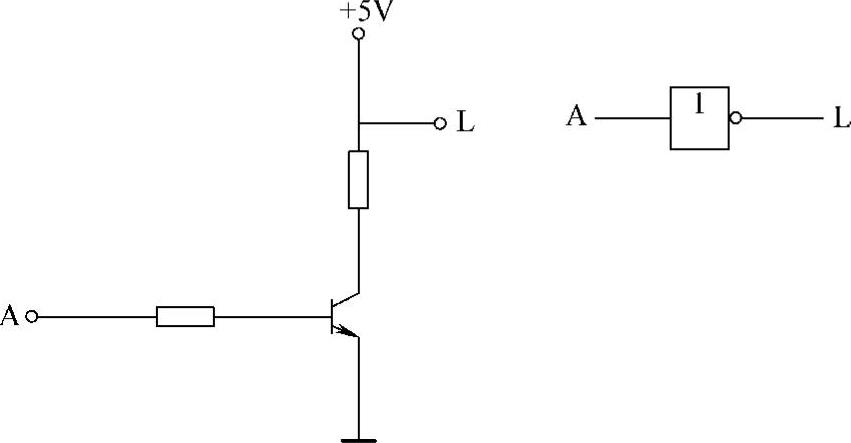

(2)晶体管门电路

在数字电路中,晶体管作为开关器件应用时,经常工作在截止区和饱和区,放大区只出现在晶体管由饱和变截止或由截止变饱和的过渡过程中(见图4-17)。

(3)复合门电路

虽然利用以上的基本与、或、非门电路,可以实现与、或、非三种逻辑运算。但是由于它们的输出电阻比较大,输出电平相对输入电平会有较大的压降,带负载的能力差,开关性能也不理想,因此基本的与、或、非门电路不具有实用性。解决的办法之一是采用二极管与晶体管门的组合,组成与非门、或非门电路,也就是所谓的DTL复合门电路。而使用更加广泛的是晶体管-晶体管逻辑(TTL)门电路和互补金属氧化物半导体(CMOS)逻辑门电路等组成的与非门及或非门电路,用多个的与非门/或非门再组成其他的逻辑电路。

图4-17 晶体管非门电路

与非门及或非门在负载能力、工作速度和可靠性方面都大为提高,是逻辑电路中最常用的基本单元。

3.组合逻辑电路

在任何时刻,输出状态只决定于同一时刻各输入状态的组合,而与先前状态无关的逻辑电路称为组合逻辑电路。

组合逻辑电路是与时序逻辑电路相对比而言的,其特点是电路结构上输入输出间没有反馈延迟的环路,因而电路没有记忆功能,电路的输出仅与当时电路输入的逻辑变量值有关,而与电路原来处于何种状态没有关系。

(1)编码器、译码器

编码器是指能实现用二进制对输入变量进行编码的电路,对于每一路输入信号,输出唯一的二进制代码数。如果输入信号有n个,输出信号的组合数目为m个,m=2n。

1)4(=22)种情况,需2位二进制码就能将所有情况表示;

2)8(=23)种情况,需3位二进制码就能将所有情况表示;

3)16(=24)种情况,需4位二进制码就能将所有情况表示;

4)2n种情况,需要n位二进制码就能完全表示。

5)用n位二进制代码对2n个信号进行编码的电路就是二进制编码器。

译码器的功能与编码器相反,它将具有特定含义的不同二进制码辨别出来,并转换为控制信号。

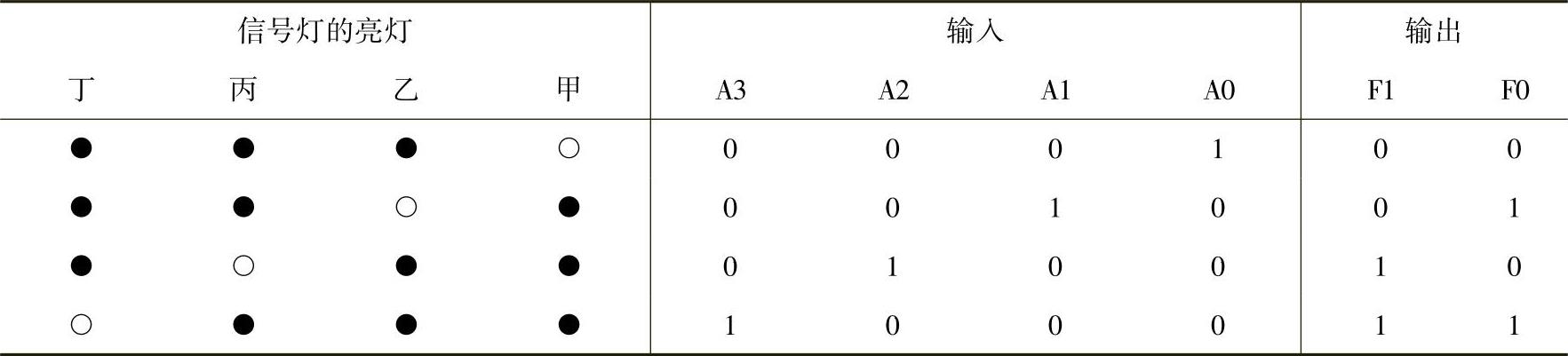

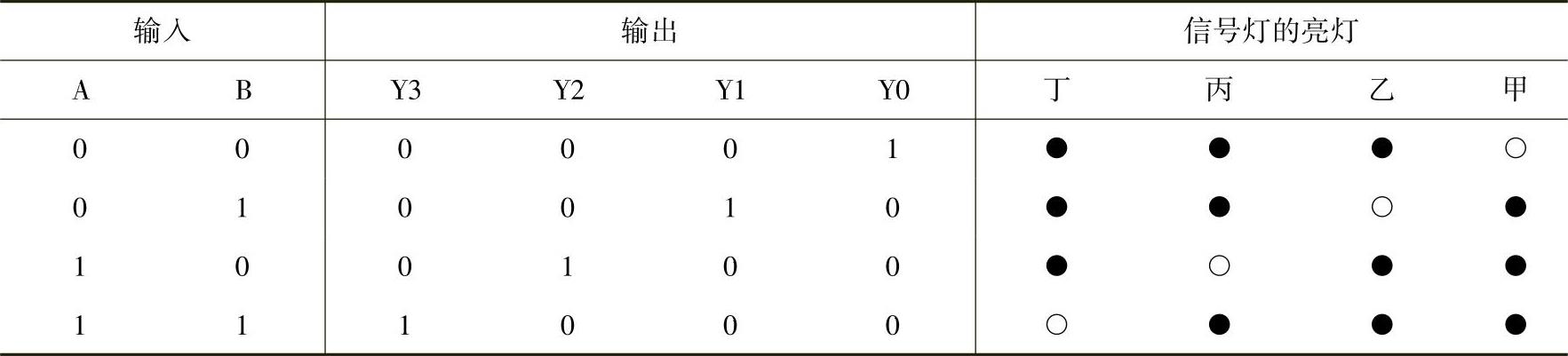

下面是一对比较简单的编码器和译码器(见表4-1、表4-2、图4-18、图4-19)。

表4-1 编码器数值

注:F0=A3+A1,F1=A3+A2。

实现微机系统中存储器或输入/输出接口芯片的地址译码是译码器的一个典型用途。

译码器分为二进制译码器、十进制译码器、集成译码器和数字显示译码驱动电路。其中二进制译码器是一种最简单的变量译码器,它的输出端全是最小项。

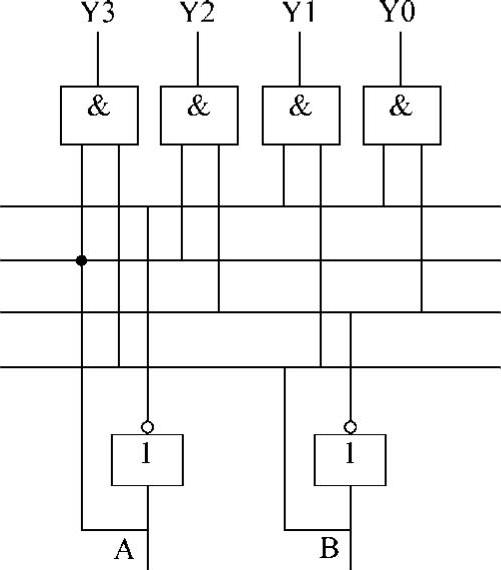

表4-2 译码器数值

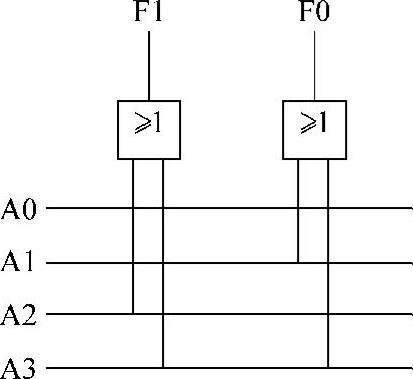

图4-18 4-2线编码器

注:将4个信号灯的亮灯信号编为两位的二进制代码。

图4-19 译码器

注:输入是一组两位二进制代码AB,输出是与代码状态相对应的4个信号Y3、Y2、Y1、Y0。

(2)数据分配器、数据选择器

将公共数据线上的信号传送到不同单元中去的逻辑电路称为数据分配器。

按需要从多个输入信号中选择一个送到公共数据线上的逻辑电路称为数据选择器。

(3)数字比较器

数字比较器是指能实现判别两个或多个数大小或是否相等的电路。

(4)算术运算电路(https://www.xing528.com)

加法器是指能实现算术运算的逻辑电路,包括半加器/全加器、半减器/全减器等。

4.时序逻辑电路

(1)触发器

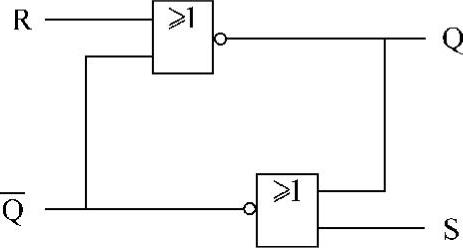

触发器(Flip Flop)也叫双稳态多谐振荡器(Bistable Multi-Vibrator),是一种可以存储电路状态的电子器件。一个触发器可以存储一位二进制码。

最简单的RS触发器由两个或非门、两个输入端和两个输出端组成(见图4-20)。复杂一些的有CLK(Clock,时钟)端和D(Data,数据)端,在CLK端为高电平时跟随D端状态,而在CLK端变为低电平的瞬间锁存信号,称为D触发器。更常用的是两个简单D触发器级联而成的在时钟下跳沿锁存信号的边缘D触发器,广泛应用于计数器、运算器、存储器等电子部件中。

图4-20 RS触发器

电路结构是指电路中门电路的种类及组合方式,基本RS触发器、同步RS触发器、主从触发器、边缘触发器等是指电路结构的不同形式。由于电路结构形式的不同,带来了各不相同的动作特点。

同一种逻辑功能的触发器可以用不同的电路结构实现,反过来说,用同一种电路结构形式可以作成不同逻辑功能的触发器。

触发器的类型按逻辑功能不同分为RS触发器、D触发器、JK触发器、T触发器。

触发器的类型按触发方式不同分为电平触发器、边沿触发器和主从触发器。

触发器的类型按电路结构不同分为基本RS触发器和钟控触发器。

触发器的类型按存储数据原理不同分为静态触发器和动态触发器。

触发器的类型按构成触发器的基本器件不同分为双极型触发器和CMOS型触发器。

(2)寄存器

用来存放二进制数据或代码的电路称为寄存器。

寄存器是由具有存储功能的触发器组合起来构成的。一个触发器可以存储一位二进制代码,存放n位二进制代码的寄存器,需用n个触发器来构成。

按功能可分为基本寄存器和移位寄存器两种。

移位寄存器中的数据可以在移位脉冲作用下一次逐位右移或左移,数据既可以并行输入、并行输出,也可以串行输入、串行输出,还可以并行输入、串行输出,串行输入、并行输出,十分灵活,用途也很广。

(3)二进制计数器

由于双稳态触发器有“1”和“0”两个状态,所以一个触发器可以表示一位二进制数。如果要表示n位二进制数,就得用n个触发器。

二进制计数器有异步二进制计数器和同步二进制计数器两种。

(4)BCD码计数器

BCD码计数器为十进制计数器,便于人工进行读数。

5.脉冲信号电路

(1)单稳态触发器

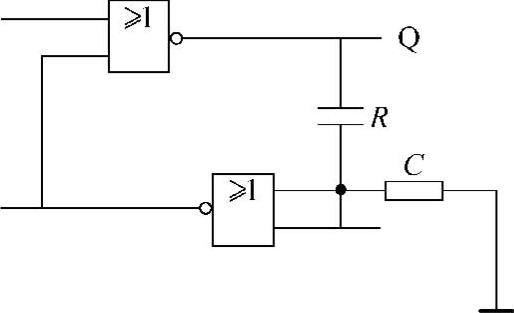

单稳态触发器的特点是它有一个稳定状态和一个暂稳状态;它在外来触发脉冲的作用下,可以从稳态翻转到暂稳态;在暂稳态维持一段时间以后,将自动地返回到稳态,而暂稳态持续的时间与触发脉冲无关,只取决于电路本身的参数(见图4-21)。

利用单稳态触发器能产生一定宽度的脉冲这一特性,可以将过窄或过宽的输入脉冲整形成固定宽度的脉冲输出。

图4-21 与非门构成的微分型单稳态触发器

注:由于电路中RC延时环节的作用,该暂态维持一段时间又回到原来的稳态,暂稳态维持的时间取决于RC的参数值。

若将单稳态触发器的输出VO接至与门的一个输入端,与门的另一个输入端输入高频脉冲序列Vf。单稳态触发器在输入负向窄脉冲到来时开始翻转,与门开启,允许高频脉冲序列通过与门从其输出端VAND输出。经过定时时间tpo后,单稳态触发器恢复稳态,与门关闭,禁止高频脉冲序列输出,由此实现了高频脉冲序列的定时选通功能。

(2)多谐振荡器

多谐振荡器又称无稳电路,是一种产生矩形脉冲波的自激振荡器。由于矩形波含有丰富的高次谐波,所以矩形波振荡器又称为多谐振荡器。多谐振荡器没有稳态,不需外加触发信号,当接通电源后,便可以自动地周而复始地产生矩形波输出。

多谐振荡器主要用于产生各种方波或时钟信号。典型的多谐振荡器有自激多谐振荡器和石英晶体振荡器。

(3)施密特触发器

施密特触发器是一种特殊的门电路。门电路有一个阈值电压,当输入电压从低电平上升到阈值电压或从高电平下降到阈值电压时,电路的状态将发生变化。与普通的门电路不同,施密特触发器有两个阈值电压,分别称为正向阈值电压和负向阈值电压。

在输入信号从低电平上升到高电平的过程中使电路状态发生变化的输入电压称为正向阈值电压(Vt+)。

在输入信号从高电平下降到低电平的过程中使电路状态发生变化的输入电压称为负向阈值电压(Vt-)。

正向阈值电压与负向阈值电压之差称为回差电压(ΔVt)。

普通门电路的电压传输特性曲线是单调的,施密特触发器的电压传输特性曲线则是滞回的。

利用施密特触发器的特性可以将非矩形波变换成矩形波,也可以恢复波形,还可以进行脉冲鉴幅。

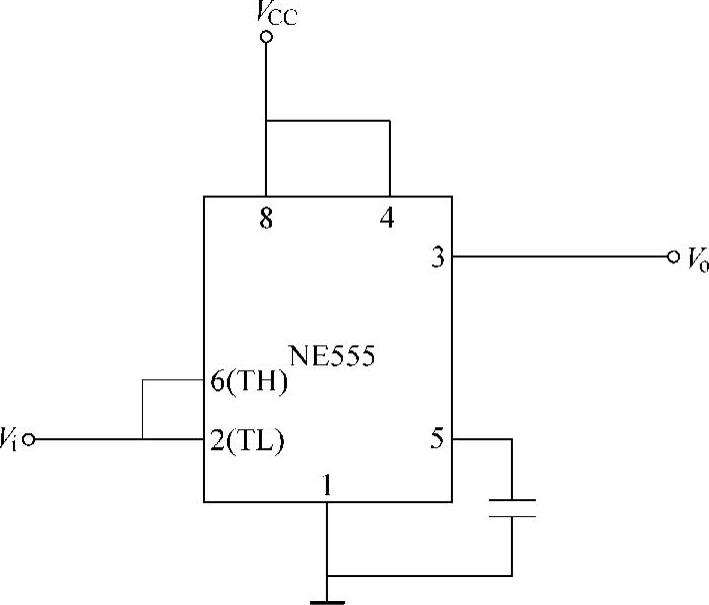

6.555时基电路

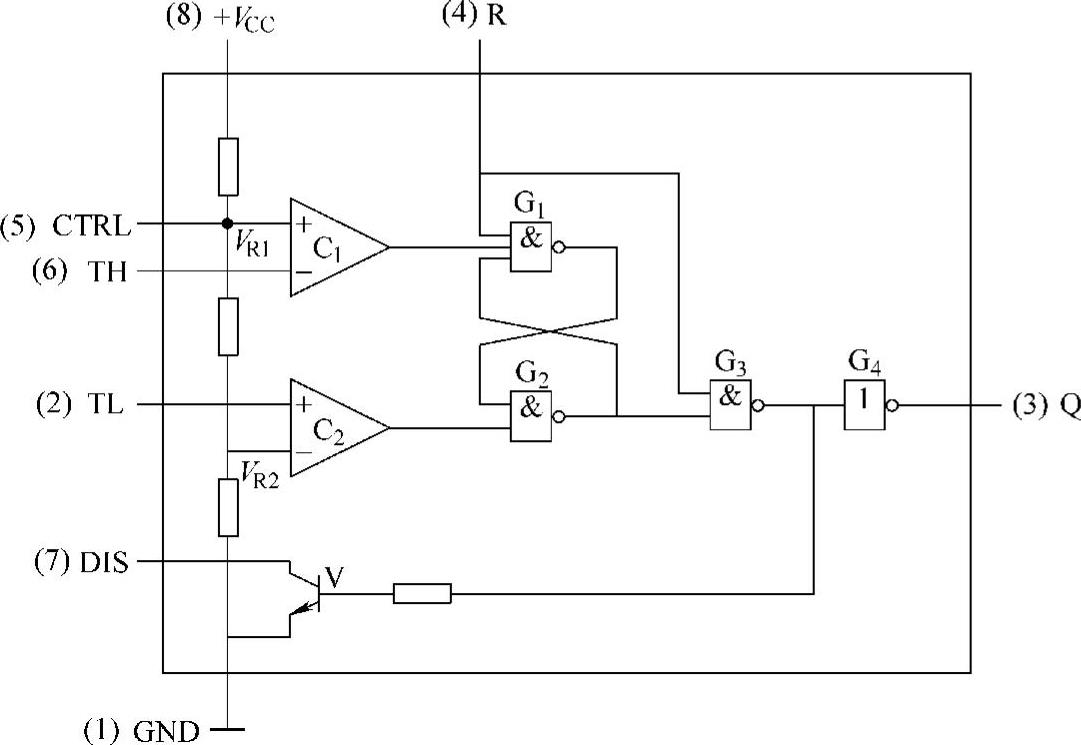

1972年Signetics公司首次推出NE555双极性时基集成电路,原本旨在取代体积大、定时精度差的机械式定时器,但器件投放市场后,由于该集成电路成本低、使用方便、稳定性好,因此受到各界电子、电器设计与制作人员的欢迎,其应用范围远远超出了设计者的初衷,其用途几乎涉及电子应用的各个领域。自世界上第一块NE555集成电路诞生至今30多年以来,其市场一直经久不衰,直至今天世界各国多个集成电路生产厂商仍竞相生产其同功能产品(见图4-22)。

图4-22 555时基电路的内部原理图

注:1.555电路有8个引出端:1地端、2低触发端、3输出端、4复位端、5电压控制端、6高触发端、7放电端、8电源端。数字1~8为器件引脚编号。

2.555定时器由电阻分压器、比较器、基本RS触发器、晶体管开关和输出缓冲器五部分组成。

3.分压器由三个阻值均为5kΩ的电阻串联连接构成,为比较器C1、C2提供参考电压。如果在电压控制端5另加控制电压,可以改变比较器参考电压的值。若工作中不使用控制端5时,则控制端5通过一个0.01μF的电容接地,以旁路高频干扰。

4.比较器C1、C2分别由集成运算放大器构成。TH称为高触发端,TL称为低触发端。当同相输入端电压大于反相输入端电压时,比较器输出为高电平;反之,比较器输出为低电平。基本RS触发器由两个与非门G1、G2构成,触发器的状态受比较器输出的控制。

5.输出缓冲器由接在输出端的非门G4构成,其作用是提高定时器的带负载能力,隔离负载对定时器的影响。晶体管V在此电路中作为开关使用,其状态受触发器的控制。

555时基电路最初用TTL技术生产,后来又出现了利用CMOS技术生产的电路,代表型号是7555,而且还出现了将2只555或4只555封装在一起的556或558,使555家族更添异彩。

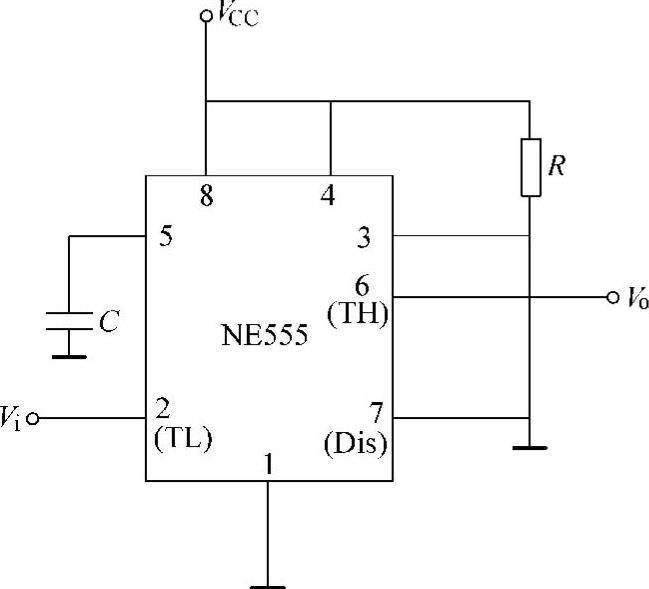

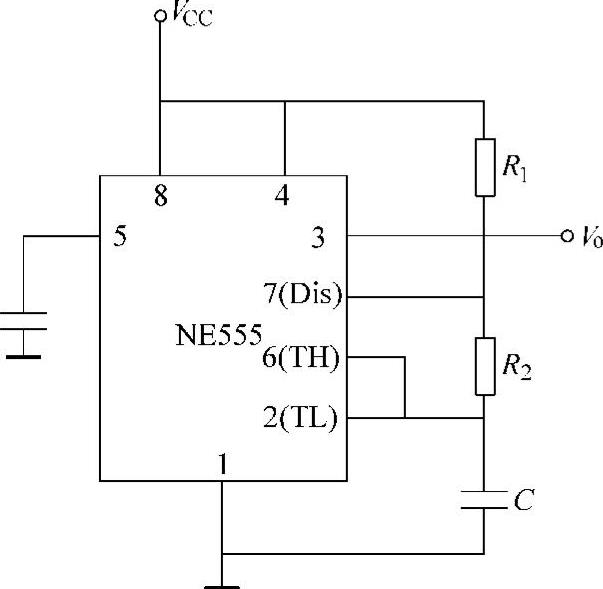

555定时器是一种多功能的数字-模拟混合集成电路,利用它进行不同的组合可方便地构成单稳态触发器、多谐振荡器和施密特触发器(见图4-23~图4-25)。由于使用灵活、方便,所以555定时器在波形的产生与变换、测量与控制、家用电器、电子玩具等许多领域中都得到了应用。

图4-23 555定时器构成的单稳态触发器(输出脉冲宽度Tw=RCln3≈1.1RC)

注:1.稳态时,触发脉冲Vi为高电平,基本RS触发器处于0状态,晶体管导通,TH和Dis端处于低电平,输出为低电平。输入窄触发负脉冲到来后,即TL端由高电平跳变到低电平时,单稳态触发器电路状态由稳态翻转到暂态,输出高电平,晶体管V截止,电源通过电阻给电容充电。电路由稳态翻转到暂态,输入负跳变触发脉冲结束,Vi由低电平又跳变到为高电平。

2.在暂稳态期间,电源给电容充电,随着充电进行,电容两端电压升高,TH和Dis端电位也随之升高。当TH端电位上升到2VCC/3时,输出又变为低电平。同时晶体管V导通,电容器通过V放电,电路由暂稳态自动返回到稳态。暂稳态时间由RC电路参数决定。

图4-24 555定时器构成的多谐振荡器[振荡周期T≈0.7(R1+2R2)C]

注:1.电路接通电源前,定时电容上的电压为0,TH、TL端的电位为0。电路接通电源开始时,由于电容器上的电压不能突变,所以TH、TL端均处于低电位,使比较器C2输出为0。此时,基本RS触发器处于1状态,定时器输出高电平,使晶体管开关截止,电源通过R1、R2给电容器充电,使TH、TL端的电位逐渐升高。电路处于暂稳态,定时器输出保持高电平。

2.当电容器充电使电容两端电压上升到2VCC/3时,TH、TL端的电位也同时上升到此值,使比较器C1输出为0,比较器C2的输出为1,此时,基本RS触发器处于0状态,定时器输出跳变为低电平,同时使晶体管V导通,电容器C经R2和晶体管V放电,TH、TL端的电位逐渐下降,电路处于另一个暂稳态,定时器输出保持低电平。

3.当电容器放电使电容两端电压下降到1VCC/3时,TH、TL端的电位也同时下降到此值,使比较器C1输出为1,比较器C2的输出为0,此时,基本RS触发器置1,定时器输出跳变为高电平,同时又使晶体管V截止,电源又通过电阻给电容器充电,……,如此周而复始地使两个暂稳态不停地相互转换,在定时器的输出端就得到矩形波脉冲信号输出。

TH(高阈值端)是比较器C1的输入端,TL(低阈值端)是比较器C2的输入端;C1和C2的参考电压(电压比较的基准)VR1和VR2由VCC经三个5kΩ电阻分压给出,在控制电压输入端CTRL悬空时,VR1=2VCC/3,VR2=VCC/3;如果CTRL端外接固定电压,则VR1=VCTRL,VR2=VCTRL/2。

R端是置零输入端,只要在该端加上低电平,输入端Q便立即被置成低电平,不受其他输入端的影响,正常工作时必须使之处于高电平。

图4-25 555定时器构成的施密特触发器

注:将555定时器的高触发端TH和低触发端TL连接起来就构成了施密特触发器。

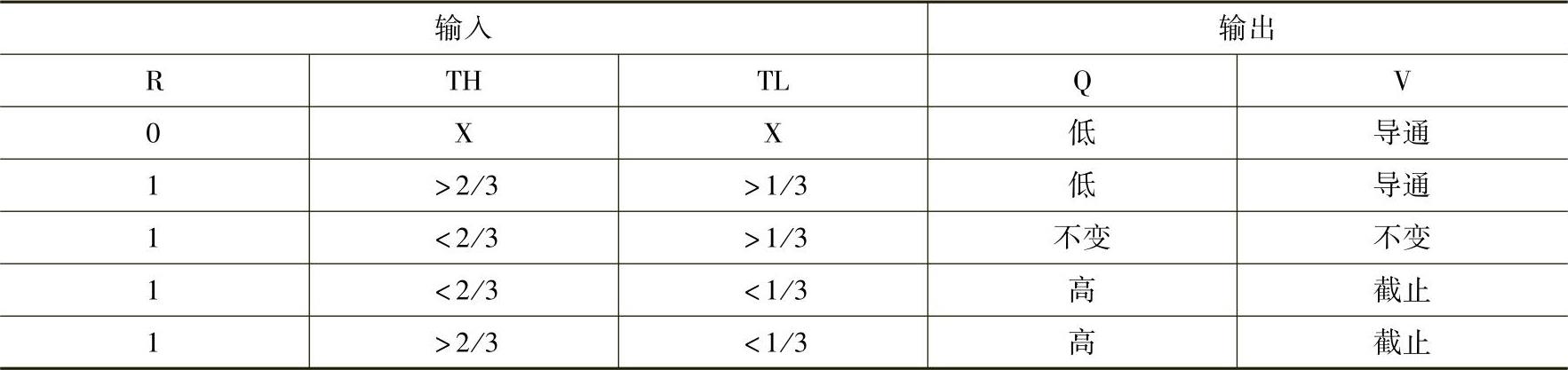

当VTH大于VR1,比较器C1的输出为0;VTL大于VR2时,比较器C2输出为1;基本RS触发器被置0,晶体管V导通,同时Q为低电平(见表4-3)。

表4-3 555功能

为了提高电路的带负载能力,还在输出端设置了缓冲器G4,如果将DIS端经过电阻接到电源上,那么只要这个电阻的阻值足够大,Q为高电平时,DIS端也一定为高电平,反之亦然。

555定时器能在很宽的电源电压范围内工作,并可承受较大的负载电流。如果使VR1和VR2的低电平信号发生在输入电压信号的不同电平,那么输出与输入之间关系将为施密特触发特性;如果能使VR1和VR2的低电平信号交替反复出现,那么就可以得到多谐振荡器。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。