利用三总线结构扩展多片程序存储器(也适于后述的数据存储器和I/O口),需要通过地址总线进行片选操作,以便选中所需的外扩器件,称为地址译码,分为线译码法和全译码法两种。

1.线译码法

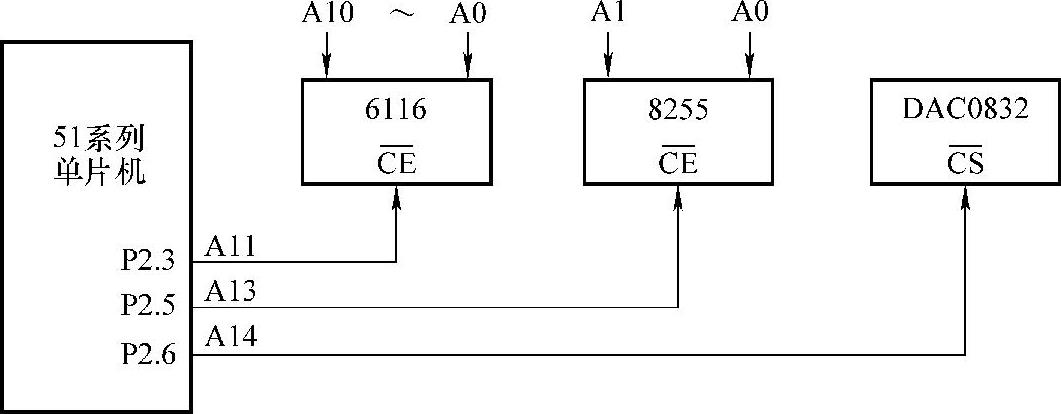

线译码法又称线选法,方法是除了P2口和P0口提供所选器件内部储存单元的地址线之外,把P2口剩余的高端地址线分别连接到所选器件的片选端CE(低电平有效)。图4-4是线译码法片选控制示例。

图4-4 线译码法片选控制示例

静态RAM(6116)为2KB容量,最大占用A0~A10共11条地址线(由P0口和P2口的P2.0~P2.2提供)。把P2口余下的P2.3、P2.5、P2.6作为三个器件的片选线(建议未用到的P2口线悬空,使呈1状态,以避免地址重叠),线译码法的地址范围见表4-1。线选法只适用于器件个数不超过P2口片选线的场合,硬件电路简单,但地址范围不连续。

表4-1 线译码法的地址范围

2.全译码法

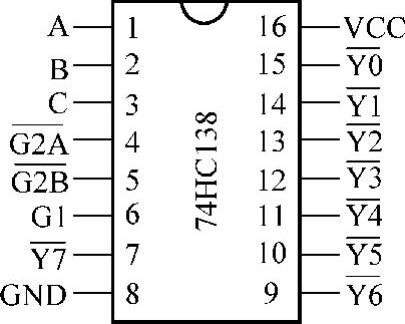

当扩展器件个数多于P2口提供的片选线时可采用全译码法,把寻址后P2口剩余的高端地址通过译码器,利用译码输出线作片选线。常用的3-8译码器(如74HC138),由3条输入线转换成8条输出线,3-8译码器引脚见图4-5(三个控制端G1、 、

、 连接为“高、低、低”的电平关系时,才能有译码输出);3-8译码器逻辑功能见表4-2。还有4-16译码器(如74HC154),由4条输入线转换成16条输出线。

连接为“高、低、低”的电平关系时,才能有译码输出);3-8译码器逻辑功能见表4-2。还有4-16译码器(如74HC154),由4条输入线转换成16条输出线。

(https://www.xing528.com)

(https://www.xing528.com)

图4-5 3-8译码器引脚

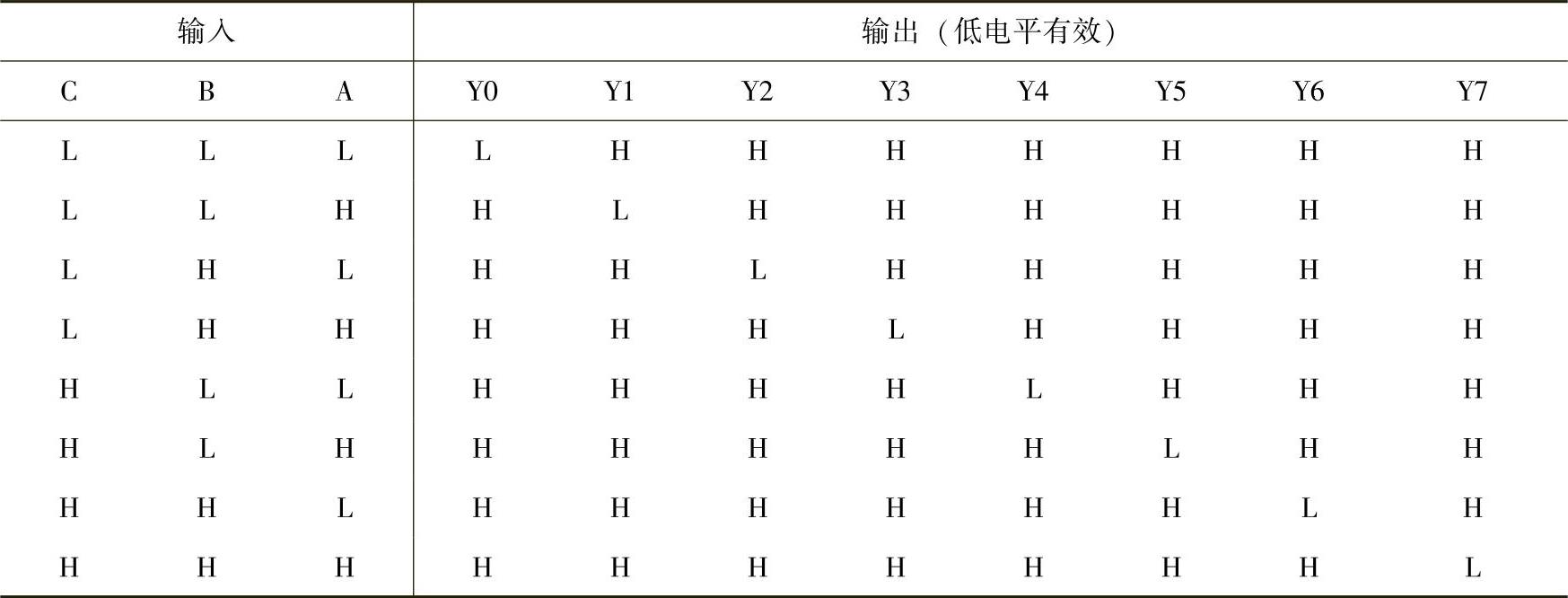

表4-2 3-8译码器逻辑功能

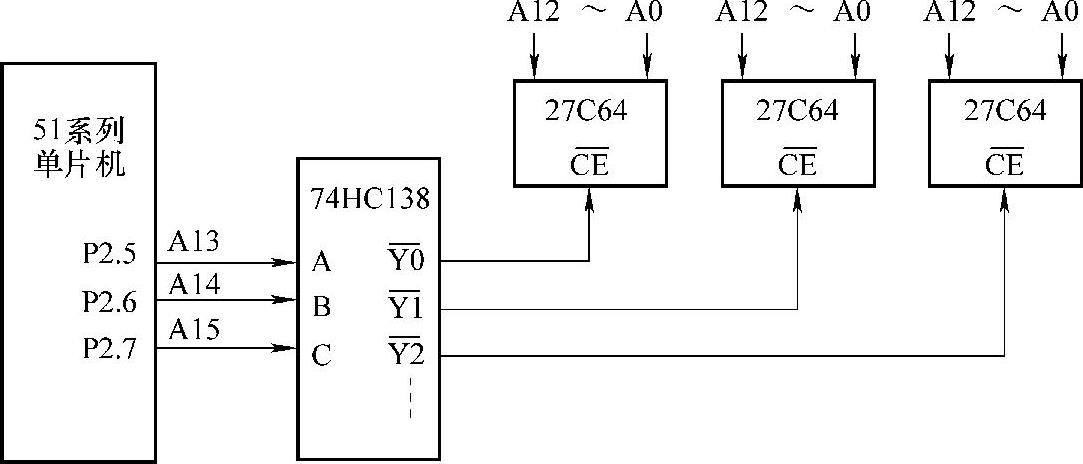

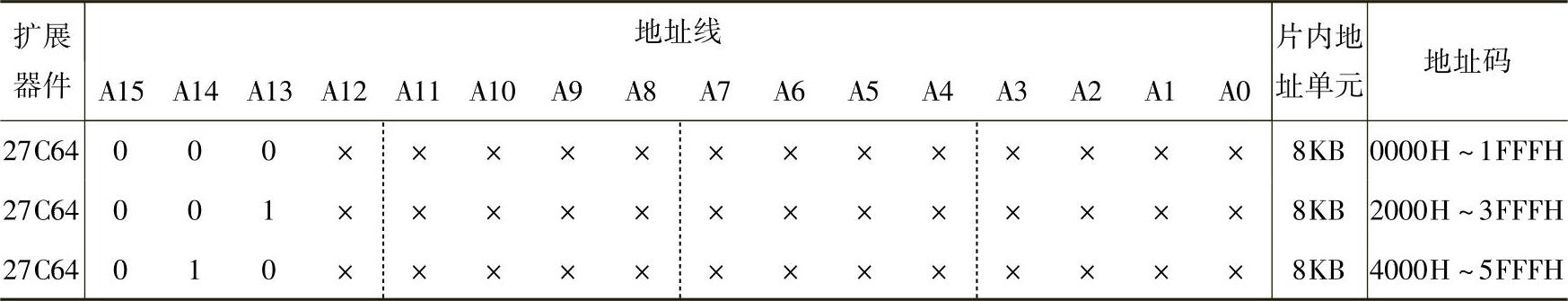

图4-6是全译码法的片选控制示例,采用3-8译码器扩展了3片程序存储器(27C64)。用P2口的高端地址线P2.7、P2.6、P2.5参与译码,全译码法的地址范围见表4-3。

图4-6 全译码法的片选控制示例

表4-3 全译码法的地址范围

从表中可看到,全译码法的地址连续,可最大限度利用地址空间。片选线数不受剩余的P2口线限制,但需附加译码电路。上述两种译码法具体选用哪一种,要取决于对器件使用的综合考虑。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。