1. PS/2 鼠标接口简介

PS/2 接口鼠标采用一种双向同步串行协议,换句话说,每在时钟线上发一个脉冲,就在数据线上发送一位数据。鼠标可以发送数据到主机,而主机也可以发送数据到设备,但主机总是在总线上有优先权,它可以在任何时候抑制来自鼠标的通信,只要把时钟拉低即可。

常见鼠标支持输入X(左右)位移、Y(上下)位移、左键、中键和右键鼠标等功能。标准的鼠标有两个计数器,保持位移的跟踪,X 位移计数器和Y 位移计数器。可存放9位二进制补码,并且每个计数器都有相关的溢出标志,它们的内容连同3 个鼠标按钮的状态一起以3 字节移动数据包的形式发送给主机。位移计数器表示从最后一次位移数据包被送往主机后,有位移量发生。

当鼠标读取它的输入的时候,它记录按键的当前状态,然后检查位移,如果发生位移它就增加(对正位移)或减少(对负位移)X 和/或Y 位移计数器的值。如果有一个计数器溢出了就设置相应的溢出标志。

PS/2 鼠标有4 种工作模式:Reset 模式,当鼠标上电或主机发复位命令 0xFF 给它时,进入这种模式;Stream 模式鼠标的默认模式,当鼠标上电或复位完成后,自动进入此模式,鼠标基本上以此模式工作;Remote 模式,只有在主机发送了模式设置命令0xF0 后,鼠标才进入这种模式;Wrap 模式,这种模式只用于测试鼠标与主机连接是否正确。

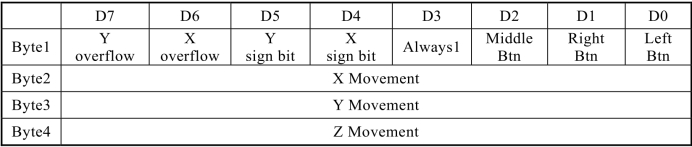

PS/2鼠标在工作过程中,会及时把它的状态数据发送给主机,发送的数据包格式见表5.9。

表5.9 3 字节数据包格式

在表5.9 中,Byte1 中的Bit0、Bit1、Bit2 分别表示左、右、中键的状态,状态值0表示释放,1 表示按下。Byte2 和Byte3 分别表示X 轴和Y 轴方向的移动计量值,是二进制补码值。Byte4 的低4 位表示滚轮的移动计量值,也是二进制补码值,高4 位作为扩展符号位。这种数据包由带滚轮的三键三维鼠标产生。若是不带滚轮的三键鼠标,产生的数据包除没有Byte4 外其余的相同。

3. PS/2 鼠标到主机的通信

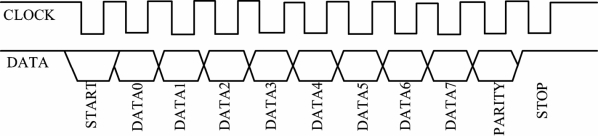

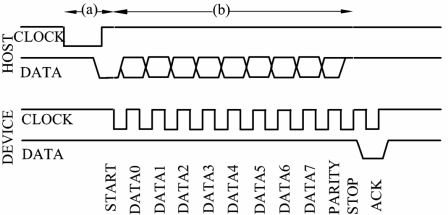

从鼠标发送到主机的数据在时钟信号的下降沿(当时钟从高变到低的时候)被读取,其数据通信协议满足PS/2 协议,其时序如图5.23 所示。

图5.23 S/2 设备到主机的通信时序

从PS/2 鼠标向主机发送一个字节可按照下面的步骤进行:

(1)检测时钟线电平,如果时钟线为低,则延时50 μs。

(2)检测判断时钟信号是否为高,为高,则向下执行,为低,则转到(1)。

(3)检测数据线是否为高,如果为高则继续执行,如果为低,则放弃发送(此时主机在向PS/2 设备发送数据,所以PS/2 设备要转移到接收程序处接收数据)。

(4)延时20 μs(如果此时正在发送起始位,则应延时40 μs)。

(5)输出起始位(0)到数据线上。这里要注意的是在送出每一位后都要检测时钟线,以确保PC 机没有抑制PS/2 设备,如果有则中止发送。

(6)输出8 个数据位到数据线上。

(7)输出校验位。

(8)输出停止位(1)。

(9)延时30 μs(如果在发送停止位时释放时钟信号则应延时50 μs)。

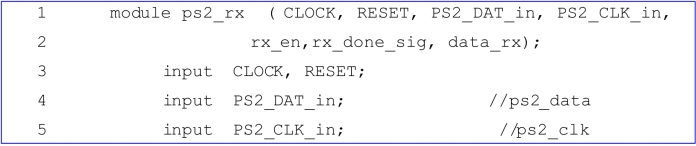

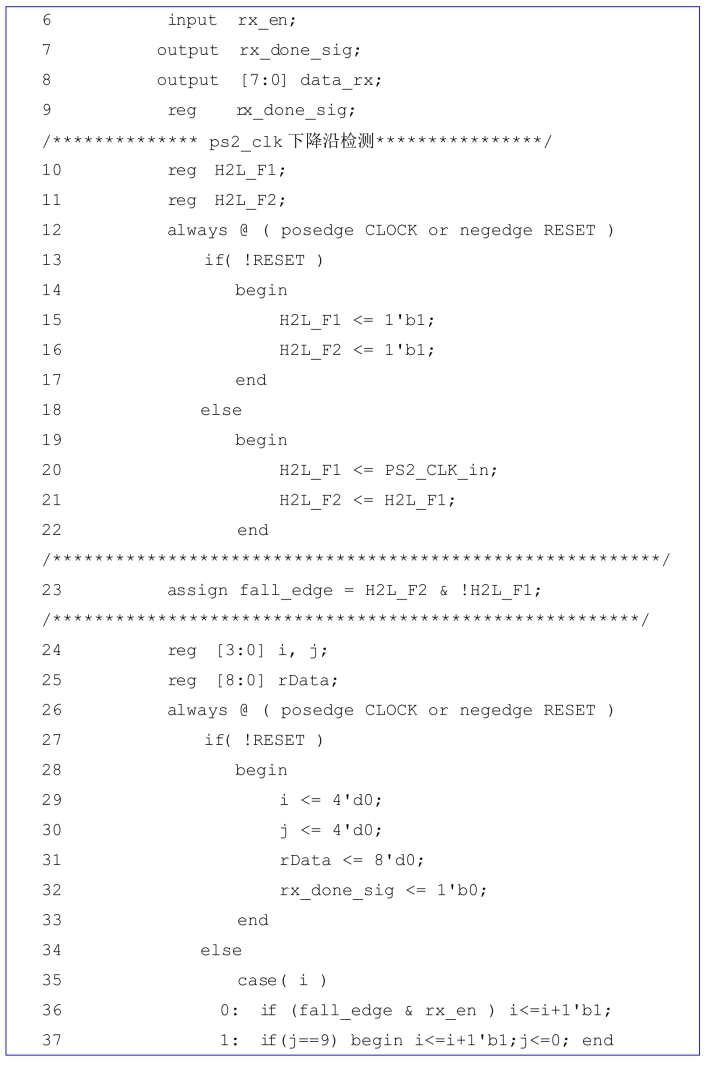

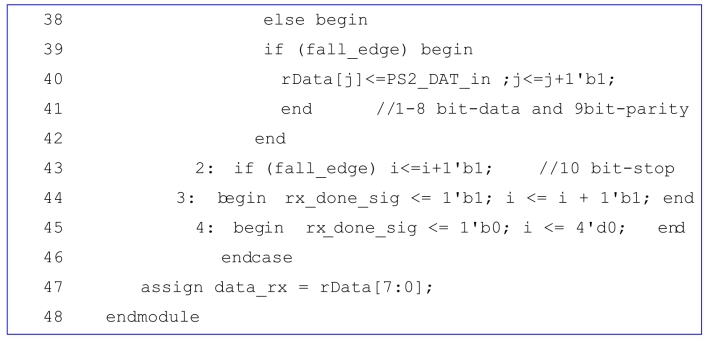

根据该时序,可以采用Verilog 设计实现PS/2 到主机的数据传输,如【代码5.12】所示。

【代码5.12】PS/2 鼠标接收模块设计

4. 主机到PS/2 鼠标的通信

首先,PS/2 设备总是产生时钟信号。如果主机要发送数据,它必须首先把时钟和数据线设置为“请求发送”状态,即通过下拉时钟线至少100 μs 来抑制通信;通过下拉数据线来应用“请求发送”,然后释放时钟。

PS/2 设备应该在不超过10 ms 的间隔内就要检查这个状态。当设备检测到这个状态,它将开始产生标记下的8 个数据位和1 个停止位的时钟脉冲。主机仅当时钟线为低的时候改变数据线,而数据在时钟脉冲的上升沿被锁存。这与发生在设备到主机的通信过程中正好相反。

在停止位发送后,设备要应答接收到的字节,就把数据线拉低并产生最后1 个时钟脉冲。如果主机在第11 个时钟脉冲后不释放数据线,设备将继续产生时钟脉冲,直到数据线被释放(然后设备将产生一个错误)。

主机可以在第11 个时钟脉冲(应答位)前中止一次传送,只要下拉时钟线至少100 μs。

要使得这个过程易于理解,主机必须按下面的步骤发送数据到PS/2 设备:

(1)把Clock 线拉低至少100 μs。

(2)把Data 线拉低。

(3)释放Clock 线。

(4)等待PS/2 设备把Clock 线拉低。

(5)设置/复位Data 线发送第一个数据位。

(6)等待PS/2 设备把时钟拉高。(https://www.xing528.com)

(7)等待PS/2 设备把时钟拉低。

(8)重复(5)~(7)步发送剩下的7 个数据位和校验位。

(9)释放Data 线,即发送停止位(1)。

(10)等待PS/2 设备把Clock 线拉高(此步可省略,因为下一步PS/2 设备还是会把Data 线拉低的)。

(11)等待PS/2 设备把Data 线拉低。

(12)等待PS/2 设备把Clock 线拉低。

(13)等待PS/2 设备释放Clock 线和Data 线。

图5.24 是单独的时序图,表示了由主机产生的信号及由PS/2 设备产生的信号。注意应答位时序的改变—数据改变发生在Clock 线为高的时候(不同于其他11 位是Clock 线为低的时候)。

图5.24 主机到设备通信时序

图5.24 描述了两个重要的定时条件:(a)和(b)。(a)从主机最初把Clock 线拉低,到PS/2 设备开始产生时钟脉冲(即Clock 线被PS/2 设备拉低),这段时间间隔必须不大于15 ms。(b)发送数据包(8 位数据位和校验位)总时间必须不大于2 ms。如果这两个条件不满足,主机将产生一个错误。在数据包收到后,主机为了处理数据应立刻把时钟线拉低来抑制通信。如果主机发送的命令要求有一个应答,这个应答必须在主机释放Clock 线后20 ms 之内被收到;如果没有收到,则主机产生一个错误。在设备到主机通信的情况中,时钟改变后的5 μs 内不应该发生数据改变的情况。

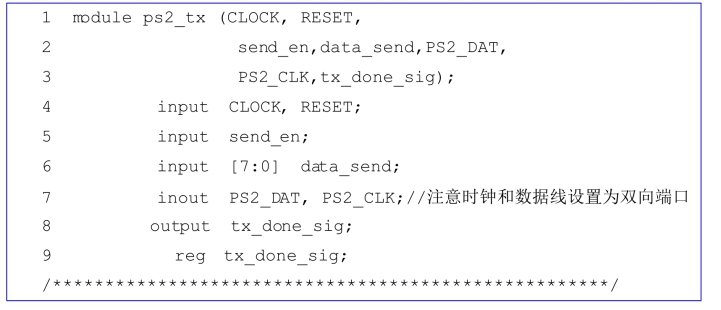

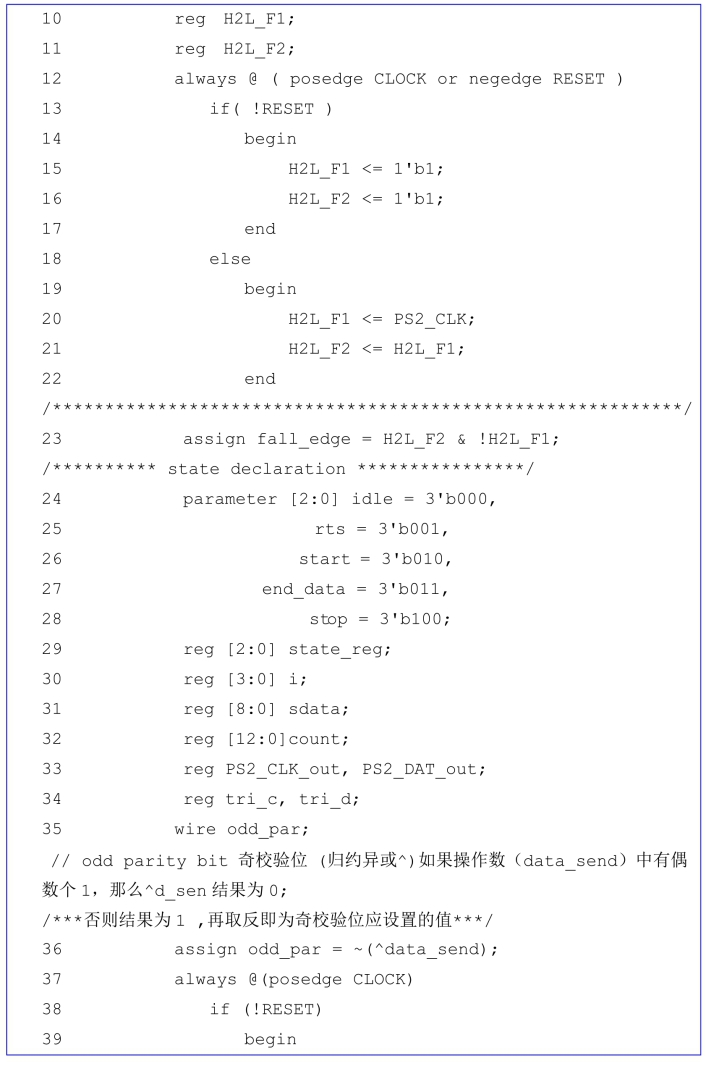

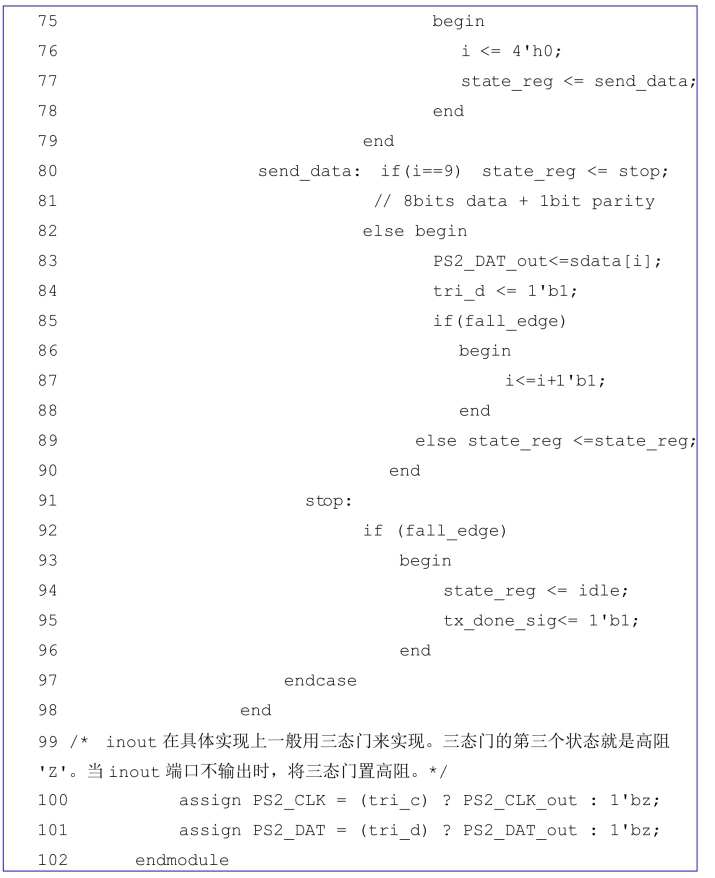

【代码5.13】实现了主机向PS/2 设备发送数据功能。

【代码5.13】PS/2 鼠标发送模块设计

PS/2 控制器必须进入主机发送请的状态。这可以通过以下动作实现:

(1)PS2_CLK 线首先被拉低至少在一个时钟周期(进入禁止传输Inhibit Transmission状态)。

(2)PS2_DATA 线随后被拉低(提供的起始位帧传送)。

(3)PS2CLK 线随后被释放(仍然保持PS2DATA 低)。

(4)PS/2 设备定期检查数据和时钟线是否为这种状态,当检测到,鼠标开始产生“PS2_CLK”信号,以便主机发送数据。

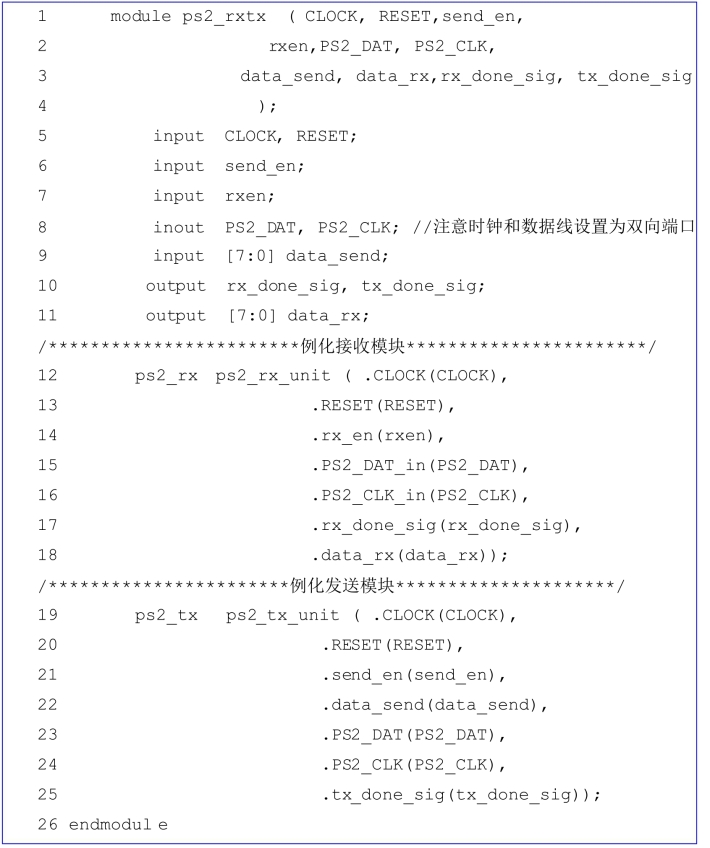

5. PS/2 鼠标双向通信模块设计

在完成了【代码5.12】和【代码5.13】的接收和发送模块设计后,为了方便实现PS/2鼠标的灵活应用,往往还需要设计一个双向的通信模块,该模块其实就是上述两个模块的组合调用而已,如【代码5.14】所示。

【代码5.14】PS/2 双向通信模块设计

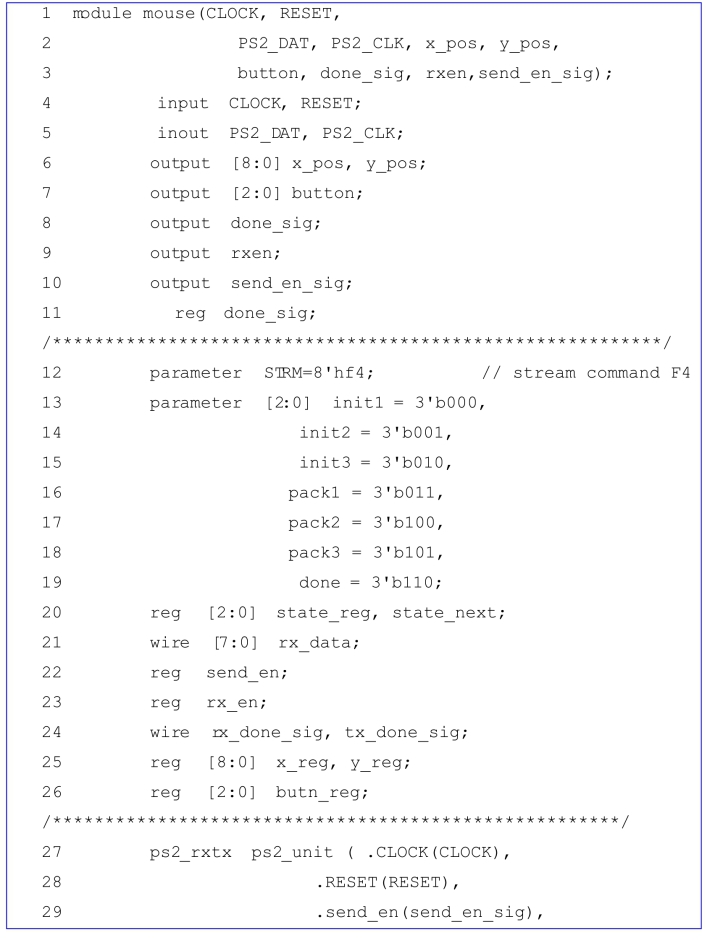

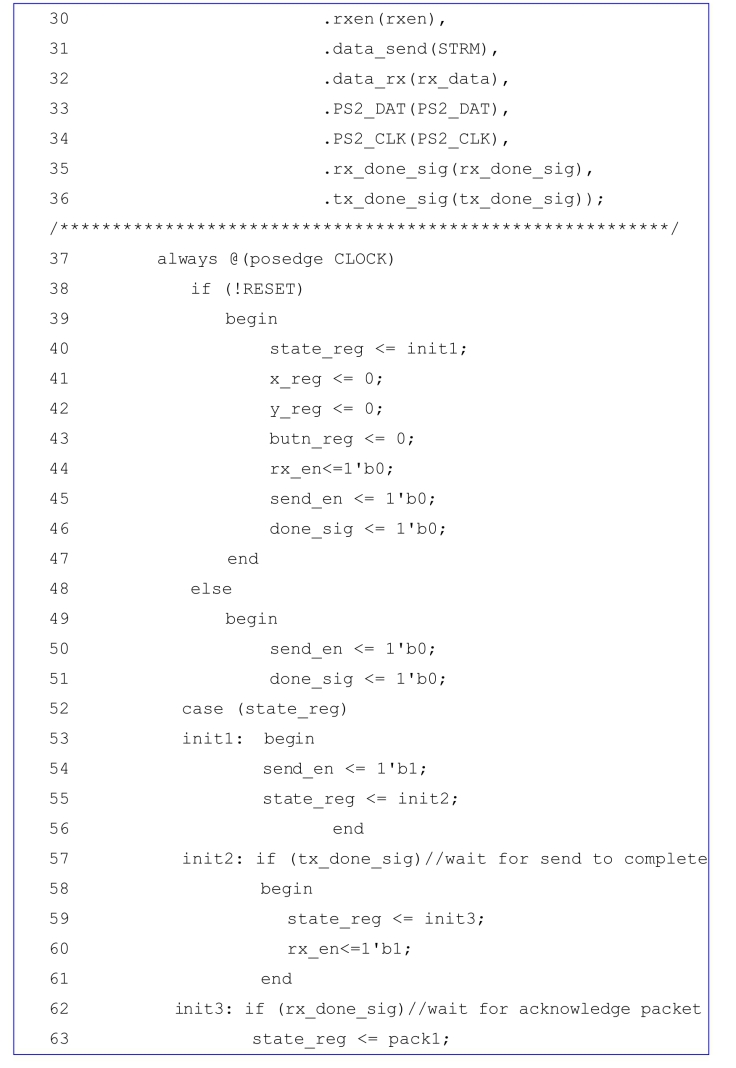

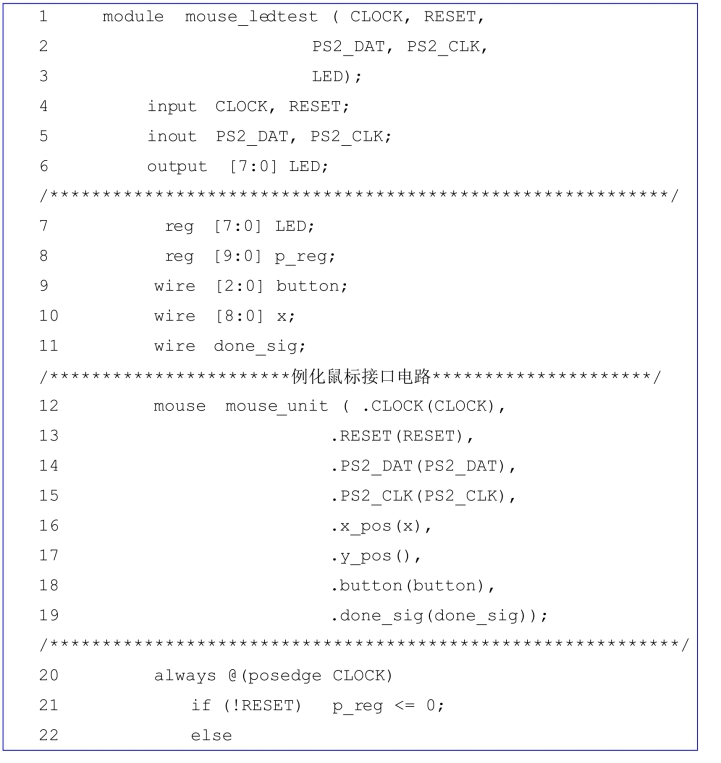

6. PS/2 鼠标接口电路模块设计

根据PS/2 鼠标的通信协议,在分别完成了发送和接收模块时序控制电路设计后,对于PS/2 鼠标的典型接口电路设计如【代码5.15】所示。

【代码5.15】PS/2 鼠标接口电路模块设计

在【代码5.15】中,第12 行定义了0xF4 使能数据报告并复位命令,鼠标用“应答”(OxFA)回应命令;标准的鼠标有两个计数器保持位移的跟踪:X 位移计数器和Y 位移计数器。可存放9 位的二进制补码,并且每个计数器都有相关的溢出标志。它们的内容连同3 个鼠标按钮的状态一起以3 字节移动数据包的形式发送给主机。位移计数器表示从最后一次位移数据包被送往主机后有位移量发生。位移计数器是一个9 位2 的补码整数。它的最高位作为符号位出现在位移数据包的第一个字节里。

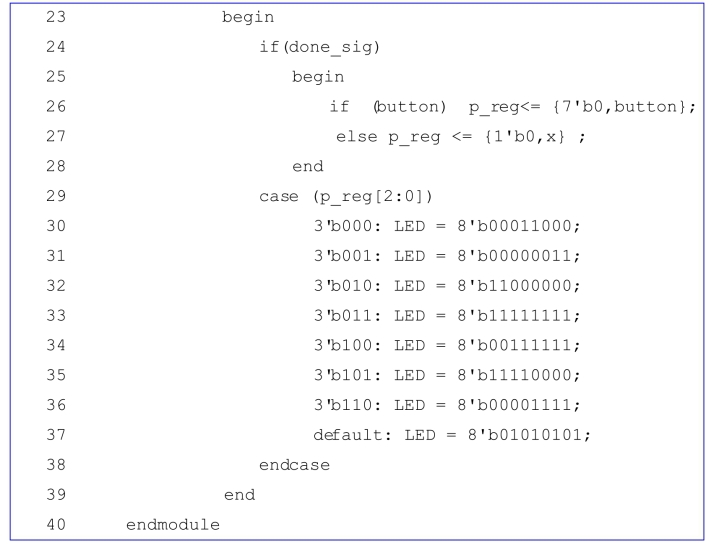

7. PS/2 鼠标应用示例

在完成了标准PS/2 鼠标接口电路设计后,就能对处于工作状态的鼠标加以应用,通过读取相应数据,进而判断鼠标是否有键按下,是否发生位移的情况,以在实际的项目应用中,轻松实现鼠标控制功能。

本示例是根据上述鼠标各个功能单元模块,完成的一个简单测试代码设计,主要功能是通过鼠标的按键来控制实验开发平台上的LED 发光二极管的亮灭状态,进而验证PS/2 鼠标控制电路设计的正确性,如【代码5.16】所示。

【代码5.16】PS/2 鼠标控制LED 测试设计

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。