为了验证刚刚定制的分频器IP 核功能是否正确,能否成功添加进入Vivado IP 核资源库目录,下面以一个简单调用分频器IP 的应用实例,证明用户自定义IP 核真实有效。

1. 设计任务

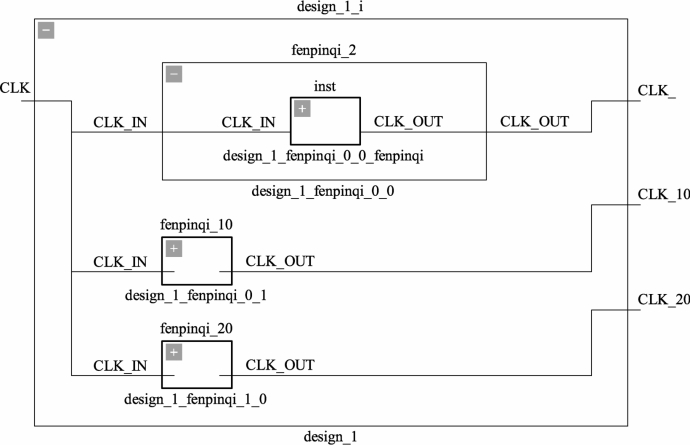

本示例的主要任务是基于IP 核设计思想,完成对一个基准时钟信号CLK,分频输出3 个不同频率信号,其中分频比分别为2、10 和20,任务如图4.72 所示。

设计思路是调用【代码4.10】生成的IP 核,通过修改R 参数值,即可实现相应分频系数的信号输出。

图4.72 设计任务框图

2. 实现过程

(1)新建工程。

打开Vivado 软件,新建一个名为“fenpinqi_call”的工程,单击“Next”,在器件型号选择界面选中“xc7z020clg484-1”的FPGA,完成工程建立。

(2)设置调用自定义IP 核路径。

Vivado IP 核资源管理器中默认只包含了软件自带的IP 库,用户自定义的IP 库需要添加路径设置,才能在IP Catalog 目录中查询调用。

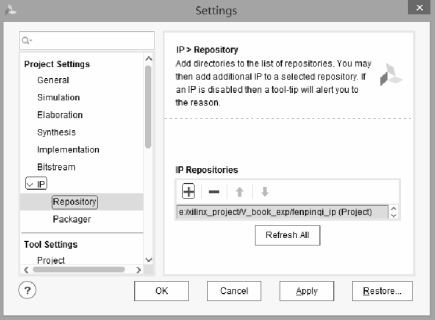

在 Vivado 左侧的“Flow Navigator”项目设计流程管理窗口,单击【PROJECT MANAGER】→【Settings】,弹出工程属性设置对话框,如图4.73 所示。单击【Project Settings】→【IP】→【Repository】,进入IP 资源库添加对话框,通过添加IP 核所在目录(一个路径),就能添加IP 目录到存储库列表中。

图4.73 “Settings”工程属性设置对话框

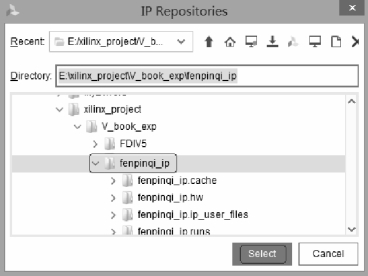

在图4.73 中单击窗口中部的 按钮,弹出“IP Repositories”添加(add)路径选择对话框,如图4.74 所示。找到已定制的IP 核存放路径,此处分频器IP 核工程路径为“E:\xilinx_project\V_book_exp\fenpinqi_ip”,选中工程文件夹名“fenpinqi_ip”即可,然后单击“Select”,弹出“Add Repository”对话框,如图4.75 所示。

按钮,弹出“IP Repositories”添加(add)路径选择对话框,如图4.74 所示。找到已定制的IP 核存放路径,此处分频器IP 核工程路径为“E:\xilinx_project\V_book_exp\fenpinqi_ip”,选中工程文件夹名“fenpinqi_ip”即可,然后单击“Select”,弹出“Add Repository”对话框,如图4.75 所示。

图4.74 指定IP 核所在工程路径

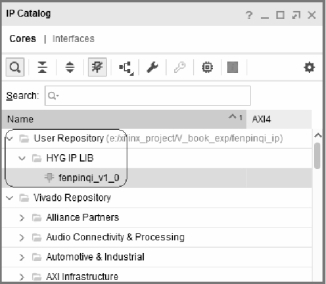

在图4.75 中,如果指定路径中包含已定义的IP,此时会自动显示出来,如图中显示指定路径中包含1 个IP 核,名称是“fenpinqi_v1_0”,说明路径设置正确。单击“OK”,完成路径添加,结果如图4.73 所示,然后单击“OK”。

此时,在Vivado 左侧的“Flow Navigator”项目设计流程管理窗口,单击【PROJECT MANAGER】→【IP Catalog】,弹出IP 资源管理器窗口,在库列表中除了Vivado Repository IP 资源外,自动显示添加成功的自定义IP 目录“User Repository”→“HYG_IP_LIB”→“fenpinqi_v1_0”,如图4.76 所示,表明自定义IP 核成功添加到Vivado IP 核管理器中。

图4.75 Add Repository 提示对话框

(3)创建Block 设计文件。

此处采用图形设计方法,调用分频器IP 核,完成设计任务。

执行【IP INTEGRATOR】→【Create Block Design】选项,可采用默认文件名(design_1)创建图形设计文件。

图4.76 自定义IP 核目录添加成功

(4)调用3 个分频器IP 核。

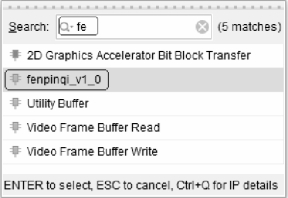

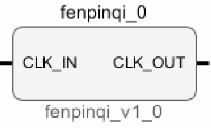

在Diagram 图形编辑窗口中单击工具栏中 按钮,打开IP 核资源库管理器,在“Search”查询对话框中,输入“fenpinqi”或“fe”时,在列表中就会显示“fenpinqi_v1_0”,如图4.77 所示,双击添加到原理图设计文件中,其元件外观如图4.78 所示。

按钮,打开IP 核资源库管理器,在“Search”查询对话框中,输入“fenpinqi”或“fe”时,在列表中就会显示“fenpinqi_v1_0”,如图4.77 所示,双击添加到原理图设计文件中,其元件外观如图4.78 所示。

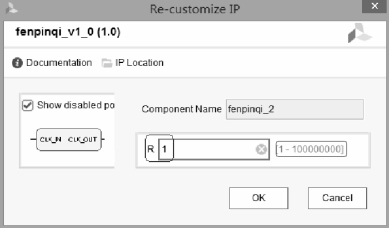

双击调出的“fenpinqi_v1_0”IP 核元件符号,弹出如图4.79 所示的对话框,进行参数设置。

在该对话框中,不难发现,只有一个参数R 需要设置,其取值范围1~100 000 000正是在定义IP 核时设定的,根据分频器定义源文件中R 参数代表的是分频比系数的一半,默认值为1,即实现分频系数为2 倍分频,刚好满足设计任务中的一个信号输出。因此,这个IP 核参数保持默认即可,单击“OK”,完成IP 核参数设置。

图4.77 调用“fenpinqi_v1_0”IP 核

图4.78 分频器IP 元件

(https://www.xing528.com)

(https://www.xing528.com)

图4.79 分频器IP 核参数设置对话框

如法炮制,重复再调用2 个分频器IP 核,分别设置R 取值为5 和10,即完成10 倍分频和20 倍分频。在原理图中,也可以采用复制粘贴的方法完成对同一个IP 元件的重复调用。

(5)绘制原理图。

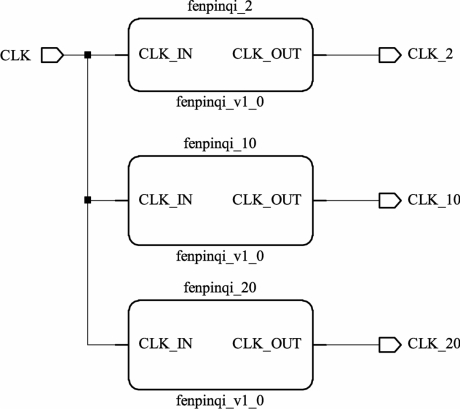

根据设计任务框图,采用原理图绘制导线、添加端口和更改端口名的方法,完成如图4.80 所示效果的原理图绘制。其中,CLK 是基准时钟输入端口;CLK_2 代表是2 分频输出端口;CLK_10 代表是10 倍分频输出端口;CLK_20 代表是20 倍分频输出端口;3个分频器IP 核的元件名依次更改为“fenpinqi_2”“fenpinqi_10”和“fenpinqi_20”,保存文件并做有效性检测。

(6)生成设计输出文件。

在Vivado 设计界面的BLOCK DESIGN 窗口中,右键单击【Sources】→【Design Sources】→“design_1”文件,弹出浮动菜单,执行“Generate Output Products…”,在弹出的“Generate Output Products”对话框中,单击“Generate”,在弹出的生成结果信息提示框中,单击“OK”。

图4.80 顶层设计原理图

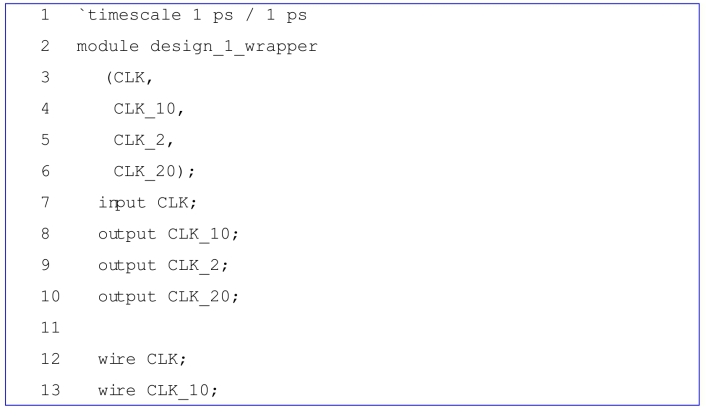

(7)生成“design_1_wrapper.v”顶层文件。

再次右键单击【Sources】→【Design Sources】→“design_1”文件,弹出浮动菜单,执行“Create HDL Wrapper…”选项,在弹出的“Create HDL Wrapper”对话框中,选择“Let Vivado manage wrapper and auto-update”,保持默认设置,单击“OK”。

此时,在工程设计源文件目录中,生成了“design_1_wrapper.v”,见【代码4.11】。

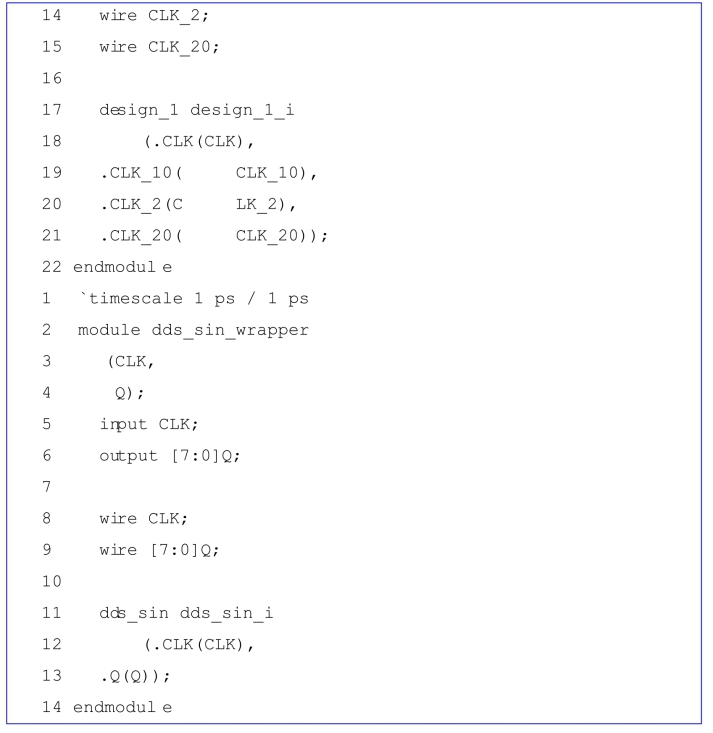

【代码4.11】design_1_wrapper.v

(8)设计综合。

在Vivado 左侧的“Flow Navigator”项目设计流程管理窗口,找到【SYNTHESIS】→【Run Synthesis】并单击,或在工具栏上单击 图标,在下拉菜单中选择【Run Synthesis】,启动运行设计综合。

图标,在下拉菜单中选择【Run Synthesis】,启动运行设计综合。

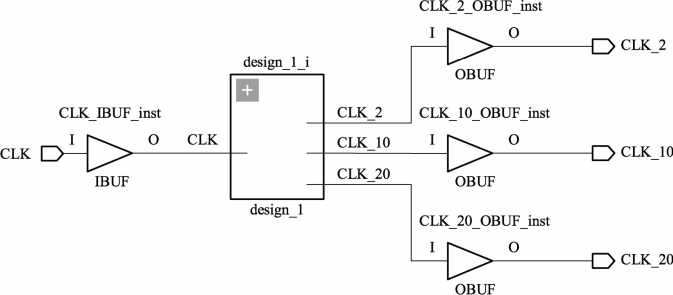

综合完成后单击【RTL ANALYSIS】→【Open Elaborated Design】→【Schematic】,打开“Schematic”网表结构如图4.81 所示。

在图4.81 中,主要是由“design_1_i”元件和输入、输出缓冲器构成。其中,“design_1_i”元件符号上有 号,可以将鼠标移动到

号,可以将鼠标移动到 号上,此时将会变为双箭头,表示此元件可以展开,查看调用底层设计结构情况,单击

号上,此时将会变为双箭头,表示此元件可以展开,查看调用底层设计结构情况,单击 号后弹出如图4.82 所示的“design_1_i”模块内部结构。

号后弹出如图4.82 所示的“design_1_i”模块内部结构。

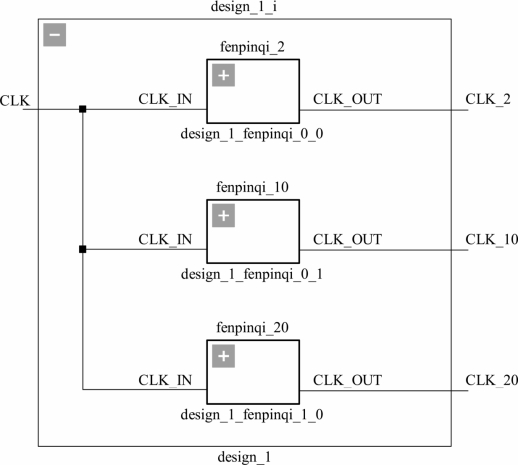

在图4.82 中可看出,“design_1_i”模块由3 个IP 核构成,同理,每一个IP 核元件符号左上角都有 号,说明都可以单击鼠标再次展开,进一步观看IP 核的内部结构,单击展开其中的“fenpinqi_2”元件,会出现如图4.83 所示的电路结构。

号,说明都可以单击鼠标再次展开,进一步观看IP 核的内部结构,单击展开其中的“fenpinqi_2”元件,会出现如图4.83 所示的电路结构。

图4.81 顶层设计RTL 网表结构

图4.82 design_1_i 模块内部结构

图4.83 展开“fenpinqi_2”的电路结构

同理,在“fenpinqi_2”内部的“inst”元件还可以继续查看最底层电路结构,这充分体现了基于Verilog HDL 是自顶向下的设计思想。

(9)仿真测试。

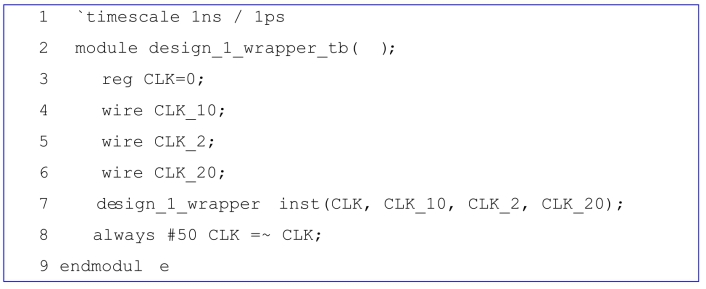

参考【代码4.12】编写Testbench 激励代码,对刚刚生成的“design_1_wrapper.v”进行测试。

【代码4.12】design_1_wrapper.v 仿真测试代码

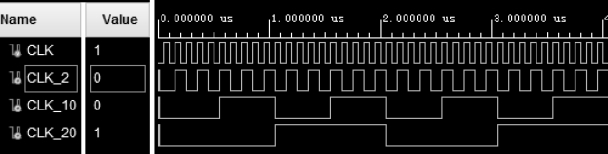

保存仿真测试文件,单击工程管理器界面的【SIMULATION】→【Run Simulation】→【Run Behavioral Simultaion】,启动行为仿真,仿真结果如图4.84 所示。

图4.84 仿真波形

从仿真波形中可以看出,分别输出了基准时钟2 分频、10 分频和20 分频的3 个不同频率信号,说明IP 核设计正确,能被正确调用,实现相应功能。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。