1. 设计任务

采用DDS 直接数字频率合成技术原理,通过调用存储器ROM 和二进制计数器IP 核,完成一个简易正弦信号发生器电路设计,并通过编写仿真测试文件,观察输出波形,看到光滑的正弦波信号。

2. 设计原理

(1)DDS 技术简介。

直接数字频率合成器(Direct Digital Synthesis/Direct Digital Frequency Synthesis,DDS/DDFS)是1971 年由J.Tierney 等人提出的一种全新全数字式频率合成技术,也是一种先进的波形产生技术,它直接从相位的概念出发进行频率合成,得到所需的任意波形。

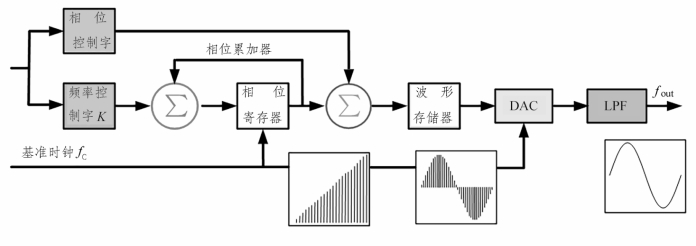

DDS 基本结构主要由相位累加器、波形存储器(相位幅度转换)、数模转换器(D/A)、低通滤波器(LPF)构成,如图4.36 所示。其中,相位累加器由N 位加法器与N 位累加寄存器级联构成。

DDS 信号发生器的基本原理是建立在采样定理的基础上,首先对需要产生的波形进行采样,将采样值数字化后存入存储器作为查找表,然后再通过查找表将数据读出,经过D/A 转换器转换成模拟量,把存入的波形重新合成出来。时钟频率给定后,输出信号的频率取决于频率控制字,频率分辨率取决于累加器位数,相位分辨率取决于ROM 的地址线位数,幅度量化噪声取决于ROM 的数据位字长和D/A 转换器位数。

图4.36 DDS 基本结构

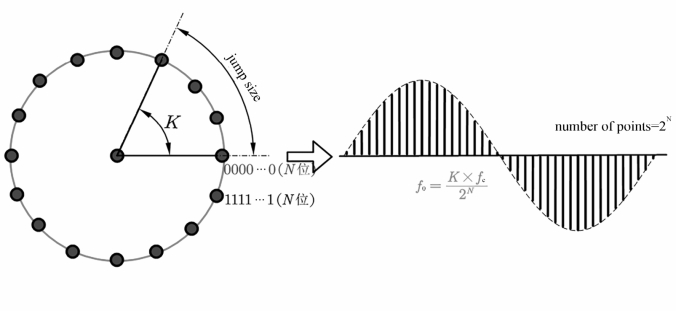

相位累加器原理:一个正弦波,虽然它的幅度不是线性的,但是它的相位却是线性增加的。DDS 正是利用了这一特点来产生正弦信号。根据DDS 相位累加器的位数N,把360°平均分成了2N 等份,如图4.37 所示。

图4.37 相位累加器原理

假设系统时钟为 f c,输出频率为 f o。每次转动一个角度360 °/2N,则可以产生一个频率为 fc /2N的正弦波的相位递增量,即为DDS 的频率分辨率。那么只要选择恰当的频率控制字K,使得 f o/fc=K/2N ,就可以得到所需要的输出频率 fo= f c·K/2N。

相位累加器由N 位加法器与N 位累加寄存器级联构成。每来一个时钟脉冲 fc ,加法器将频率控制字K 与累加寄存器输出的累加相位数据相加,把相加后的结果送至累加寄存器的数据输入端。累加寄存器将加法器在上一个时钟脉冲作用后,所产生的新相位数据反馈到加法器的输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字K相加。这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。由此可以看出,相位累加器在每一个时钟脉冲输入时,把频率控制字累加一次,相位累加器输出的数据就是合成信号的相位,相位累加器的溢出频率就是DDS 输出的信号频率。

DDS 信号发生器的优点:

① 频率分辨率高、输出频点多、可达2N 个频点(N 为相位累加器位数)。

② 频率切换速度快,DDS 是一个开环系统,无任何反馈环节,因而频率转换时间极短,可达纳秒量级。

③ 频率切换时相位连续。

④ 可以输出宽带正交信号。

⑤ 输出相位噪声低,对参考频率源的相位噪声有改善作用。

⑥ 可以产生任意波形。

⑦ 全数字化实现、便于集成、体积小、质量小。

(2)正弦信号发生器设计方案。

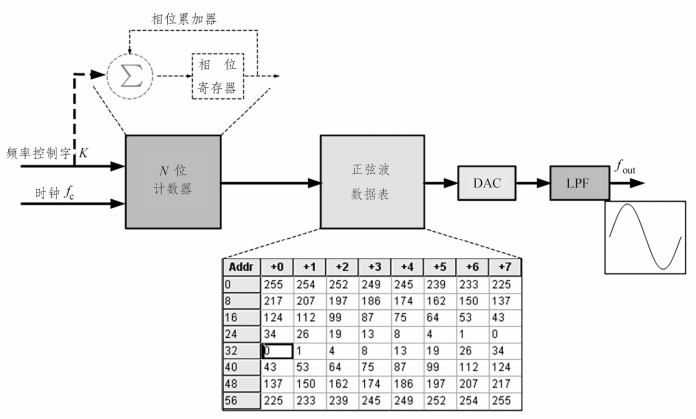

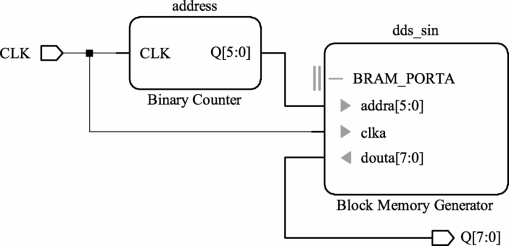

根据DDS 工作原理,正弦信号发生器原理如图4.38 所示,相位累加器的功能其实与计数器的功能相同,可用N 位计数器实现,即由累加器和寄存器实现;波形存储器单元可由ROM 存储器存放正弦波采样值数据实现。

图4.38 DDS 正弦信号发生器原理框图

用计数器输出的数据作为波形存储器(ROM)的相位取样地址,这样就可把存储在波形存储器内的正弦波波形采样幅度数值经查找表查出,完成相位到幅值转换。波形存储器的输出送到D/A 转换器,D/A 转换器将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号。低通滤波器用于滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。

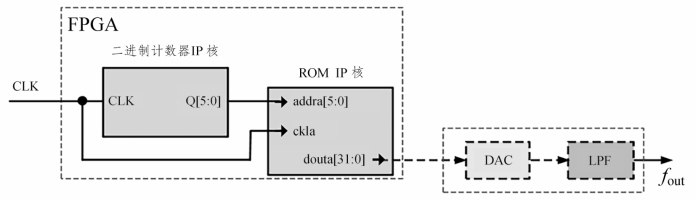

为此,整个项目的设计完全可以使用系统自带的二进制计数器IP 核实现相位累加器功能(此处为简化功能,频率控制字K 默认为1);使用ROM 存储器IP 核实现波形数据存储功能,DAC 部分电路也可不用设计,直接采用Vivado 的仿真功能,观看设计波形结果,设计实现方案如图4.39 所示。

图4.39 DDS 正弦信号发生器实现方案

3. COE 文件创建方法(ROM 初始化文件)

(1)COE 文件简介。

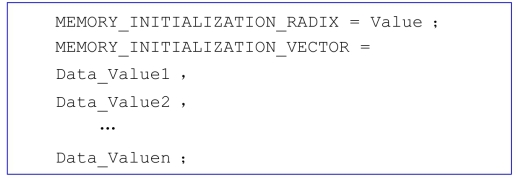

在调用存储器类IP 核进行配置时,往往需要对存储器进行初始化,以加载指定数据内容到存储器中。Vivado 中对ROM 类存储器IP 核进行初始化的文件格式是“.coe”(Coefficient)文件(ALTERA Quartus II 中存储器初始化文件是“.mif”),其基本格式如下:

COE 文件是一种ASCII 文本文件,其中,“MEMORY_INITIALIZATION_RADIX”是关键词,定义存储器初始化值的基数,等号后面的“Value”表示文件存储数据的进制,可以设置为 2(二进制)、10(十进制)或 16(十六进制),以分号结束;“MEMORY_INITIALIZATION_VECTOR”是关键词,定义块存储器与分布式存储器的数据(数据向量),等号后面的“Data_Value1…Data_Valuen”的数字就是数据向量,每个数据占一行,用逗号隔开,最后一个数字以分号结束。.coe 文件的前两行的开头格式是固定的,不能改变。

(2)COE 文件的创建方法。

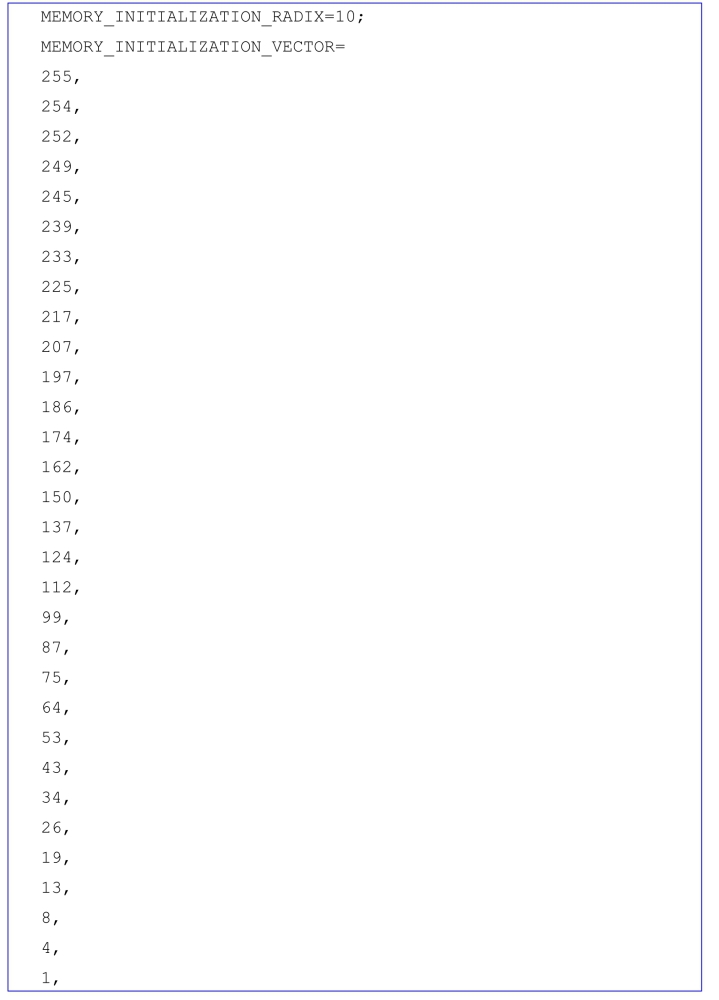

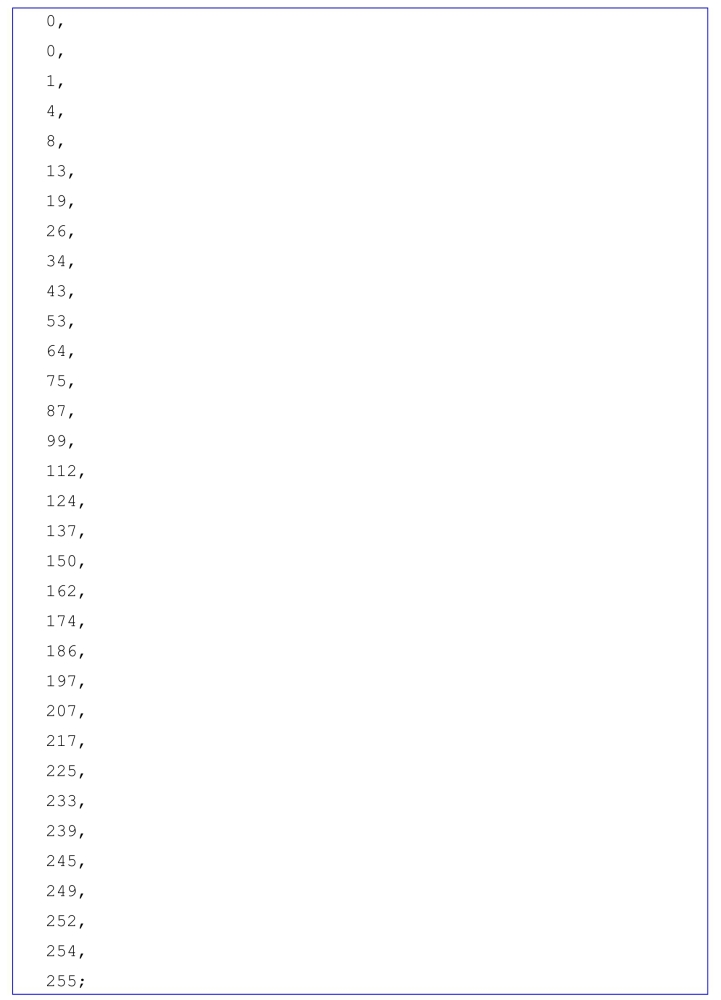

COE 文件的创建方法可以在写字板、记事本等文本编辑器中按照上述格式编辑,保存后缀为“.coe”即可。例如,此项目中需要构建正弦波的数据存储模块(此处以64 点数据采样),则需要将正弦波采样数据值编辑为“.coe”文件,其方法是打开写字板,输入【代码4.6】,保存为“sin64.coe”。其中,数据格式采用十进制,一共64 个数据,最大数据为255(8 位二进制)。

【代码4.6】sin64.coe 正弦波采样值(64 点)COE 文件

上述文件中的正弦波采样数据值可以通过编写C 语言代码或在MATLAB 软件中直接生成,如【代码4.7】所示。

【代码4.7】MATLAB 生成正弦波采样数据代码

对MATLAB 生成的“.txt”文件用文本编辑软件打开,进行下面的处理,就能创建COE 文件。

① 在文件最开始添加两行关键字内容:

memory_initialization_radix=10;

memory_initialization_vector=

② 把每一行的空格用文本替换功能换成“,”,并在最后一行添加一个“;”。

③ 将“.txt”文件后缀修改为“.coe”,保存文件并退出。

对于波形数据还可以用其他专用工具软件生成,如Guagle_wave,它可以生成正弦波、三角波、锯齿波和任意波形采样数据。对于今后可能会用到的图像数据,也可以使用相关软件工具生成,然后再将其转化为符合COE 格式的文件。

4. 设计实现过程

根据图4.39 的设计实现方案,DDS 正弦信号发生器设计实现过程主要是完成两个底层模块和一个顶层设计文件,即存储正弦数据ROM、计数器和DDS 顶层设计文件。

IP 核调用可以使用文本方式例化,也可以采用Block 原理图设计实现,在此以原理图设计方法详细介绍实现过程。

(1)新建工程。

新建一个名为“dds_sin_block”,FPGA 型号为“xc7z020clg484-1”的工程。

(2)创建Block 设计文件。

执行【IP INTEGRATOR】→【Create Block Design】选项,创建名为“dds_sin”的图形设计文件。

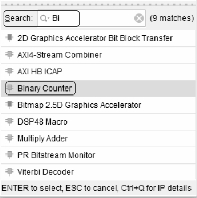

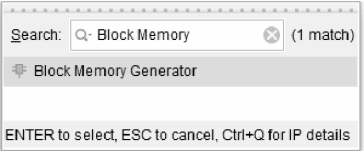

(3)添加“Binary Counter IP”核。

在Diagram 图形编辑窗口中单击工具栏中 按钮,打开IP 核资源库管理器,在“Search”查询对话框中,完整输入“Binary Counter”或输入“Bi”时,在列表中已经出现“Binary Counter”,如图4.40 所示,双击添加到原理图设计文件中。

按钮,打开IP 核资源库管理器,在“Search”查询对话框中,完整输入“Binary Counter”或输入“Bi”时,在列表中已经出现“Binary Counter”,如图4.40 所示,双击添加到原理图设计文件中。

图4.40 查找“Binary Counter”IP 核

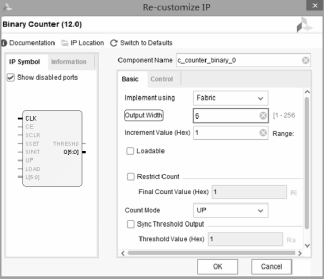

双击调出的“Binary Counter”IP 核元件符号,进行参数设置。根据正弦信号发生器设计方案,因为对输出信号频率无精度及可调控制要求,所以相位累加器位宽只要大于存储器中数据地址线位宽即可。同时根据存储器中数据深度为64,对应地址位宽为6 位,所以计数器的数据输出位宽大于等于6,此处设置为6,其他保持默认,如图4.41 所示单击“OK”。

图4.41 “Binary Counter”参数设置

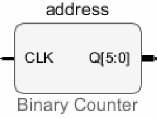

添加“Binary Counter IP”核定义的6 位二进制计数器结果如图4.42 所示,此时可以将计数器模块名字进行重命名,选择元件,在左侧的参数修改对话框中输入“address”,如图4.44 所示,最后计数器元件名字重命名的效果如图4.43 所示。

图4.42 计数器元件 (https://www.xing528.com)

图4.43 更名后的计数器元件

图4.44 重命名

(4)添加ROM 存储器IP 核。

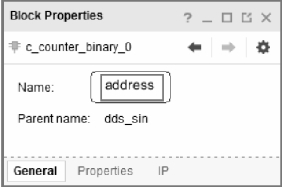

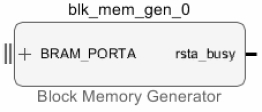

在Diagram 图形编辑窗口中单击工具栏中 按钮,打开IP 核资源库管理器,在“Search”查询对话框中,输入“Block Memory Generator”,在列表中将显示“Block Memory Generator”IP 核(见图4.45),双击添加到原理图设计文件中,元件符号如图4.46 所示。

按钮,打开IP 核资源库管理器,在“Search”查询对话框中,输入“Block Memory Generator”,在列表中将显示“Block Memory Generator”IP 核(见图4.45),双击添加到原理图设计文件中,元件符号如图4.46 所示。

图4.45 调用Block Memory GeneratorIP 核

图4.46 存储器元件符号

双击图4.46 中存储器元件符号,进行参数设置,弹出如图4.47 所示的参数修改对话框,存储器IP 核通常有“Basic”“PortA Options”“Other Options”3 个选项卡内容需要设置。

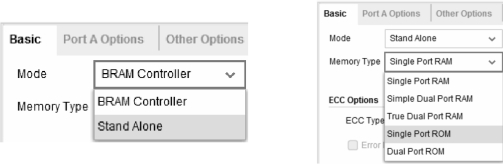

① Basic 选项卡。

Mode 选项:包含“BRAM Controller”和“Stand Alone”两种模式,此处选择“Stand Alone”。

Memory Type 选项:在“Stand Alone”模式下一共有5 种类型的存储器,如可以定义为单端口ROM、双端口ROM 或单端口RAM 等。此处我们需要定义的是单端口ROM,因此存储器类型设置为“Single Port ROM”,如图4.48 所示,其他保持默认即可。

图4.47 “Block Memory Generator”参数设置对话框

图4.48 “Basic”选项卡参数设置

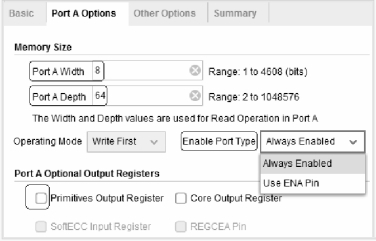

② Port A Options 选项卡。

Memory Size 选项:主要设置存储器大小,包含端口数据位宽,因为“.coe”存储器初始化文件中正弦波形数据采样值最大值为255,因此数据位宽为8 位二进制,此处“Port A Width”设置为8;“Port A Depth”表示存储深度,即存储数据单元个数,该参数决定存储器的地址位宽,因正弦波形采样为64 点,故需要存储64 个数据,与“.coe”文件中的数据格式对应,所以“Port A Depth”设置为64;“Enable Port Type”设置为“Always Enabled”。

Port A Optional Output Registers 选项卡:去掉“Primitives Output Register”前面复选框中的“√”,其他保持默认,如图4.49 所示。

图4.49 “Port A Options”选项卡参数设置

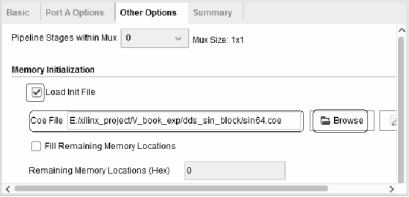

③ Other Options 选项卡。

Memory Initialization 选项:存储器初始化参数设置。将“Load Init File”前复选框选中打“√”,表示加载ROM 初始化数据文件,通过单击“Browse”,找到之前定义好的“.coe”初始化文件,将数据加载进ROM 中,其他保持默认,如图4.50 所示。

图4.50 加载ROM 初始化“.coe”文件

COE 文件提供了一种设置内存初始化值的高层次方法,但实际上并不能直接使用。当生成IP 核时,Vivado 会将COE 文件转换为MIF 文件。MIF 文件保存了原始值,用于存储类IP 核的初始化和仿真模型。

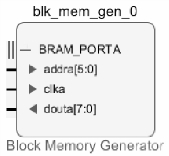

完成上述参数设置后单击“OK”,返回原理图设计文件,进行图形绘制。把鼠标移到ROM 元件的端口“+ BRAM_PORTA”上,鼠标会变为如图4.51 所示的向下箭头状,表示此端口是一个可以展开的端口,此时单击鼠标左键,会将此端口包含的所有端口展开,结果如图4.52 所示,这样就可以进行图形绘制了。

图4.51 展开ROM 端口

图4.52 ROM 端口展示

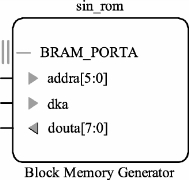

选择ROM 元件符号,在左侧的参数修改对话框中更改元件名为“sin_rom”(见图4.53),更改后的元件如图4.54 所示。

图4.53 更改ROM 元件名对话框

图4.54 “sin_rom”元件效果

(5)绘制原理图。

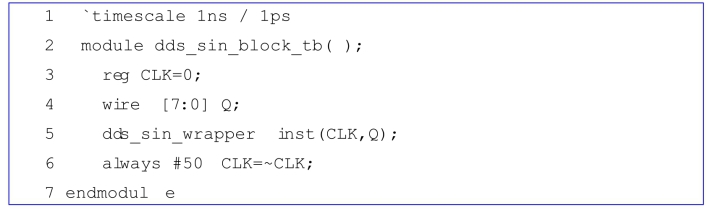

根据DDS 正弦信号发生器设计方案,采用原理图绘制导线、添加端口和更改端口名的方法,完成如图4.55 所示效果的原理图绘制,保存文件并做有效性检测。

图4.55 DDS 正弦信号发生器顶层设计原理图

(6)生成设计输出文件。

在Vivado 设计界面的“BLOCK DESIGN”窗口中,右键单击【Sources】→【Design Sources】→“dds_sin”文件,弹出浮动菜单,执行“Generate Output Products…”,在弹出的“Generate Output Products”对话框中,单击“Generate”,在弹出的生成结果信息提示框中,单击“OK”。

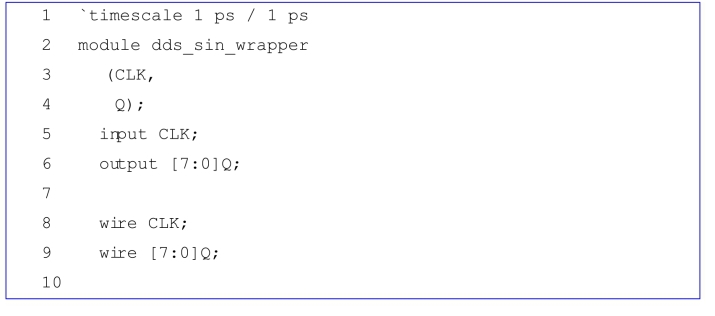

(7)生成“dds_sin_wrapper.v”顶层文件。

再次右键单击【Sources】→【Design Sources】→“dds_sin”文件,弹出浮动菜单,执行“Create HDL Wrapper…”选项,在弹出的“Create HDL Wrapper”对话框中,选择“Let Vivado manage wrapper and auto-update”,保持默认设置,单击“OK”。

此时,在工程设计源文件目录中,生成了“dds_sin_wrapper.v”,见【代码4.8】。

【代码4.8】dds_sin_wrapper.v

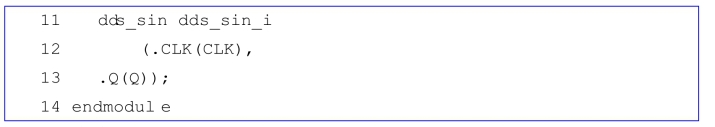

(8)仿真测试。

参考【代码4.9】编写Testbench 激励代码,对刚刚生成的dds_sin_wrapper.v 进行测试。

【代码4.9】DDS 正弦信号发生器仿真测试代码

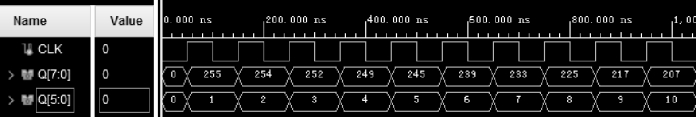

保存仿真测试文件,单击工程管理器界面的【SIMULATION】→【Run Simulation】→【Run Behavioral Simultaion】,启动行为仿真,仿真结果如图4.56 所示。

图4.56 正弦信号发生器仿真波形

从仿真波形可以看出随着计数器不断累加,把ROM 中的存储数据有序地读取出来,证明设计是正确的。

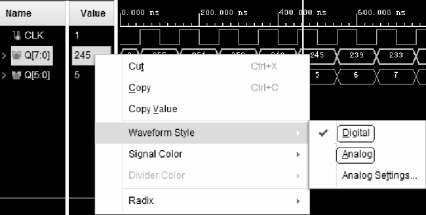

为了更加直观地看到正弦波效果,在Vivado 中仿真器波形观察界面,允许对波形显示数据格式进行数字和模拟的切换。选中输出端Q[7:0],单击右键弹出浮动菜单,如图4.57 所示。

图4.57 设置波形模拟显示格式

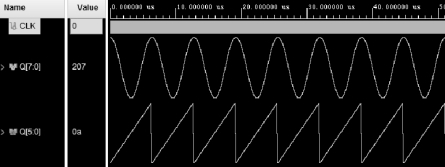

选择“Waveform Style”展开“Digital”“Analog”选项,默认是“Digital”类型,这里选择“Analog”,将数据已模拟信号方式显示。此时,输出端波形发生了变化,出现了线条显示,再通过波形工具栏的![]() 缩放按钮,调节视图比例,一条光滑的正弦波形产生,如图4.58 所示。

缩放按钮,调节视图比例,一条光滑的正弦波形产生,如图4.58 所示。

至此,完成了DDS 正弦信号发生器设计。

图4.58 仿真结果正弦波

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。