1. 设计任务

序列检测器的主要功能是能够实现对一组或多组由二进制码组成的脉冲序列信号进行识别,完成检测与比对。当序列检测器连续收到一组串行二进制码后,如果这组码与检测器中预置的码相同,则输出“1”,否则输出“0”。这种检测的工作过程是将输入的串行二进制码与预置数(密码)对应位的码字进行比对,只有当比对结果相同后,才进行下一位的连续比对,只要有任何一位不相等,都将返回第一个码字处重新开始检测。

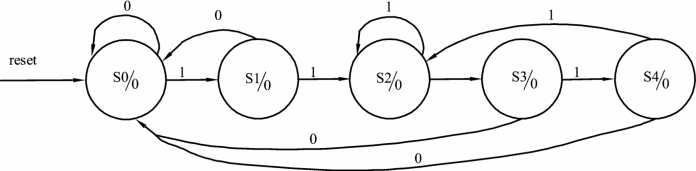

此项目的任务是设计一个可以检测“1101”序列的电路,当输入的一串连续的序列数高位在前串行进入检测器后,如此数与预置的“1101”相同,则输出“1”,否则输出“0”。其运行原理如图3.57 所示。

图3.57 序列检测器状态转移图

该序列检测器整个过程包含5 个状态,分别是图中的S0~S4,其对应的功能含义如下:

(1)状态S0:初始状态,如果输入为“1”,则状态迁移到S1;否则,继续等待接收序列的输入起始有效位(此时表示接收到“1”),系统输出为“0”。

(2)状态S1:如果输入为“0”,则必须返回状态S0;否则,迁移到状态S2(此时表示已经接收到“11”),系统输出为“0”。

(3)状态S2:如果输入为“1”,则停留在状态S2;否则,迁移到状态S3(此时表示已经接收到“110”),系统输出为“0”。

(4)状态S3:如果输入为“0”,则必须返回状态S0;否则,迁移到状态S4(此时表示已经接收到“1101”),系统输出为“0”。

(5)状态S4:系统输出为“1”。如果输入为“0”,则必须返回状态S0 继续重复检测;否则,迁移到状态S2(此时表示第二个序列可能正确输入开始)。

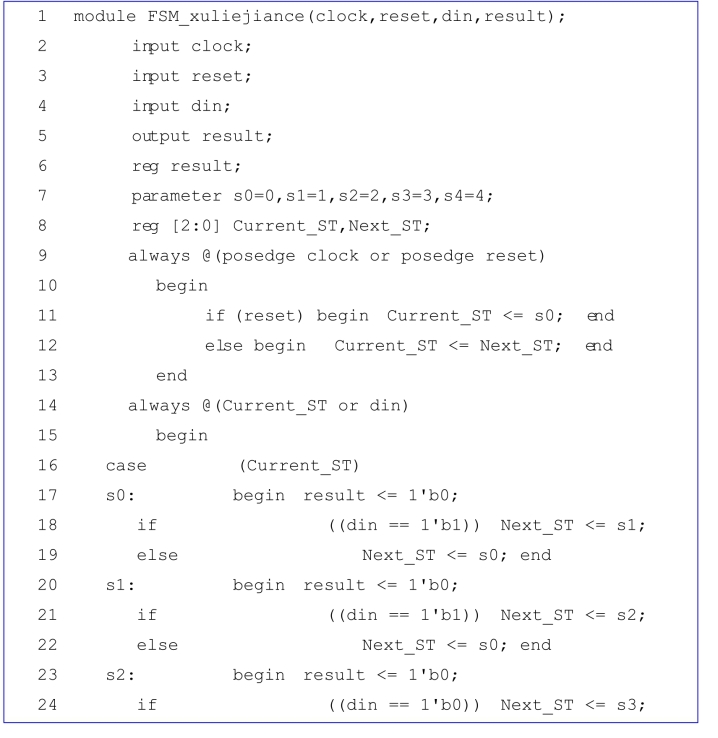

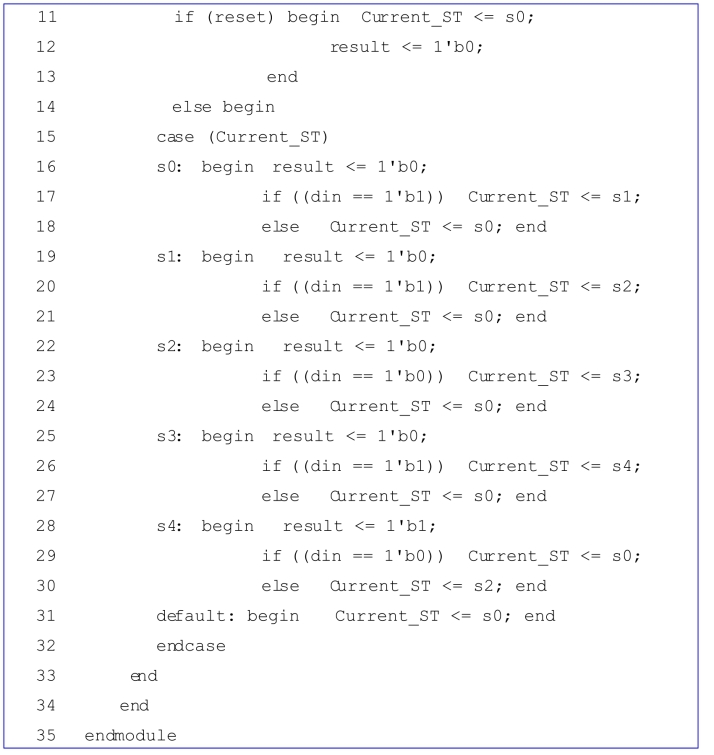

2. 设计代码

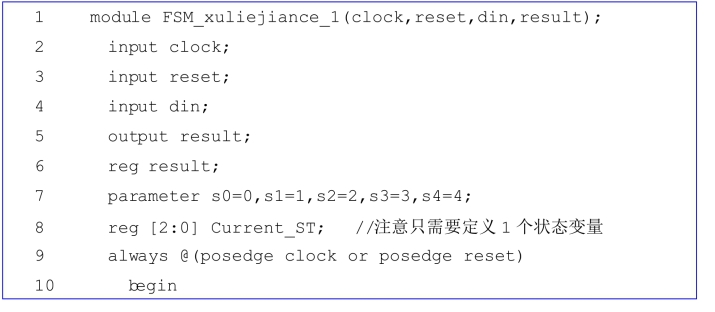

【例3.35】序列检测器状态机设计

3. 仿真波形(https://www.xing528.com)

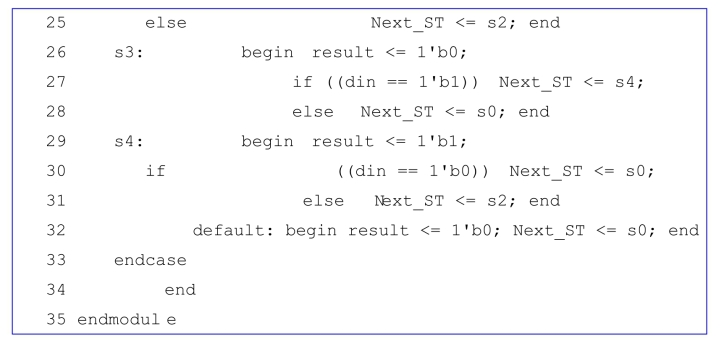

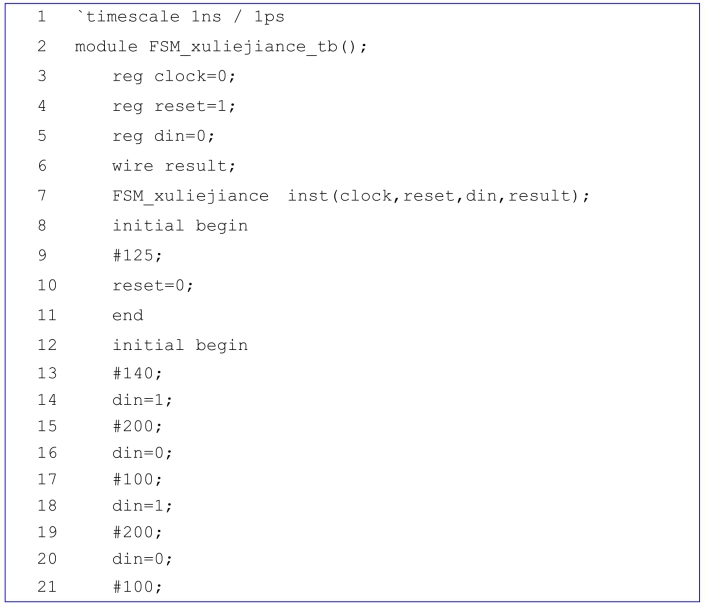

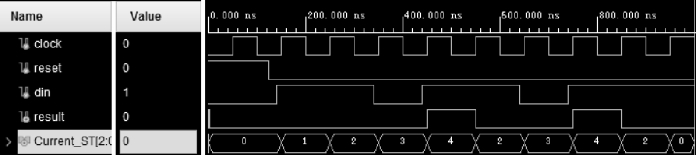

编写如【代码3.36】所示的Testbench 激励文件,完成的波形仿真如图3.58 所示。

【代码3.36】序列检测器仿真测试文件

图3.58 序列检测器仿真波形

4. FSM 常见描述风格

Verilog HDL 语法结构相对灵活,根据FSM 的基本结构,往往还可以把它变形为三进程、双进程和单进程三种描述风格。对【代码3.35】的功能,还可以采用【代码3.37】和【代码3.38】的不同表达方式。不管哪种写法,只要能正确实现功能即可。

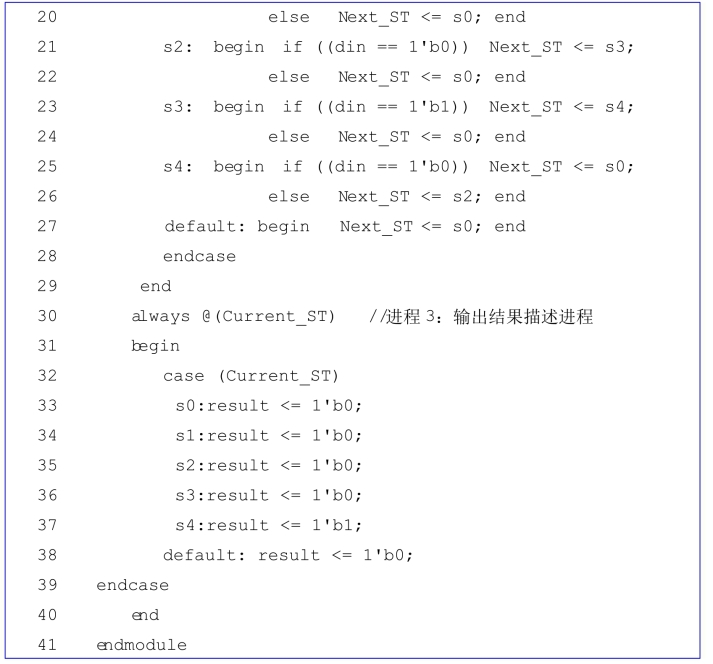

【代码3.37】FSM 三进程描述风格示例

相对于【代码3.35】而言,三进程结构描述风格,是把状态转移和系统功能输出分别用进程语句描述,这样逻辑清晰,功能直观。

【代码3.38】FSM 单进程描述风格示例

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。