1. 设计任务

在数字电路设计中,有些时候需用一组非常特殊的数字信号。一般情况下我们就将这种特殊的串行数字信号叫作序列信号。序列信号是指在同步脉冲作用下循环地产生一串周期性的二进制信号,能产生这种信号的逻辑器件就称为序列信号发生器或序列发生器。

本项目任务是完成“11001”序列发生器电路设计,周期重复输出序列信号。

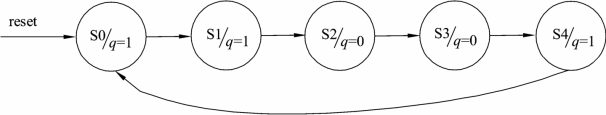

基本原理:用一个不断循环的状态机,循环产生序列信号11001,运行过程如图3.54所示。

图3.54 序列发生器状态

该序列发生器整个过程非常简单,主要包含5 个状态,分别是图中的S0~S4,其对应的功能含义如下:

(1)状态S0:初始状态,输出q=1;状态迁移到S1。

(2)状态S1:输出q=1;状态迁移到S2。

(3)状态S2:输出q=0;状态迁移到S3。

(4)状态S3:输出q=0;状态迁移到S4。

(5)状态S4:输出q=1;状态迁移到S0。

2. 设计代码

【代码3.33】“11001”序列发生器设计代码

3. 仿真波形

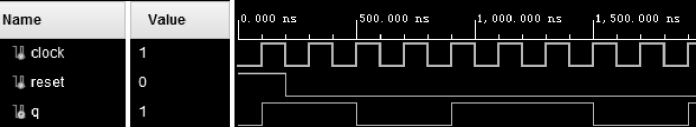

编写如【代码3.34】所示的Testbench 激励文件,完成的波形仿真如图3.55 所示。

图3.55 11001 序列发生器仿真波形

【代码3.34】序列发生器仿真测试文件

(https://www.xing528.com)

(https://www.xing528.com)

4. 状态机基本结构

【代码3.33】是一种典型的状态机结构描述,用Verilog 设计的状态机有多种形式:

① 从信号的输出方式上分有Moore(摩尔)型和Mealy(米里)型;Moore 型状态机的输出只与当前状态有关,而Mealy 型状态机的输出不仅取决于当前状态,还受到输入的直接控制。

② 从结构上分有单进程状态机和多进程状态机。

③ 从状态表达方式上分有符号化状态机和确定状态编码的状态机。

④ 从状态编码方式上分,有顺序编码状态机、一位热码编码状态机。

然而最一般和最常用的状态机设计代码通常都具有一个固定的结构,即主要由说明部分、主控时序进程、主控组合进程和辅助进程等部分构成。

(1)说明部分。

说明部分主要用来定义状态机所有可能的状态名和声明状态转换的两个变量,即在【代码3.33】中的第6 和7 行的语句。其中第6 行用关键词“parameter”定义的是状态机的各状态元素值,用具体的数值或编码来表示每个状态。第7 行声明了两个reg 型的现态和次态变量“Current_ST”“Next_ST”,以存储相应的状态值。

(2)主控时序进程。

所谓主控时序进程是指负责状态机运转和在时钟驱动下负责状态转换的进程。状态机是随外部时钟信号以同步时序方式工作,因此状态机中必须包含一个对时钟信号敏感的进程作为状态机的“驱动泵”。时钟clk 则是这个“驱动泵”中电机的驱动电源,当时钟发生有效跳变时,状态机的状态才发生变化。

一般地,主控时序进程不负责次态的具体状态取值,当时钟有效跳变到来时,它只是机械地将代表次态的“Next_ST”变量中的内容送入现态变量“Current_ST”中。主控时序进程的设计代码比较固定,可以沿用【代码3.33】中的第8 到12 行代码。

(3)主控组合进程。

主控组合进程也称为状态译码进程,其任务是根据外部输入的控制信号和当前状态值确定相应的输出以及下一状态的走向。为了更好地理解状态机的工作过程,不妨将状态机比喻为一台机床或一部机器,那么主控时序进程即为此机床的驱动电机,clk 信号即为此电机的功率泵,而主控组合进程就好比机床的加工部件,它本身的运转有赖于电机的驱动,它的具体工作方式则依赖于机床操作者的控制,该结构如图3.56 所示。

由图3.56 的基本结构可以看出,组合逻辑电路实际上就是用控制组合进程实现其功能,它通过信号“Current_ST”中的状态值,进入相应的状态,并在此状态中根据外部的信号(input)决定输出信号的取值以及“Next_ST”中的状态值。而下一状态值由状态变量“Next_ST”传递给主控时序进程,直至下一个时钟脉冲的到来再进入下一轮的状态周期转换。主控组合进程,往往就是用一个CASE 语句来实现,完成对输出端口赋值和确定状态机的下一个状态值。具体的如【代码3.33】所示。

图3.56 有限状态机的基本结构

(4)辅助进程。

辅助进程部分主要是用于配合状态机的主控组合进程和主控时序进程进行工作,以完善和提高系统的性能。例如,为了完成某种算法的进程,或用于配合状态机工作的其他时序进程,或为了稳定输出设置的数据锁存器等。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。