【摘要】:实现这种多维移位寄存器的方法可以是将几个具有相同位数的移位寄存器并联起来。图3.43移位寄存器74LS194 设计仿真波形

在数字电路中,移位寄存器(shift register)是一种在同一时钟下以触发器为基础工作的器件,数据以并行或串行的方式输入到该器件中,然后每个时间脉冲依次向左或右移动一个比特,从输出端输出。这种移位寄存器是一维的,事实上还有多维的移位寄存器,即输入、输出的数据本身就是一维数据。实现这种多维移位寄存器的方法可以是将几个具有相同位数的移位寄存器并联起来。

1. 74LS194 功能简介

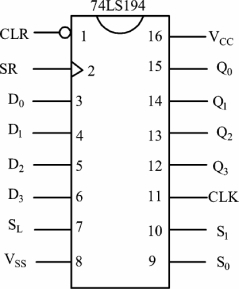

74LS194 是一个4 位双向移位寄存器,最高时钟脉冲为36 MHz,其引脚排列如图3.41所示。

图3.41 74LS194 引脚图

其中,D0~D1 为并行输入端;Q0~Q3 为并行输出端;SR 是右移串行输入端;SL是左移串行输入端;S1、S0 是操作模式控制端;CLR 是异步清零端;CLK 是时钟脉冲输入端。其功能表见表3.11。

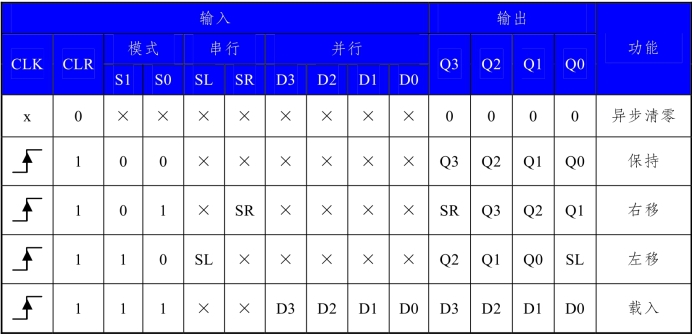

表3.11 74LS194 功能表

2. 设计代码

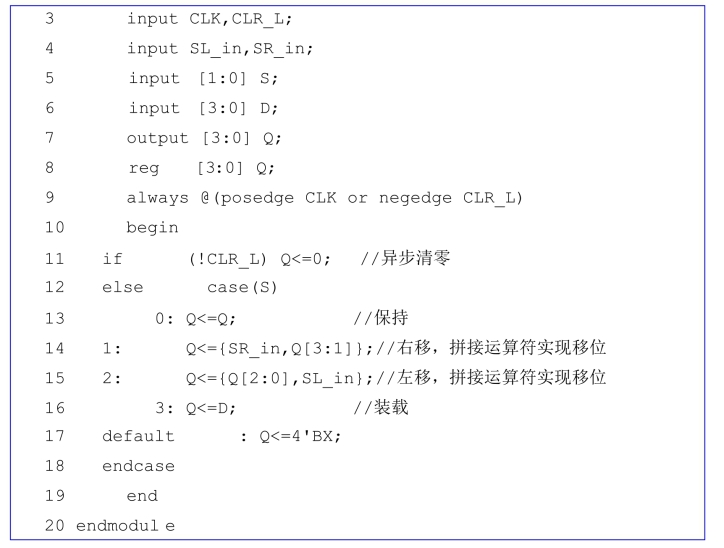

【代码3.24】移位寄存器74LS194 设计(方法1)

(https://www.xing528.com)

(https://www.xing528.com)

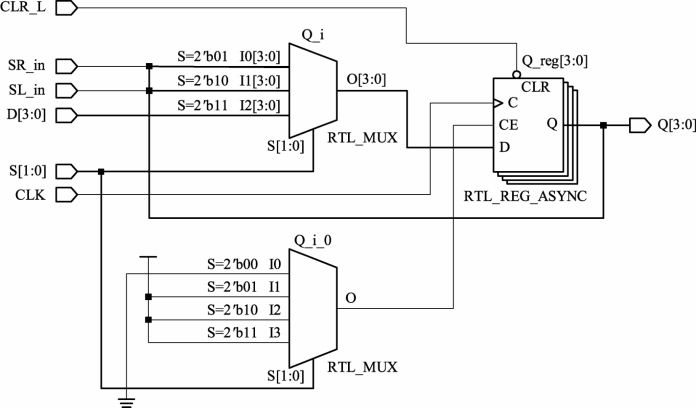

图3.42 移位寄存器74LS194 RTL 结构图

【代码3.25】移位寄存器74LS194 设计(方法2)

3. 仿真测试

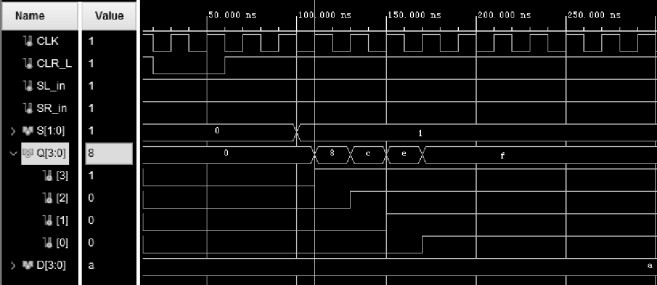

编写Testbench 测试激励文件如【代码3.26】所示,运行仿真后得到如图3.43 所示的仿真波形。

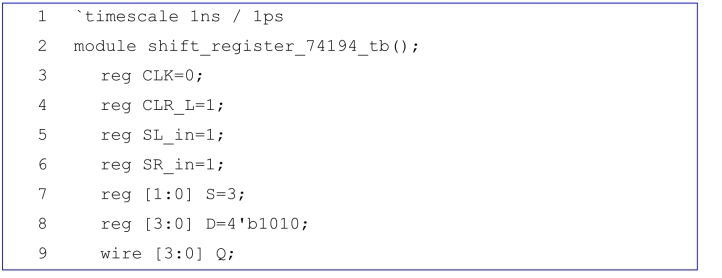

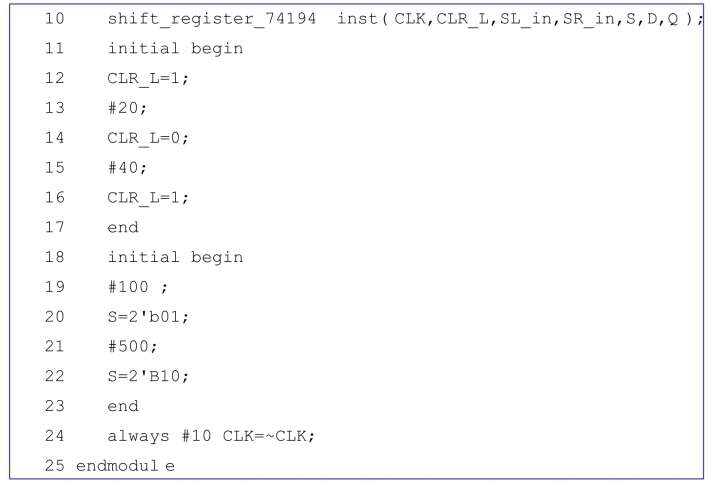

【代码3.26】移位寄存器74LS194 设计仿真测试文件。

图3.43 移位寄存器74LS194 设计仿真波形

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。