计数器是时序电路中另外一种常用的典型电路,它是在数字系统中使用最多的时序电路之一,它不仅能用于对时钟脉冲计数,还可以用于分频、定时、产生节拍脉冲和脉冲序列以及进行数字运算等,数字钟、秒表就是计数器的典型应用实例。

1. 四位二进制可预置同步加法计数器设计(74LS163)

(1)74LS163 功能简介。

74LS163 是常用的四位二进制可预置同步加法计数器,可以灵活地运用在各种数字电路以及单片机系统中,可以实现分频器等很多重要的功能,其电路外引脚如图3.36 所示。其中,CLK 是时钟,上升沿有效;CLR 是同步清零控制信号,低电平有效;ENP 是计数使能控制端,高电平有效;ENT 是进位信号使能端,高电平有效;LD 是装载预置数控制端,低电平有效;RCO 是进位信号输出端;ABCD 是4 位预置数输入端;QA\QB\QC\QD是4 位计数结果输出端。具体电路功能见74LS163 真值表,表3.10。

图3.36 74LS163 引脚图

表3.10 74LS163 真值表

从74LS163 功能表中可以知道,每当时钟上升沿有效时,如果清零端“CLR=0”,计数器输出Q3、Q2、Q1、Q0 立即为全“0”,这个时候为同步复位功能。当“CLR=1”且“LD=0”时,在CLK 上升沿作用后,74LS163 输出端Q3、Q2、Q1、Q0 的状态分别与并行数据输入端D3,D2,D1,D0 的状态一样,为同步置数功能。而只有当“CLR=LD=ENP=ENT=1”、CLK 脉冲上升沿作用后,计数器加1。74LS163 还有一个进位输出端RCO,其逻辑关系是RCO=Q0·Q1·Q2·Q3·ENT。合理应用计数器的清零功能和置数功能,一片74LS163 可以组成16 进制以下的任意进制分频器。

(2)设计代码。

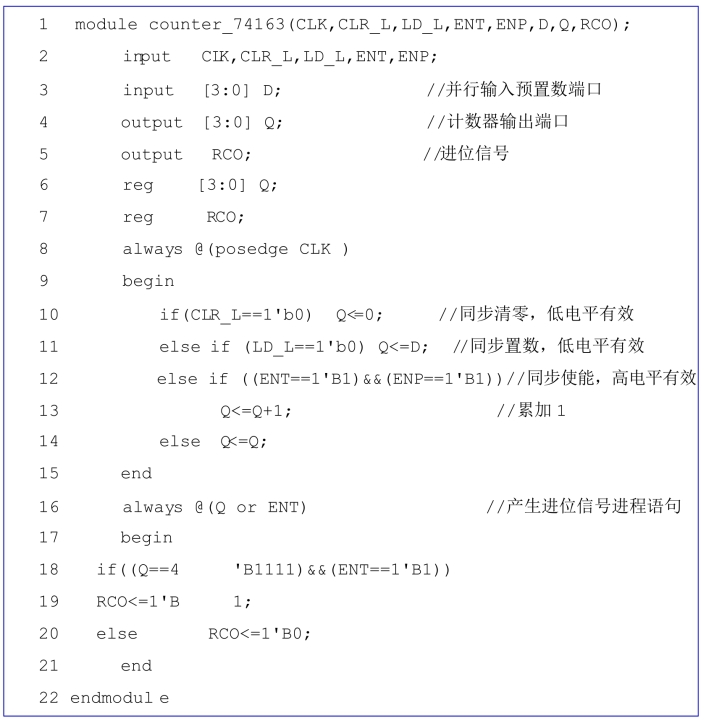

【代码3.20】四位二进制可预置同步加法计数器。

在【代码3.20】中,时钟进程语句的敏感信号只有对CLK 的上升沿表达,未放入其他任何信号,说明其他所有信号都是受时钟同步的,同步清零、同步预置、同步使能计数等,CLR 优先级最高,预置使能次之,计数使能和进位使能再次之,采用了if_else if的结构。“Q<=Q+1”实现了累加计数功能。代码综合实现后对应的RTL 电路结构如图3.37所示。

(3)仿真结果。

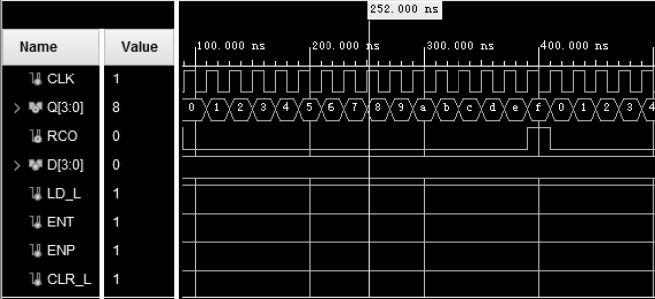

编写Testbench 仿真测试文件见【代码3.21】,完成对【代码3.20】进行仿真的波形如图3.38 所示。

图3.37 74LS163 计数器RTL 结构

【代码3.21】四位二进制可预置同步加法计数器仿真测试代码。(https://www.xing528.com)

图3.38 74LS163 计数器仿真波形

从仿真波形可以验证电路描述功能正确,请自行分析仿真结果。

2. 任意模计数器的设计

在采用计数器实现分频、计数、计时等实际应用时,往往不需要严格完全使用上述功能的控制信号,而只需按照需求实现相应计数范围和简单计数功能即可。下面以模5计数器为例,介绍带模计数器的设计方法,模5 计数器就是从0 到循环4 计数,即有5个状态,输出为0~4,然后返回0。

【代码3.22】带模计数器设计示例。

在【代码3.22】中,定义了异步清零端,注意异步时钟信号在敏感信号列表中的表达方式;定义常量“parameter n=5”,表示此例计数器的模为5,如果要设计任意模数的计数器,则只需修改n 的取值即可。综合后的RTL 结构如图3.39 所示。

图3.39 模n 计数器的RTL 结构

编写Testbench 测试激励文件如【代码3.23】所示,运行仿真后得到如图3.40 所示的仿真波形。

【代码3.23】带模计数器设计示例仿真测试文件

图3.40 模5 计数器仿真波形

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。