本小节将以典型的时序电路元件D 触发器、T 触发器和JK 触发器设计为例,详细介绍基于Verilog 的时序电路设计表述方法和新的语法现象。

1. D 触发器设计

(1)D 触发器的功能。

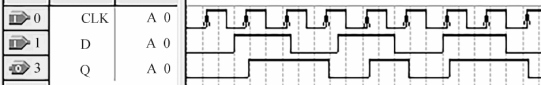

D 触发器是现代数字系统设计中最基本、最常用、最具代表性的时序单元和底层元件,JK 和T 触发器都是由D 触发器构建而成。其外观如图3.31 所示,功能特征是当时钟上升沿有效时,将D 输入端信号传输给Q 输出端输出,当时钟信号处于其他状态时,Q 输出端的值保持不变。图3.32 是D 触发器的时序波形,只有在上升沿时刻,Q 的值才发生改变。

图3.31 D 触发器

图3.32 D 触发器的时序波形

(2)设计代码。

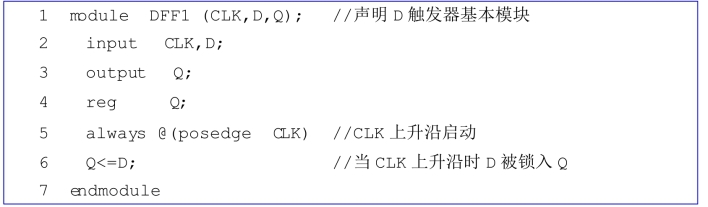

【代码3.15】边沿触发型D 触发器设计

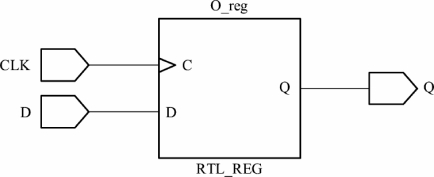

在【代码3.15】中,只使用了一个简单的always 语句,但对应的敏感信号表达式与之前使用大不相同,此处由关键词posedge 引导的表达式可以理解为是对某一信号上升沿敏感的表述,或表示CLK 上升沿到来的敏感时刻。此处表示当输入信号CLK 出现一个上升沿时,敏感信号“posedge CLK”将启动过程语句的执行。代码综合后的RTL 结构如图3.33 所示。

图3.33 D 触发器的RTL 结构

(3)时钟边沿表达式。

在时序电路的Verilog HDL 描述中,上升沿使用关键词“posedge”表述,下降沿使用关键词“negedge”表述,其表述格式如下:

posedge 信号名 //表述某信号的上升沿

negedge 信号名 //表述某信号的下降沿

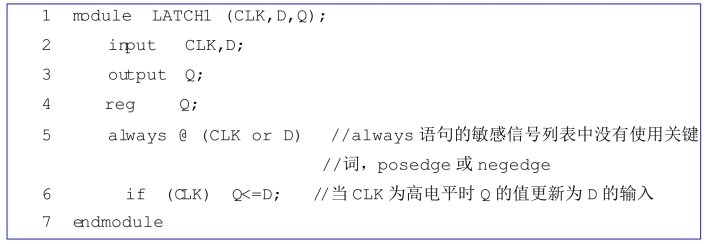

“posedge CLK”出现在always 语句的敏感信号列表,此时综合器会自动构建以边沿触发型的时序结构。因此“posedge CLK”可以认为是时序元件对CLK 信号上升沿敏感的标志符号,即凡是边沿触发性质的时序元件必须使用时钟边沿敏感表述,放置在always过程语句的敏感信号列表中。而没有使用该敏感表述标志所产生的电路都是电平敏感性时序电路,如下列代码所示:

(4)异步清零/同步使能的D 触发器设计。

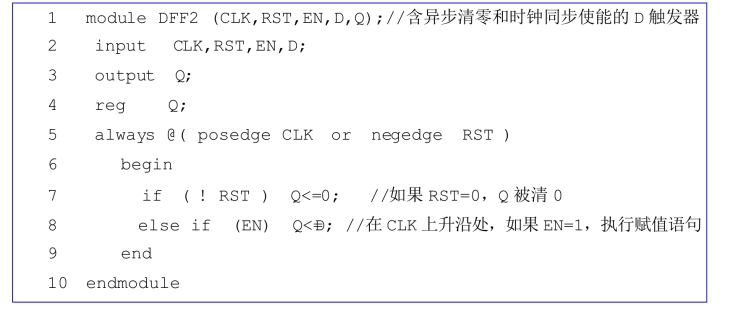

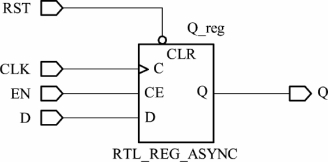

【代码3.15】是基本功能的D 触发器,在实际使用中,D 触发器往往还需要带有异步清零和同步使能功能。这里所谓的“异步”并非指时序的异步,而是指独立于时钟控制的复位控制端,即在任何时刻,只要RST 复位端为0,D 触发器的输出端即刻被清0,与时钟状态无关。“同步”使能是指当使能信号为1 时,必须还要在时钟CLK 的上升沿到来时才有效,因此与时钟状态有关。含异步清零和同步时钟使能的D 触发器设计如【代码3.16】所示,综合后的RTL 结构如图3.34 所示。

【代码3.16】异步清零/同步使能的D 触发器设计

图3.34 异步清零/同步使能的D 触发器RTL 结构

与【代码3.15】相比,【代码3.16】中多定义了一个清零端RST 和一个使能端EN,除此以外,在always 进程语句的敏感信号表中还多了一个RST 下降沿敏感表达式。

(5)时钟进程表述的特点。(https://www.xing528.com)

前文曾经谈到,过程语句中的敏感信号列表中的敏感信号的多选、少选或漏选都不会影响电路的逻辑结构,因为综合器会默认过程语句中敏感信号列表中会列全了所有应该被列入的信号。但这种情况主要针对没有使用关键词posedge 或negedge 的敏感信号表。

编程时应特别注意,当敏感信号表中含有边沿敏感的posedge 或negedge 时,选择性的改变敏感信号的放置是会影响综合结果的。对于【代码3.16】中虽然放置了RST 的边沿敏感信号,但在模块中,它实际上是独立于时钟CLK 的电平敏感型变量,这好像与negedge 的本意不符,但在程序代码描述中,RST 的边沿敏感信号的确采用的电平判断。

另外还需注意,一旦在敏感列表中放置了posedge 或negedge 的边沿信号后,所有其他电平敏感型变量都不能放置在敏感信号列表中,从而导致在该过程语句内部的所有未能进入敏感信号列表的变量都必须是相对于时钟同步。所以,如果希望在同一个模块中含有独立于主时钟的时序或组合逻辑,则必须用另一个过程来描述。

(6)时钟进程设计规律。

① 如果将某一信号A 定义为边沿敏感时钟信号,则必须在敏感信号列表中给出相应的表述,如posedge A 或negedge A;但在always 进程中不能再出现信号A 了。

② 如果将某信号B 定义为对应于时钟的电平敏感的异步控制信号,则除了在敏感信号列表中给出对应的表述外,如posedge B 或negedge B,在always 进程中必须明示信号B 的逻辑行为,如【代码3.16】中的RST。特别注意这种表述的不一致性,即敏感信号声明为边沿型,但电路中却使用为电平型敏感信号。

③ 如果将某信号定义为对应于时钟的同步控制信号,则绝不能以任何形式出现在敏感信号列表中。

④ 敏感信号列表中一旦出现类似posedge 或negedge 的边沿型敏感表述,则绝不允许出现其他非敏感信号的表述。即敏感和非敏感表述不能同时出现在敏感信号列表中;每个过程语句中只能放置一种类型的敏感信号,不能混放。

(7)异步时序模块设计。

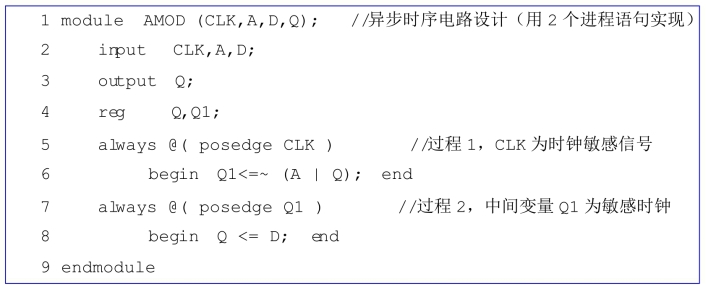

可以将含有时钟边沿敏感的过程语句称为时钟进程。在时序电路设计中应注意,一个时钟进程只能构成对应单一时钟信号的时序电路。如果在某一个过程中,需要构成多触发时序电路,也只能产生对应某个单一时钟的同步时序逻辑。而异步时序逻辑电路的设计则必须采用多个时钟进程语句来构成,如【代码3.17】所示的异步时序电路设计。

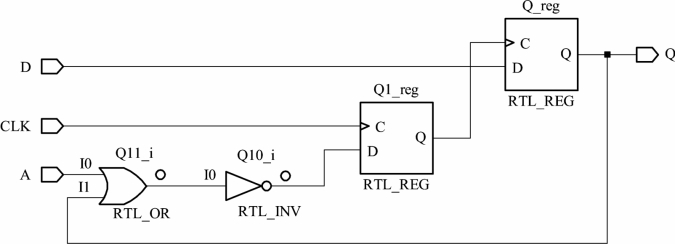

【代码3.17】异步时序电路设计

【代码3.17】综合后对应的RTL 电路结构如图3.35 所示,分别使用了两个D 触发器,但是两个触发器的时钟不是同一个,所以称为异步时序电路,即系统中各功能单元不随某个主控时钟同步,没有一个统一的系统时钟。这种系统是极其不稳定的,容易产生有害的冒险竞争,无法形成高速工作模块。因此,在现代数字系统设计中,极少有应用异步时序逻辑的场合,故在此不深入探讨。

图3.35 【例3.17】对应的RTL 电路图

2. T 触发器设计

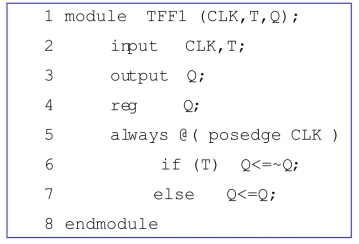

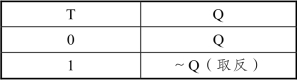

T 触发器也称翻转触发器,其功能如表3.8 所示,在时钟CLK 的上升沿到来时,如果T=1,输出Q 将取反输出(即翻转);如果T=0,输出Q 将保持当前值不变。完成T 触发器代码设计。

【代码3.18】T 触发器设计。

表3.8 T 触发器功能表

3. JK 触发器设计

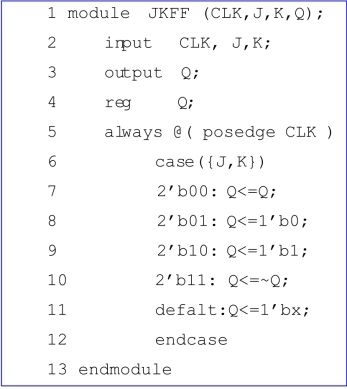

JK 触发器的真值表如表3.9 所示,Verilog 设计见【代码3.19】。

【代码3.19】JK 触发器设计

表3.9 JK 触发器功能表

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。