译码器是一种多输入多输出的组合逻辑电路,负责将二进制代码翻译为特定的对象(如逻辑电平),或将某一特定的输入状态翻译为其他具有特定物理含义的事件状态,往往是输入和输出一一对应关系。典型的如3-8 译码器、2-4 译码器、七段码译码器等。本小节将以74LS138 译码器为例详细介绍译码器设计方法。

1. 74LS138 译码器功能简介

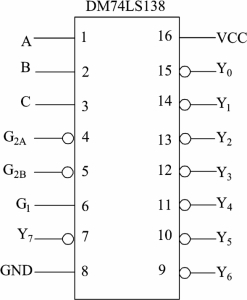

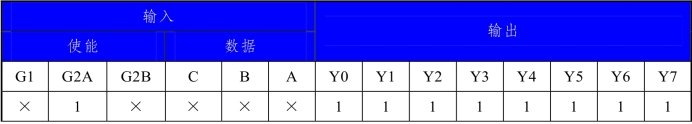

图 3.18 给出了 74LS138 3-8 译码器的管脚符号描述,通过阅读器件数据手册(Datasheet),可以获得各管脚功能,其中引脚C,B,A 为3 位数据输入端,C 为高位;Y7~Y0 是译码数据输出端,用来表示译码输出组合,低电平有效;G1,G2A,G2B 是使能控制端,G1 高电平有效,G2A,G2B 低电平有效。表3.2 是74LS138 的功能表,当使能控制端有效时,在一个时刻输出引脚Y7~Y0 中只有一位为低,其余输出均为高,且输出状态为低的信号位码编号与输入三位数据的值对应,即当输入CBA=000 时,Y7~Y0=11111110(即只有Y0=0);当CBA=001 时,Y7~Y0=11111101(即Y1=0),以此类推;当使能控制端无效时,Y7~Y0 全部输出为高。

图3.18 74LS138 译码器管脚图

表3.2 74LS138 译码器功能表

续表

2. 设计代码

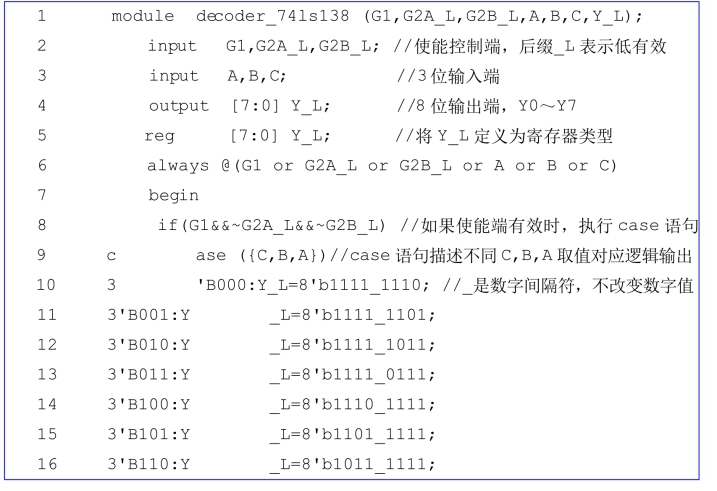

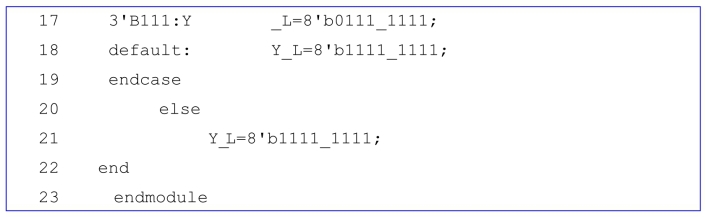

根据74LS138 译码器的逻辑功能,完成Verilog HDL 代码如【代码3.7】所示,代码中主要采用if 语句实现使能端控制逻辑描述,采用case 语句实现对不同状态输入时使输出获取唯一取值的操作,重点理解case 语句特点,领会其应用场景。

【代码3.7】74LS138 译码器设计代码

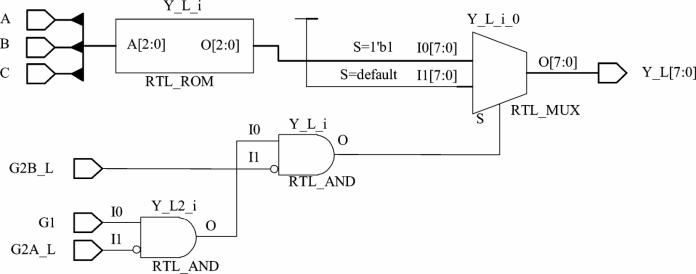

通过Vivado 对【代码3.7】进行综合实现后,可查看RTL 级电路结果,如图3.19 所示。其中,代码综合后生成了“RTL_ROM”存储器结构的查找表单元实现了case 语句功能;2 选1 数据选择器“RTL_MUX”单元实现了if 语句判断功能;两个“RTL_AND”单元实现了if 语句中条件表达式“G1&&~G2A_L&&~G2B_L”的电路功能。由此可见,硬件描述语言的每一个语句结构都将对应一个具体硬件电路单元,故硬件描述语言的代码设计结果是硬件,与C 语言等软件语言的结果(二进制代码流,只能供CPU 识别处理)有本质区别,不能用C 语言的代码编写思想转移到Verilog HDL 语言的学习中。

图3.19 74LS138 RTL 结构图

3. if_else 语句

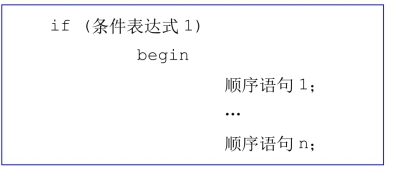

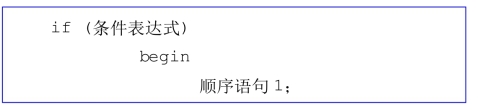

在Verilog 中,条件语句(if_else 语句)用于表达执行某项由条件控制是否操作的结构,即往往表达“当某个条件为真时,执行某项操作;否则,执行另外的操作”。常见有以下三种表述方法:

(1)表述方法1。

在表述方法1 中,表示有多个条件分支选项时的if 结构,“条件表达式”一般为逻辑表达式或关系表达式,也可以是位宽为1 位的变量。若表达式计算结果为0、x、z 时,按“假”处理,若为1 时,按“真”处理。其功能是首先判断条件表达式1 的逻辑值,如果为真,则执行后面的语句块;如果条件表达式1 为假,则继续判断条件表达式2 的逻辑值,选择执行后面的块语句;如果所有表达式都为假,则执行最后的else 后面的块语句。

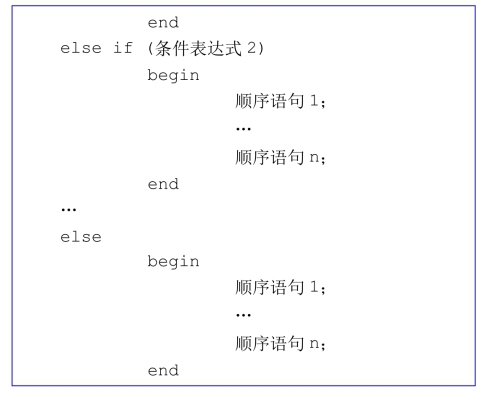

(2)表述方法2。

(3)表述方法3。

表述方法2 适合于条件分支选项只有两个,即条件成立和不成立时都对应有相应操作。表述方法3 中只表达了条件成立时对应的操作,没有描述条件不成立时的电路功能,故称为不完整条件语句。在综合时,往往会将不完整条件语句对应成时序电路,完整条件语句对应成组合电路。因此if 语句的else 分支项写与不写,将会对电路的综合结果有影响,可能会出现不同的综合结果。

(1)if 语句属于顺序语句,Verilog HDL 规定所有顺序语句必须用always语句来引导,不能单独使用!

(2)当条件成立后对应的执行操作不止一条语句时,一定要使用“begin_end”将多条语句构成顺序块语句,如果只有一条执行语句,则可省略“begin_end”。(https://www.xing528.com)

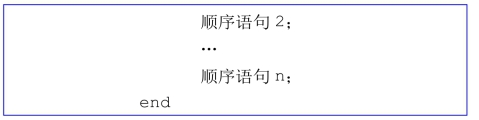

4. case 语句

在Verilog 中有两类可综合的条件语句,即if_else 和case_endcase 语句,它们都属于顺序语句,因此必须放在always 过程语句中。case 语句是一种多分支语句,可以用来直接描述真值表,常常用于译码器、数据选择器、状态机、存储器等设计。基本格式如下:

case 语句由关键词“case_endcase”构成,执行该语句时,首先计算表达式的值,然后执行选择值与表达式值相同的冒号后边的语句或块语句,当所有的选择值都不与表达式的值相同时,则执行“default”后的语句。

(1)case 语句中表达式必须是一个,不能同时对多个表达式进行讨论。

(2)所有选择值必须在表达式的取值范围之类,且数据类型必须匹配。

(3)允许出现多个选择值取相同值的情况,这时,代码将执行最先满足条件的分支项,然后随即跳出case。

(4)除非把所有表达式的取值都列完,否则最后一行必须加上关键词“default”引导的语句。

(5)注意if_else 和case 语句是可以相互嵌套使用的。

5. 逻辑值和数字格式

(1)逻辑值。

在Verilog 中有4 种基本逻辑值,分别是1、0、z(或Z)和x(或X),其含义如下:

① 1:含义可以是二进制数字1、高电平、逻辑1 和事件为真的判断结果。

② 0:含义可以是二进制数字0、低电平、逻辑0 和事件为假的判断结果。

③ z 或(Z):含义是高阻态或高阻值。高阻值还可以用问号“?”表示。

④ x 或(X):含义是不确定,或未知的逻辑状态。X 和Z 都不分大小写。

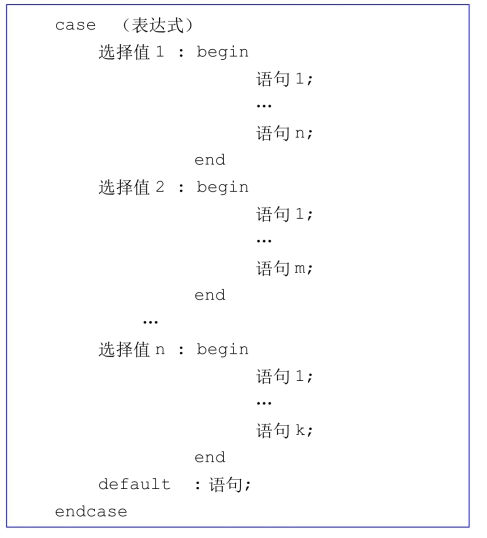

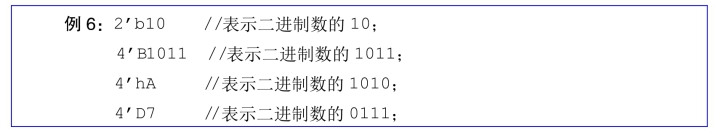

(2)数字格式。

在【代码3.7】中出现了不同的数据格式表达形式,Verilog 中定义了一个二进制数的一般格式如下:

<位宽>’<进制> <数字>

在该格式中,符号“'”(撇)左侧的“位宽”常常是一个十进制数,表示二进制数的位数;撇右侧的“进制”常常是用字母B、O、H、D 之一来表示“数字”的进制,其中B 是二进制、O 是八进制、H 是十六进制、D 是十进制,这几个字母不分大小写。

(1)这种格式的数字表示中,位宽可以省略,如’b10,’hA 等。

(2)十进制数的位宽和进制都可以省略,直接写数字,如120,表示十进制数120。

(3)x 和z 可以出现在除了十进制数以外的数字形式中。x 和z 所占位数,由所在数字进制决定,二进制数中,一个x 或z 表示1 位;十六进制中,一个x 或z 表示4 位;八进制中,一个x 或z 表示3 位。例如,’b1111xxxx 等价于’hfx;’b1101zzzz等价于’hdz。

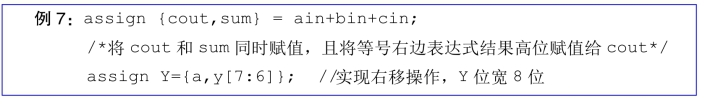

6. 并位运算符 { }

在【代码3.7】的case 语句表达式中,有这样的表达形式“{C,B,A}”,这里大括号“{ }”是并位运算符。它的功能是将两个或多个信号按照二进制位拼接起来,作为一个整体信号使用。例如,【代码3.7】中3 个输入信号C、B、A 各自取值范围是二进制数0 和1,若将它们用并位运算符拼接起来后就得到了一个3 位宽度的矢量信号,这个新的信号取值范围将是3 位二进制数范围。注意在进行并位运算时,每个成员的位置和顺序关系。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。