【摘要】:图3.16激励信号波形3. 阅读Testbench 测试文件,画出激励信号a,b,c 的波形图。简易分频器代码5. 已知一位二进制全加器原理结构如图 3.17 所示,通过调用 2 个半加器模块和1 个或门构成,其中“h_adder”和“or2a”模块设计文件如和所示,请用例化方式完成对一位二进制全加器电路的Verilog 描述。图3.17一位二进制全加器原理图半加器h_adder.v或门or2a.v

1. 根据 Testbench 设计方法,请编写相应代码key_led_tb.v,实现对【代码 3.1】“key_led.v”逻辑功能仿真测试。

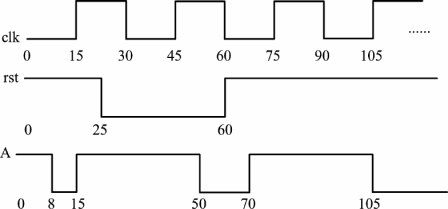

2. 已知某设计电路的输入激励信号clk,rst,A,其变化规律如图3.16 所示,为了能实现对该电路功能仿真,请运用Verilog HDL 相关语句,完成此激励信号产生的代码段(从声明必要的变量开始),不用写完整的Testbench 代码。

图3.16 激励信号波形

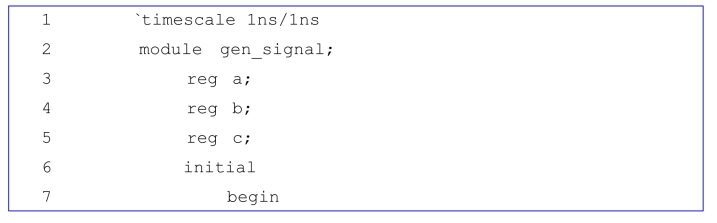

3. 阅读Testbench 测试文件【代码3-4】,画出激励信号a,b,c 的波形图。

【代码3.4】gen_signal.v

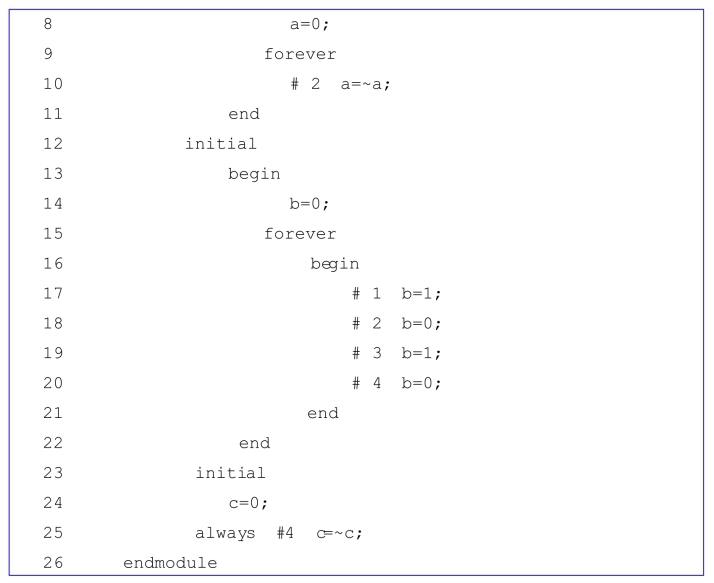

4. 已知采用Verilog HDL 完成了简易分频器电路代码设计,如【代码3.5】所示,但不能确定设计功能是否正确,请编写Testbench 测试文件(div_freq_tb.v),实现对该电路的功能仿真测试。

【代码3.5】简易分频器代码(https://www.xing528.com)

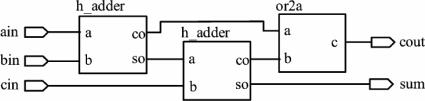

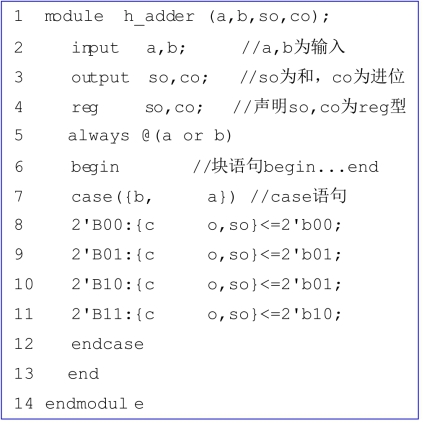

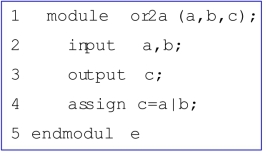

5. 已知一位二进制全加器原理结构如图 3.17 所示,通过调用 2 个半加器模块(h_adder.v)和1 个或门(or2a)构成,其中“h_adder”和“or2a”模块设计文件如【代码3.6】和【代码3.7】所示,请用例化方式完成对一位二进制全加器电路的Verilog 描述。

图3.17 一位二进制全加器原理图

【代码3.6】半加器h_adder.v

【代码3-7】或门or2a.v

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。