1. 层次化设计概念

Verilog HDL 采用的是自顶向下的设计方法,无论多么复杂的系统,总能划分为多个小的功能模块,每个小的功能模块又可以继续往下细分为功能更简单的若干模块,直到能用最简单、最基本的常见电路单元实现为止,这种设计方法称为层次化设计。模块是分层的,高层模块通过调用、连接低层模块的实例来实现复杂功能,各模块连接完成的整个系统称为顶层模块(top-module),如图3.9 所示。

图3.9 层次化设计结构

在图3.9 中,顶层系统设计文件Top.v 是由调用模块A 和模块B 实现,而模块A 又是由调用模块C 和模块D 实现。其中,模块A 和B 对Top.v 而言称为底层被调用模块(或称为子模块),Top.v 称为顶层模块;模块C 和D 对模块A 而言称为底层模块(子模块),此时模块A 称为顶层模块。

2. 元件例化语句

Verilog HDL 提供了将一个模块嵌入到其他模块的层次化描述语句,即在一个模块设计中调用其他功能单元模块的语句,称为元件例化语句。高层次模块创建低层次模块的例化,并且通过input、output 和inout 端口进行通信,其基本结构如下所示:

其中,<模块名>是指被调用底层元件的模块名(实体名),<例化名>是指被调用模块在顶层中系统电路中的位置,也称为例化号,只是一个编号而已,例如u1、u2……

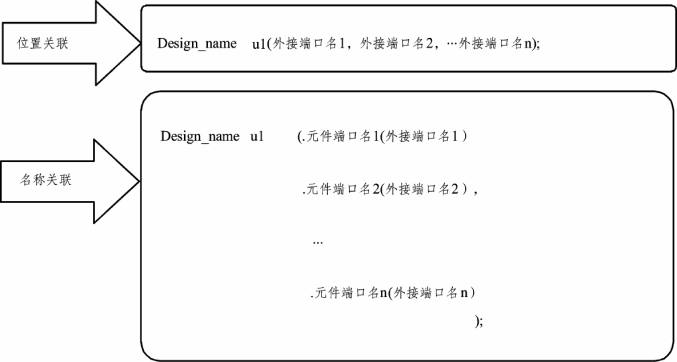

在例化语句结构中的端口映射表达式有位置关联和名称关联两种表达方式,具体格式如下所示。(https://www.xing528.com)

(1)位置关联法。

在调用模块时,需严格按照模块定义的端口顺序来连接,按位置对应,不用标明底层模块定义时规定的端口名,故在放置外接端口名的时候对位置顺序有要求,不能交换顺序。

(2)名称关联法。

在调用模块时,用“.”符号,标明底层模块定义时规定的端口名,此时端口名放置的前后顺序位置没有关系,可以任意放置。建议在例化结构中尽可能使用此方法。

(3)悬空端口的处理。

在实例化中,可能有些管脚没有用到,可在端口映射中采用空白处理。对于输入管脚悬空,该管脚输入为高阻Z;输出管脚悬空,该管脚废弃不用。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。