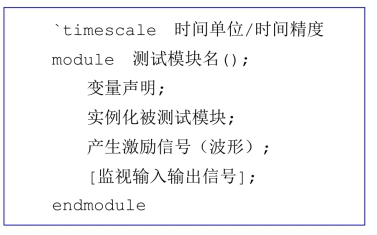

Testbench 的代码结构和通用的Verilog HDL 设计代码结构基本相同,但也有细微差别。相同点是它们都是Verilog 代码,都是以“module”开头,以“endmodule”结束。不同点是测试平台的模块不需要定义输入输出端口,但内部必须要实例化被测试的模块。其基本结构如下:

1. 时间刻度定义

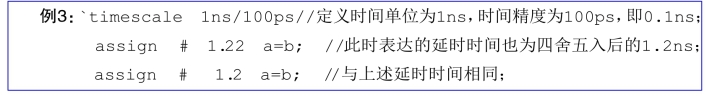

在测试平台中,往往在开始之前,会采用“`timescale”预编译指令定义仿真器的时间单位和时间精确度。与C 语言类似,Verilog 也有预编译指令,所有预编译指令均是以“`”字符开头,且结尾不需要分号“;”为结束标志。其中,时间单位由数字与单位组成,数字只能是1、10 和100 三个数字之一,单位可以是s,ms,μs,ns,ps,fs。

时间精度也是由数字和单位组成,后面的单位是前面单位的下一个级别。如果代码中出现的时间量大于“`timescale”所定义的时间精度,则四舍五入到定义的时间精度内。

在【代码3.3】中,“`timescale 1ns/1ps”表示定义时间单位为1 ns,时间精度也是1 ps。预编译指令对应语句是不可综合的。

2. 测试模块名

编写测试平台的模块名命名规则一般会用被测试模块的名字后加上“_tb”后缀,“tb”是英语测试平台“test bench”的缩写。例如,【代码3.3】中被测试模块是“counter4b”,则测试平台的命名为“counter4b_tb”。

3. 变量声明

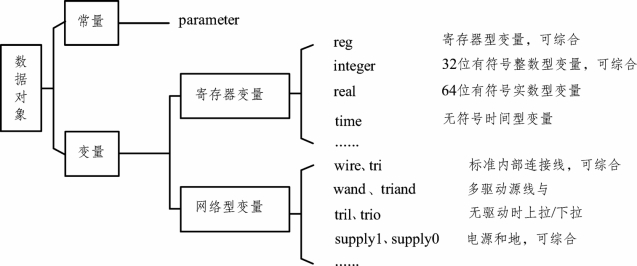

(1)数据对象。

在Verilog HDL 中,所谓数据对象是指用来存放各种类型数据的容器,主要包含常量和变量。其中,常量是指恒定不变的量,一般是一个具体数值,在程序开始之前定义,用来表示模块内部或外部的参数,类似于C 语言中的宏定义常量;变量是指在程序运行时其值可以改变的量,在Verilog HDL 中的变量主要分为网络型(nets type)和寄存器型(register type)两种,如图3.8 所示。

图3.8 数据对象分类

在采用Verilog HDL 进行电路设计时,最常用的变量类型为reg 和wire 两种,其余类型如real 和time 寄存器变量都是纯数学的抽象描述,往往不对应任何具体的硬件电路,即这种寄存器类型均不可综合,在特殊电路描述中使用,此处不再详述。

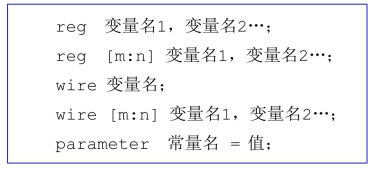

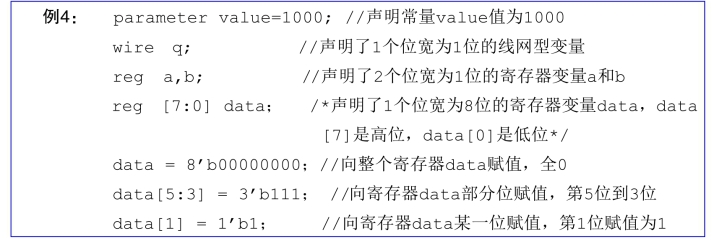

(2)变量声明格式。

所有数据对象必须遵循先声明后使用原则,其定义格式如下:(https://www.xing528.com)

其中,reg 为寄存器变量的关键词,只能小写,格式中可以定义相应变量的位宽参数,默认位宽为1 位,也可以用[m:n]格式表明所需要的矢量位宽。

(3)reg 和wire 的区别。

reg 型变量是对数据存储元件的抽象表述,从当前赋值到下一次赋值之前,保持当前的值不变,由赋值语句改变寄存器变量中的值;wire 型变量表示器件之间的物理连线,需要门和模块的驱动,wire 型变量不能保存值,只能传递数据,其输出始终根据输入的变化而变化。

在Verilog 模块设计中所有声明的端口默认为wire 型,所有wire 型的变量需要由assign 连续赋值语句提供驱动源数据;reg 型变量只能在initial 和always 内部进行赋值操作,反之,在initial 和always 内部的赋值对象必须是reg 型变量。

(4)Testbench 中变量声明技巧。

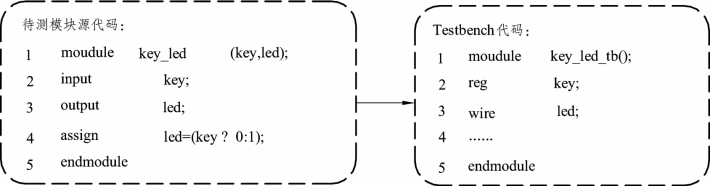

在编写Testbench 代码中变量声明是为被测试模块提供对应接口,与被测试模块端口对应即可,数量、位宽保持不变,变量名可以与待测模块端口名一致,也可自己任取,但变量数据类型应该把被测试模块的输入端口对应声明为reg 型,而输出端口声明为wire型,双向端口需要另外的处理,即与输入端口相连接的变量定义为reg,与输出端口相连的定义为wire。

例如【代码3.1】模块中端口有1 输入key 和1 输出led,如果要对该电路进行仿真测试,那么对应的Testbench 的变量声明部分只需定义一个reg 型变量和一个wire 型变量即可,如下所示。

4. 实例化被测试模块

实例化被测试模块是对被测试模块进行端口映射,把产生的输入激励信号连接到被测试模块的输入端口中。同时,连接输出端口以便观察输出结果。一般采用Verilog 实例化方法即可(元件例化语句结构见后文所述)。

5. 产生激励信号(波形)

根据待测模块逻辑功能和输入端口变化规律,往往采用initial 语句和always 过程语句实现激励信号(波形)的产生。激励信号可分为一次特定的序列和重复的信号两类,一般需要为待测模块每一个输入端口产生一个激励信号,信号取值变化或波形形状视端口功能含义而定。

6. 监视输入输出信号

可以通过调用相关的系统任务和函数,实现对相关信号值的打印与保存功能。这些系统任务与函数主要有显示类系统任务、文件输入输出类、时间标度类、仿真控制类、仿真时间类等,如$time,$display,$write 等。在此不做详细介绍,需要深入理解时请参考其他书籍。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。