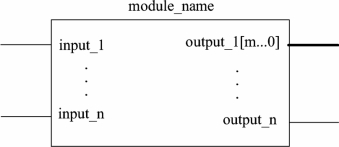

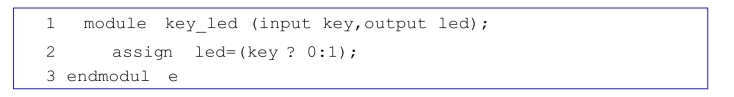

模块声明(【代码3.1】第1~3 行)也叫电路设计实体描述,用于定义电路外观属性、名字、管脚特征。主要包括定义模块名字(实体名)、模块的输入输出端口名及属性声明。设计电路实体往往可以采用图3.2 所示的图形结构表示。

图3.2 设计实体图形表示

1. 模块名

模块名也叫实体名,属于标识符。由设计者自己为该电路功能定义的名字,即该电路的器件名,因此一般名字能反映该电路的具体功能。例如,4 位二进制计数器,可以取名counter4b;4 位二进制加法器,可以取名为ADDER4B 等。在工程实现中,往往需要用模块名作为文件名来保存,后缀为.v。例如,【代码3.1】应该保存为“key_led.v”。并且注意文件名的大小写,必须与模块中模块名(实体名)保持一致。

2. 端口列表

在模块名右边用括号引出的内容是该模块的所有输入输出端口列表,输入/输出端口是模块与外部电路连接的接口,是与外部电路进行通信和数据交换的通道。这如同一个芯片必须有外部引脚一样,必须具有输入输出或双向口等引脚,以便与外部电路交换信息。

通常在进行Verilog 电路设计时,需要将该电路的所有输入/输出端口全部放入端口列表,端口名根据电路接口功能自己定义,它也属于标识符格式。各个端口名之间原则上没有位置顺序之分,用逗号隔开即可。

除了在Verilog 的Testbench 仿真测试模块中不需要定义端口外,其余的module 模块中都需定义端口。

3. 标识符命名规则

标识符只可由英文字母(含大小写)、数字、下画线( _ )和美元符号($)组合而成,除此以外的字符均是非法字符。且所有标识符都只能是以字母或下画线( _ )开头,不能用数字、中文或其他非法字符开头,同时也不能用Verilog 库中定义好的关键词或元件名作为标识符命名。

4. 端口声明语句

端口声明语句的功能是对端口列表中的每个端口名进行详细的属性定义,主要包括定义端口的方向、数据宽度。端口声明语句使用的关键词主要有3 种:input(输入)、output(输出)和inout(双向,输入输出),表示数据流动方向和方式。(https://www.xing528.com)

(1)input:输入模式,定义端口为单向只读模式,即规定数据只能由此类端口被读入进模块电路中,不允许对输入模式端口进行赋值操作。

(2)output:输出模式,定义端口为单向输出模式,即规定数据只能通过此类端口从模块电路内部向外流出,或者说只能对输出模式端口赋值,而绝对不能从此类端口读值进行比较判断等操作。

(3)inout:双向端口,定义端口为输入输出双向模式,即从端口的内部看,可以对此类端口进行赋值操作,也可以通过此类端口读入外部的数据信息;而从端口外部看,信号既可从该端口流出,也可向此端口输入信号,如RAM 的数据端口、单片机的I/O 口等。

端口声明语句的一般格式如下:

其中,参数[m:n]表明此端口是一个逻辑位矢量,即定义端口为总线。通常,m 表示矢量的最高位,n 表示矢量的最低位,总线宽度为m-n+1。

Verilog-2001 版本允许将端口声明和端口名都放在模块端口列表中,如【代码3.1】的模块端口列表和端口声明语句合并为“module key_led(input key,output led);”。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。