(1)创建仿真激励文件。

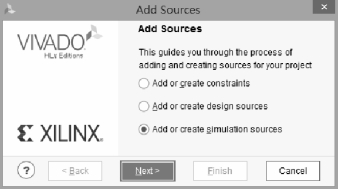

在图2.32 所示的“Sources”源文件管理窗口中,右键单击【Simulation Sources(1)】选项,弹出子菜单中选择【Add Sources…】弹出添加源文件对话框。

图2.32 添加仿真激励文件

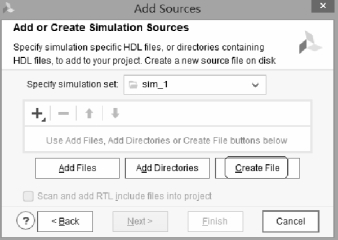

(2)在图2.33 所示界面中选中“Add or create simulation sources”单击【Next】弹出创建文件选项对话框。

图2.33 选中添加仿真文件

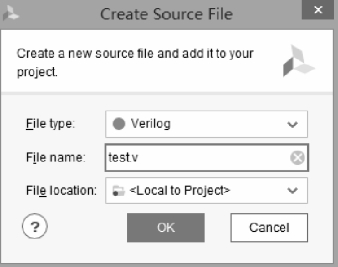

(3)在图2.34 所示界面中单击【Create File】选项,弹出如图2.35 所示的“Create Source File”对话框,在该对话框中设置仿真文件名,此处设置为“test.v”,然后单击【OK】。返回到图2.34 单击【Finish】,在随即弹出的“Define Module”对话框直接单击【OK】,再单击【Yes】按钮完成仿真激励文件的创建,此时在源文件管理窗口“Simulation Sources(1)”菜单下多了刚刚创建的“test.v”源文件。

图2.34 选择“Create File”(https://www.xing528.com)

图2.35 设置仿真文件名

(4)编辑仿真激励文件。

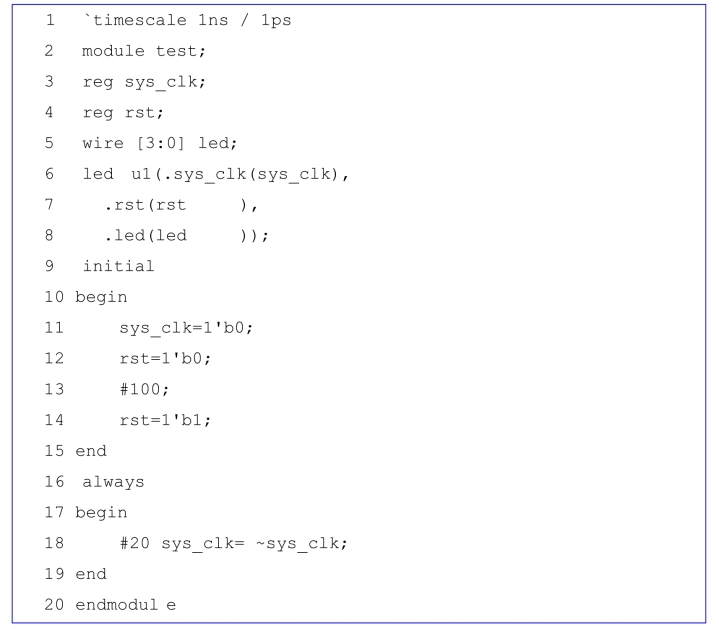

在“Sources”源文件管理窗口中,找到并双击“test.v”文件,打开代码编辑器,参照【代码2.2】输入代码,并保存文件完成仿真文件添加。

【代码2.2】test 仿真激励测试文件

(5)运行仿真及观察结果。

在Vivado 左侧的“Flow Navigator”项目设计流程管理窗口,找到【SIMULATION】→【Run Simulation】并单击,在弹出的子菜单中选择【Run Behavioral Simulation】运行仿真,如图2.36 所示。仿真结果如图2.37 所示,运用仿真工具操作观察各信号变化是否符合设计逻辑。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。