在VIVADO环境里新建一个项目工程,命名为“ddr3_test”。在VIVADO左边界面“Project Manager”选项下,点击“IP Catalog”,在打开的IP核管理工具中,找到【Memories & Storage Elements】→【Memory Interface Generators】→【Memory Interface Generator(MIG 7 Series)】,如图5.16所示。

图5.16 Memory Interface Generate(MIG 7 Series)

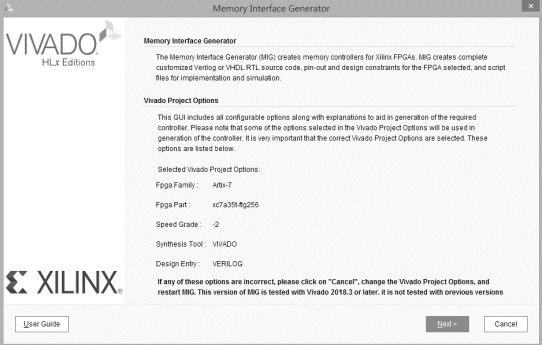

也可以在搜索栏输入“MIG”快速查找。双击“Memory Interface Generate(MIG 7 Series)”,进入DDR IP核配置界面,如图5.17所示。点击“Next”按钮,进入下一步。

图5.17 MIG工具界面

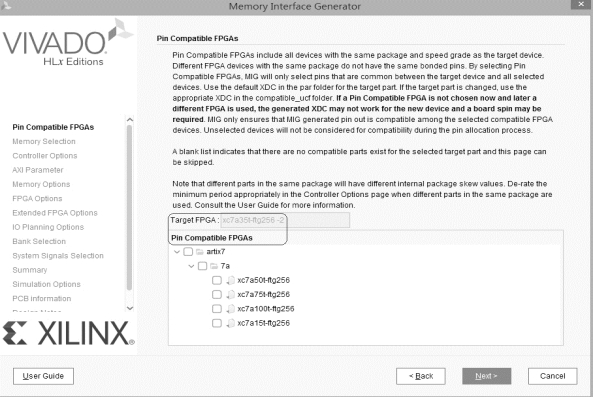

在如图5.18所示的界面中,修改“Component Name”为“DDR3”,然后点击“Next”按钮,进入下一配置界面,选择目标FPGA芯片型号,然后单击“Next”按钮,如图5.19所示。

图5.18 修改Component Name

图5.19 选择目标FPGA芯片型号

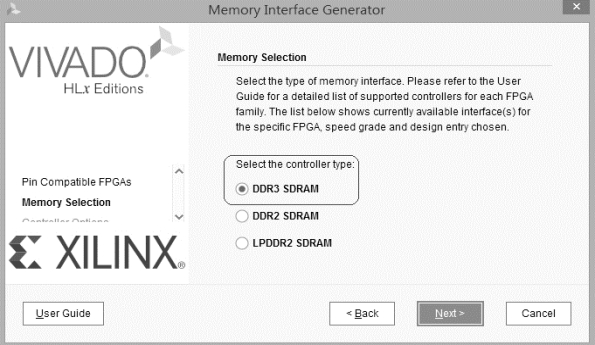

在图5.20所示界面中,选择默认的控制器类型为“DDR3 SDRAM”,单击“Next”按钮,进入下一步。

图5.20 选择控制器类型

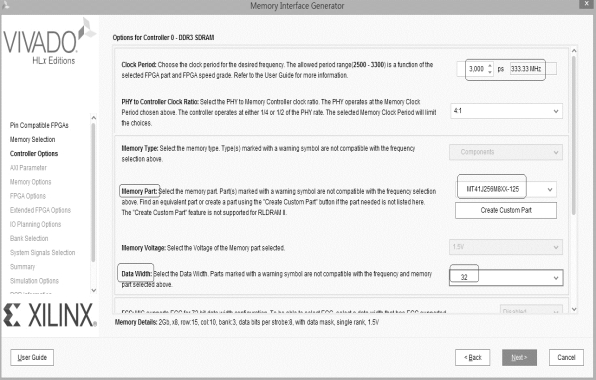

在图5.21所示Controller Options界面中,设置时钟周期参数,这里的频率选择是3000-3300ps。这个时钟有两层含义,一是表示DDR芯片的工作频率,二是表示IP CORE的参考时钟。在“Memory Part”选项中,用户可以选择开发板上对应的DDR3型号;“Creat Custom Part”表示如果没有找到开发权上对应的DDR型号,用户可以自己创建,但是需要的参数比较多。数据宽度“Data Width”选择“32”位;然后点击“Next”按钮进入下一步。

图5.21 Controller Options选项界面(https://www.xing528.com)

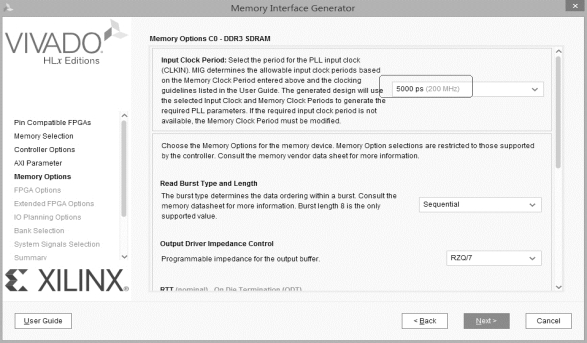

在图5.22所示界面中,选择PLL输入时钟的频率“Input Clock Period”为“200MHz”(这个时钟需要与开发板上的时钟频率一致),点击“Next”按钮,进入下一步。

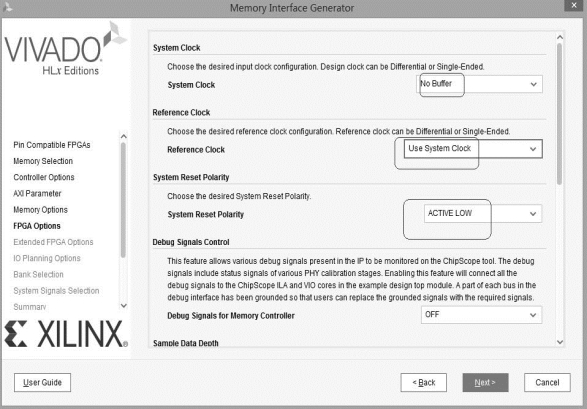

接下来进入FPGA Option时钟界面设置。在“System Clock”选项选择差分“No Buffer”;在“Reference Clock”选项中,因为开发板上没有提供单独的DDR参考时钟,所以选择“Use System Clock”;在“System Reset Polarity”选项选择“ACTIVE LOW”,点击“Next”按钮进入下一步,如图5.23所示。

图5.22 配置输入PLL时钟

图5.23 FPGA Options时钟选项

在图5.24所示的界面中,“Internal Termination ImPedance”选项中High Range Banks 的内部端接阻抗,这里选择默认的“50 Ohms”。点击“Next”按钮进入下一步。

图5.24 Internal Termination ImPedance选项

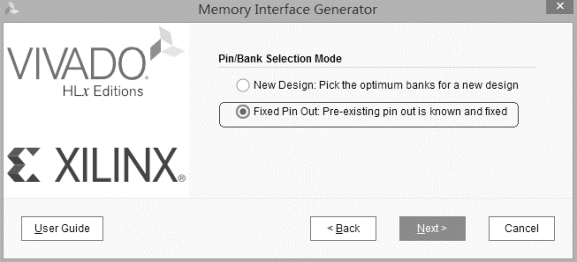

在图5.25所示界面中,选择第二项,设定DDR的管脚,然后点击“Next”按钮,进入下一步。

图5.25 DDR管脚设置

在图5.26所示界面中,设置DDR3的数据、地址和控制信号的FPGA管脚分配和IO电平。如果是手工分配比较麻烦,此时可以点击“Read XDC/UCF”直接导入管脚分配文件(.ucf文件)。在本例程中已经准备好了一个DDR3.ucf文件,只要直接导入这个.ucf文件就可以完成ddr3的管脚分配。接着再点击“Validate”进行验证,通过后点击“Next”按钮。

图5.26 导入.ucf管脚文件

接下来显示的是DDR3 IP核配置的整体情况,检查一下是否存在问题,没有问题就点击“Next”按钮。接下来选择“Accept”,点击“Next”。接下来选择“Generate”生成MIG控制器。MIG会生成example_ design和user_design两个文件夹以及相关文件,生成设计后,MIG GUI关闭。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。