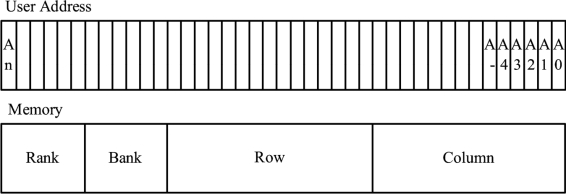

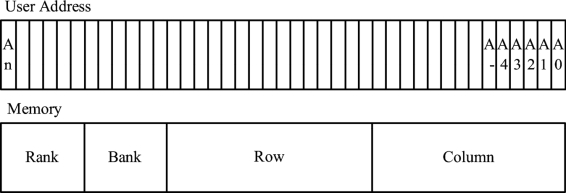

用户接口地址总线与物理层存储器件地址(Row、Bank、Column)间的映射关系是可配置的。根据应用数据的组织方式,可选择Bank-Row-Column或Row- Bank-Column地址映射方案使控制器效率达到最优。具体地址映射方案如图5.10和图5.11所示。

图5.10 Bank-Row-Column模式下的存储器地址映射方案

图5.11 Row-Bank-Column模式下的存储器地址映射方案

1.命令路径

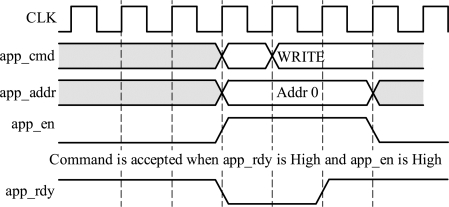

当用户发出的app_en信号和UI发出的app_rdy信号有效时,UI接收命令并写入FIFO;当app_rdy无效时,UI忽略用户发送的命令,用户逻辑需要继续保持接口信号且使app_en高有效,直到app_rdy信号有效为止,如图5.12所示。

图5.12 app_ rdy有效时的UI命令时序图

2.写路径

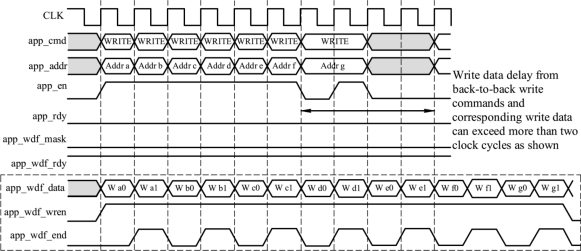

如图5.13所示,当app_ wdf_ wren和app_ wdf_ rdy 高有效时,表明写数据已进入写FIFO中。当app_ wdf_ rdy 无效时,用户逻辑需要一直保持app_ wdf_ wren和app_ wdf_ end为高,以及保持app_ wdf_data 数据有效直到app_ wdf_rdy 信号置为有效为止。app_ wdf_mask信号用作外部存储器的字节掩码。(https://www.xing528.com)

图5.13 app_ wdf_rdy有效时的UI写时序图

单个写操作时,写命令和写数据之间的延时最大不能超过2个时钟周期,如图5.12所示。背靠背(Back-to-Back)写操作时,写命令和写数据之间没有最大延时的限制,如图5.14所示。

图5.14 UI背靠背写命令时序图(Burst Type=BL8)

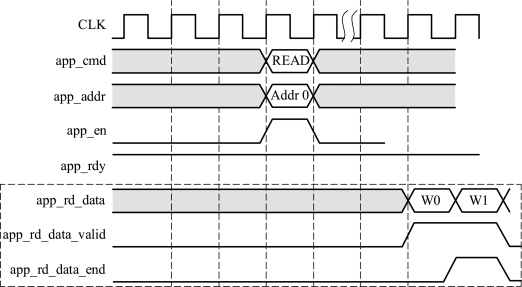

3.读路径

如图5.15所示,读数据按照请求的顺序通过用户接口(UI)并返回,当app_ rd_data_ valid 信号有效时,读数据有效。app_ rd_ data_ end信号用于指示读突发操作的结束,但在用户逻辑中该信号不是必需的。

图5.15 UI读时序图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。