PHY模块为外部DDR2/DDR3 SDRAM提供物理接口,用于产生时钟、地址、控制逻辑、读/写数据通路和上电后SDRAM存储器的初始化状态逻辑。此外,PHY模块也包括校准逻辑,用于执行解决系统静态及动态时延问题的读/写数据通路时序训练等。

MIG工具为DDR3SDRAM的PHY提供了一个单独的HDL代码库,通过文件顶层的HDL参数和UCF文件中的约束可以定制SDRAM类型和大量的设计参数。PHY模块结构如图5.6所示。

图5.6 PHY模块结构框图

1.初始化顺序

系统复位后,PHY执行存储器要求的上电初始化操作,之后进行数个阶段的读/写数据路径时序校准。校准完成后,PHY发出初始化完成指示,这时MC模块才可以对存储器进行正常的读/写操作。PHY初始化顺序如图5.7所示。

图5.7 PHY初始化顺序

2.时钟结构

PHY要求MMCM模块产生多种不同的时钟,并且所有全局时钟和区域时钟网络均分布在整个设计中。PHY模块中的时钟产生、电路分布和网络驱动模块可以大致分为以下4部分:

内部(FPGA)逻辑;

写数据通路(输出)I/O逻辑;

读数据通路(输入)及时延I/O逻辑,以及读数据同步逻辑;

IODELAY参考时钟(200 MHz或300 MHz)。

PHY模块需要一个MMCM。就一般功能而言,MMCM产生的时钟会驱动大部分的内部逻辑、写数据通路I/O逻辑、读数据捕获及时钟同步。

如果系统时钟是存储器时钟的1/2,则example_top模块的参数设置如下:

CLKFBOUT_ MULT_ F=8;

DIVCLK_ DIVIDE=2;

CLKOUT DIVIDE=2。

如果系统时钟与存储器时钟的频率相同,则example_top模块的参数设置如下:

CLKFBOUT_ MULT_ F=8;

DIVCLK_ DIVIDE=4;

CLKOUT DIVIDE=2。(https://www.xing528.com)

一个200 MHz或300 MHz的IODELAY时钟(取决于IODELAY Tap的分辨率)必须提供给IDELAYCTRL模块,IDELAYCTRL模块根据外部环境的变化在I/O域中不断调整IODELAY单元。当前IP核认为IDELAYCTRL模块由外部时钟信号驱动,如果一个PLL时钟驱动IDELAYCTRL模块的输入时钟,则PLL的锁定信号必须与IODELAY_CTRL.v/vhd的rst_ tmp_ idelay 信号合并,以确保时钟在使用之前已经稳定。

3.I/O结构

每一个I/O Block 的逻辑中包含了支持读/写平衡要求的电路,并且每一个I/O Block的3个元素(ISERDES、OSERDES及IODEALY)也增加了新的特点。

4.存储器初始化

系统复位后,PHY可完成符合JEDEC标准的初始化序列。通过模式寄存器设置命令(MRS)可以访问DDR2/DDR3 SDRAM中一系列的模式寄存器。这些模式寄存器决定了SDRAM的性能状态,如突发长度及类型、读/写CAS时延及附加时延等,具体配置信息由顶层的HDL参数决定。

5.写数据通路

1)写平衡

DDR3 SDRAM模块在时钟、地址、命令及控制信号上采用了“fly-by”拓扑结构以提高信号的完整性。这些信号以菊花链(Daisy-Chained)的形式连接,在每一个路径的末端终止。但是这造成了存储设备中DQS信号和时钟(CK)之间的不一致。DDR3SDRAM的一个新特点是支持写平衡,写平衡允许控制器根据CK独立地调整每一个写DQS的相位。这种调整补偿了DQS和CK之间的歪斜,使其满足tDQSS规范要求。在写平衡期间,DQS信号由FPGA存储器接口驱动,DQ信号由DDR3 SDRAM驱动以提供反馈。FPGA 存储器接口应有能力调整DQS信号延迟,直到在DQ信号上检测到0-1跳变。

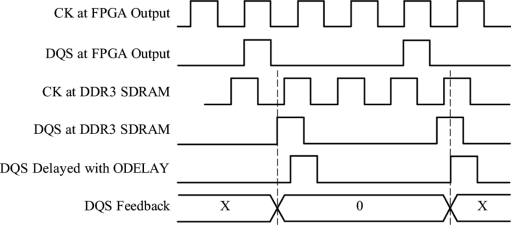

写平衡模块框图如图5.8所示,FPGA 存储器接口驱动的DQS信号用作D触发器的时钟信号,而时钟CK为该D触发器的数据输入信号。该D触发器的输出信号通过DQ作为一个反馈回传给FPGA存储器接口。如果DQ上的电平为0,则延时DQS信号直到检测到DQ信号为1。

写平衡的时序图如图5.9所示,FPGA存储器接口输出DQS脉冲信号用于检测DDR3 SDRAM的CK信号。DQS脉冲信号的最少间隔为16个时钟周期。采用增加IODELAY的Tap值来实现DQS的时延,直到检测到反馈DQ输入信号上有0-1跳变为止。通过写平衡建立的DQS延时可以确保满足tposs规范要求。

图5.8 写平衡模块框图

图5.9 写平衡时序图

2)写校准

写校准用于DQS和DQ信号与时钟信号CK的对齐,以补偿PCB路径和I/O缓冲器的时延。校准操作通过读/写特定数据来验证其能否被正确地写入存储器。在写校准期间,适当的时钟时延被添加,直到期望的数据格式被读返回。这个校准过程以字节为基本操作单位,在写校准时,该过程只有在“fly-by”拓扑被使用时,才会在DDR3 SDRAM上执行。

6.物理接口信号

PHY模块通过物理层接口与外部DDR3 SDRAM器件连接,信号描述如表5.4所示。

表5.4 DDR3 SDRAM引脚信号

续表

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。