【摘要】:CIC IP核的接口在Verilog HDL中进行设计时,一定要参考官方文档中给出的时序图。也可以在Xilinx官网或DocNav工具中搜索“pg140”,查阅CIC IP核的说明。将CIC IP核配置为3级CIC滤波器的级联,对输入数据进行5倍抽取。CIC IP核应用代码程序中认为输入的采样数据始终有效,因此将s_axis_data_tvalid永远置1。为了能将IP核的仿真结果与Verilog HDL的设计仿真结果进行对比,此处使用CIC滤波器对0.25 MHz+7.5 MHz的正弦混合信号滤波,在VIVADO中进行仿真,结果如图4.26所示。

CIC IP核的接口在Verilog HDL中进行设计时,一定要参考官方文档中给出的时序图。在IP核的配置界面点击“documentation”,可以找到IP核的“user guide”。也可以在Xilinx官网或DocNav工具中搜索“pg140”,查阅CIC IP核的说明。

将CIC IP核配置为3级CIC滤波器的级联,对输入数据进行5倍抽取。单通道、固定倍数的CIC接口时序非常简单,Verilog HDL示例见【代码4-5】。

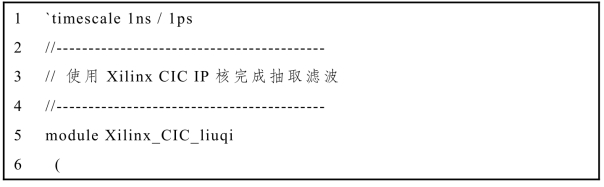

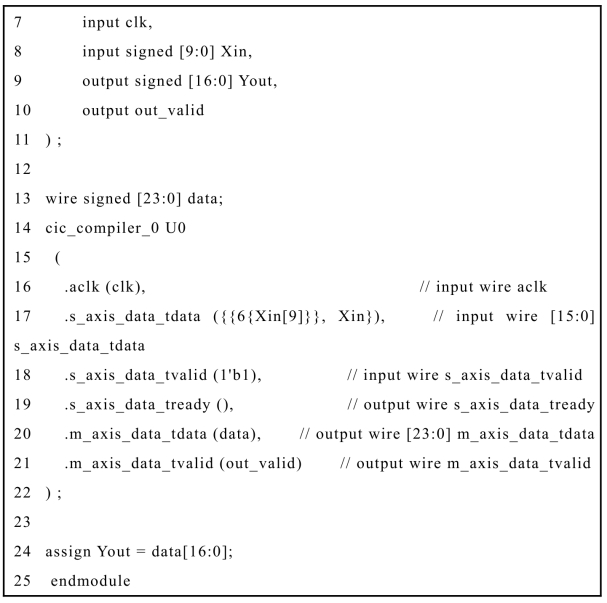

【代码4-5】CIC IP核应用代码

(https://www.xing528.com)

(https://www.xing528.com)

程序中认为输入的采样数据始终有效,因此将s_axis_data_tvalid永远置1。由于s_axis_data_tdata为16 b位宽,但输入信号数据为10 b位宽,因此用拼接运算符{}在高位填充符号位;由于m_axis_data_tdata为24 b位宽,但输出信号数据有效位仅有17 b位宽,因此仅需取低17 b作为CIC滤波器的输出。当然不这样操作,直接将信号赋值到实例化接口,结果也是正确的,这样做只是为了更严谨。

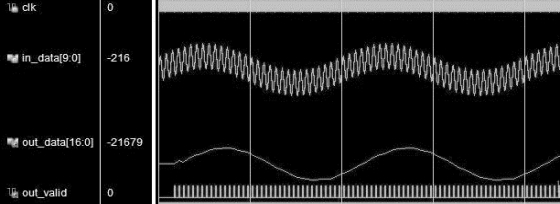

为了能将IP核的仿真结果与Verilog HDL的设计仿真结果进行对比,此处使用CIC滤波器对0.25 MHz+7.5 MHz的正弦混合信号滤波,在VIVADO中进行仿真,结果如图4.26所示。可以看到经过抽取滤波后,0.25 MHz的信号分量数据速率降低,但信号频率没有改变。而7.5 MHz的信号分量被抗混叠滤波器滤除,结果符合预期。

图4.26 仿真波形

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。