在VIVADO左侧的“Flow Navigator”项目设计流程管理窗口中,左键单击“IP Catalog”(IP目录),随即弹出“IP Catalog”对话框IP库资源界面,在搜索框中输入“CIC Compiler”或者选择【Digital Signal Processing】→【Filters】→【CIC Compiler】,如图4.22所示。

图4.22 CIC IP核存储位置

双击IP Catalog中“CIC Compiler”,打开CIC Compiler 4.0主界面,如图4.23所示。

图4.23 CIC Compiler主界面

主界面左边的选项卡组可以切换看到CIC的模块图(IP Symbol)、频率响应(Frequency Response)等信息;右边的选项卡组是对CIC滤波器进行设计。CIC Compiler管脚结构如图4.24所示。

图4.24 CIC Compiler管脚图

在“Filter Options”选项卡(见图4.23)中,主要设置以下参数:

Filter Type:设置CIC滤波器模式为抽取(Decimation)或插值(Interpolation);(https://www.xing528.com)

Number Of Stages:设置级联的CIC滤波器级数。

Differential Delay:设置差分延时(该值与输出数据位宽有关)。

VIVADO的CIC IP核也支持多通道模式,可以在“Number Of Channels”中设置数;此外还支持抽取/内插倍数的动态配置,采样率可选择固定模式和可编程模式,此处选用固定5倍。

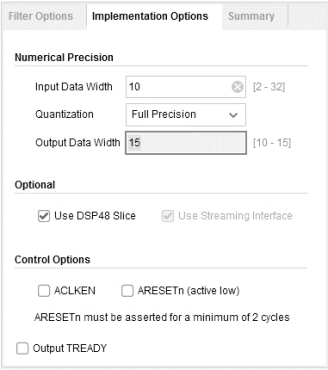

然后切换到“Implementation Options”标签卡,如图4.25所示。主要设置以下参数:

图4.25 Implementation Options设置页

Input Data Width:设置CIC滤波器输入数据的位宽;

Quantization:设置输出数据的量化方式,可以选择全精度输出(Full Precision)或截断模式(Truncation),后者可以手动设置输出数据位宽。

该页面还可以设置是否使用DSP48单元,是否需要时钟使能信号(ACLKEN)、复位信号(ARESETn)和输出的TREADY信号。配置完成后可以在Summary选项卡中看到IP核的具体信息。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。