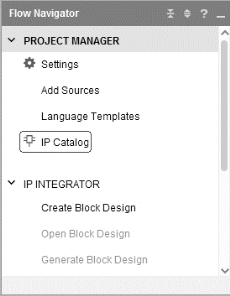

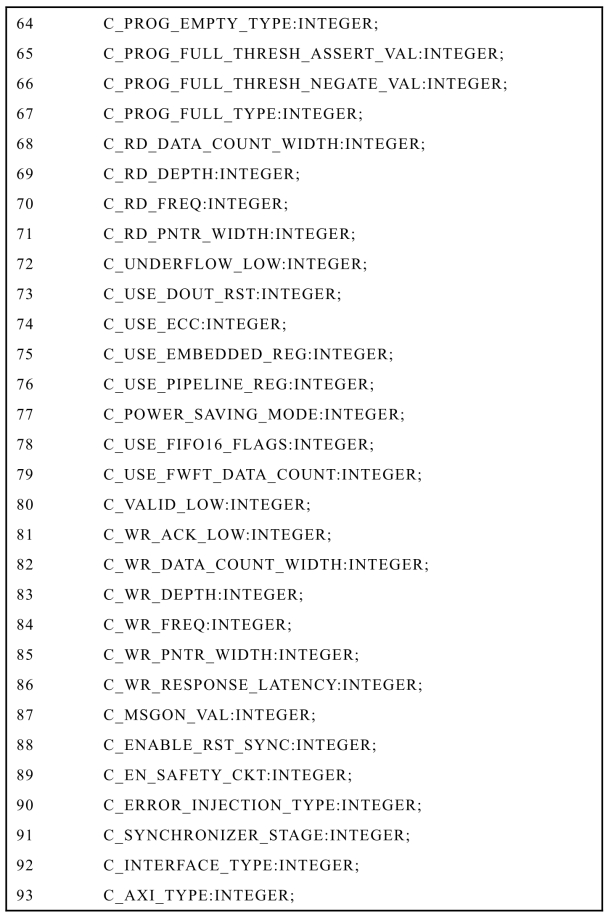

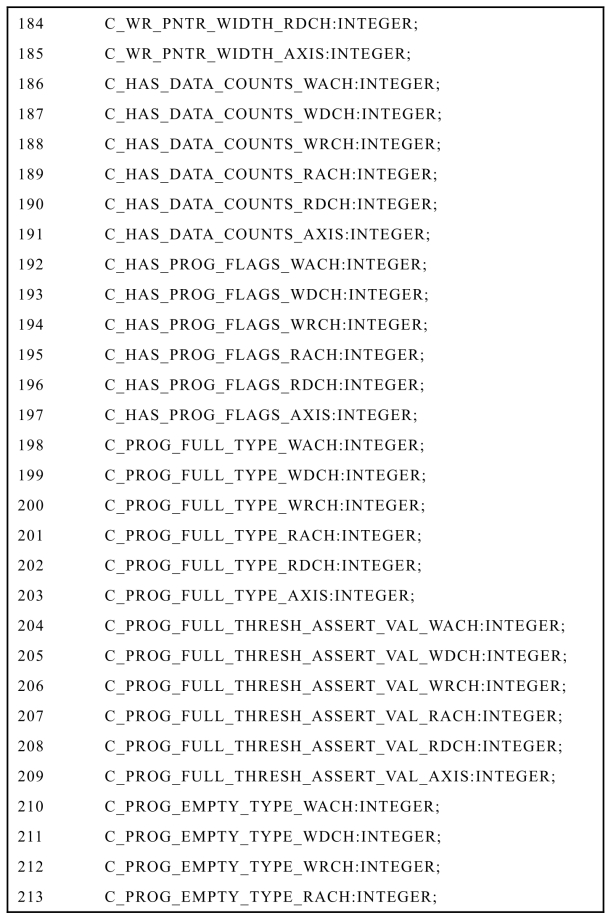

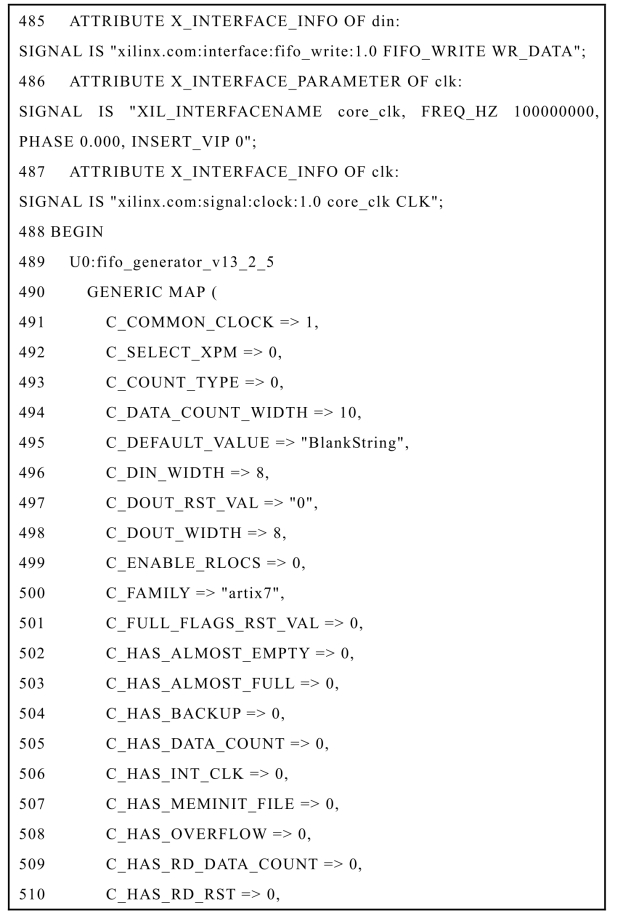

在VIVADO左侧的“Flow Navigator”项目设计流程管理窗口中(见图3.35),左键单击【IP Catalog】(IP目录),随即弹出“IP Catalog”对话框IP库资源界面。

图3.35 Flow Navigator工程管理器窗口

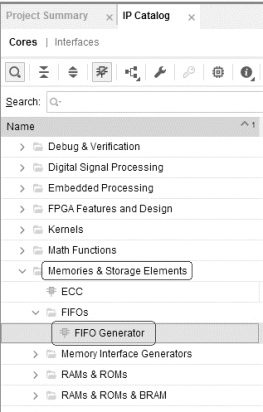

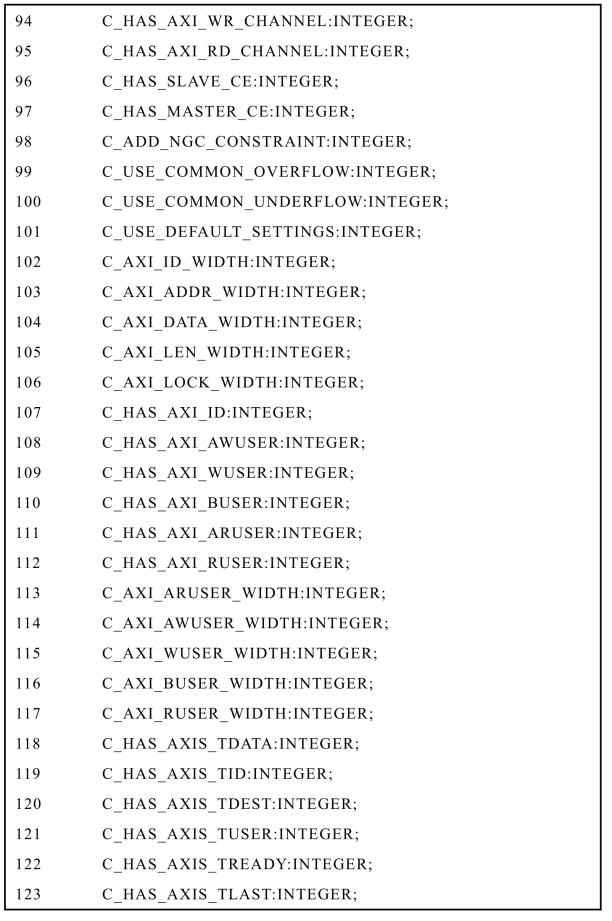

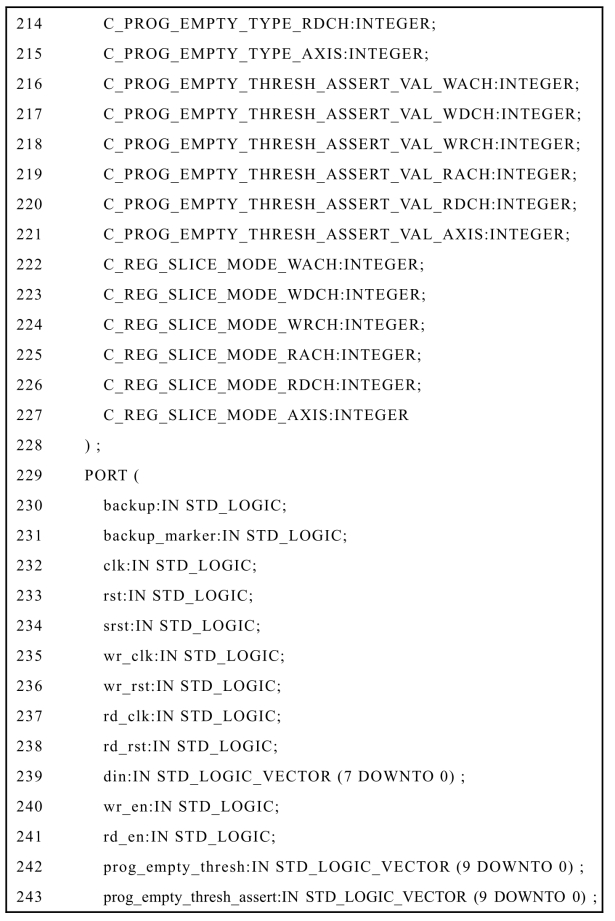

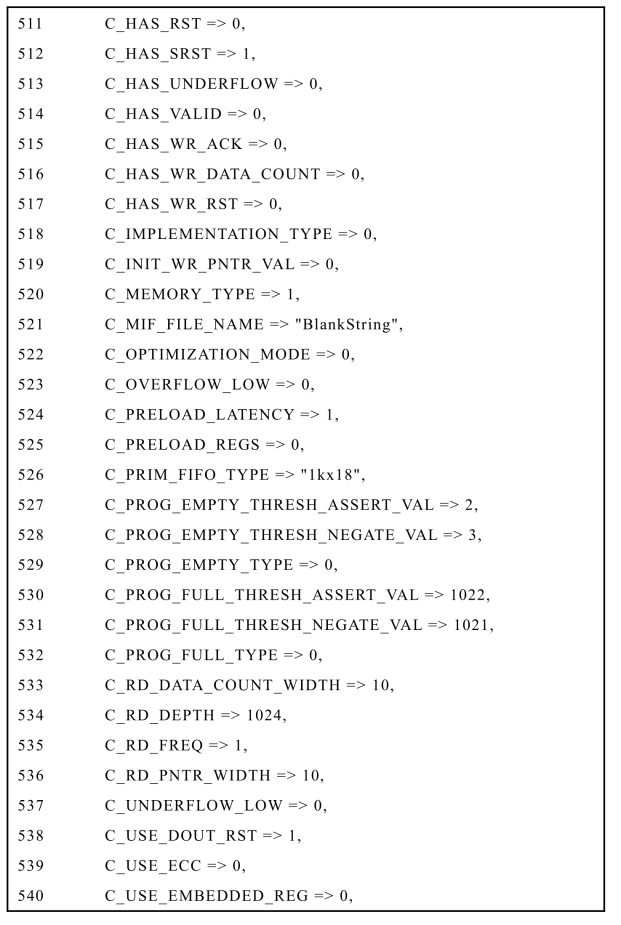

在IP库资源界面点击【Memories & Storage Elements】→【FIFOs】→【FIFO Generator】,如图3.36所示。

图3.36 FIFO IP核位置

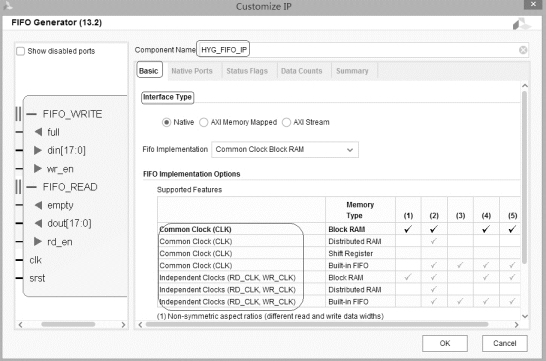

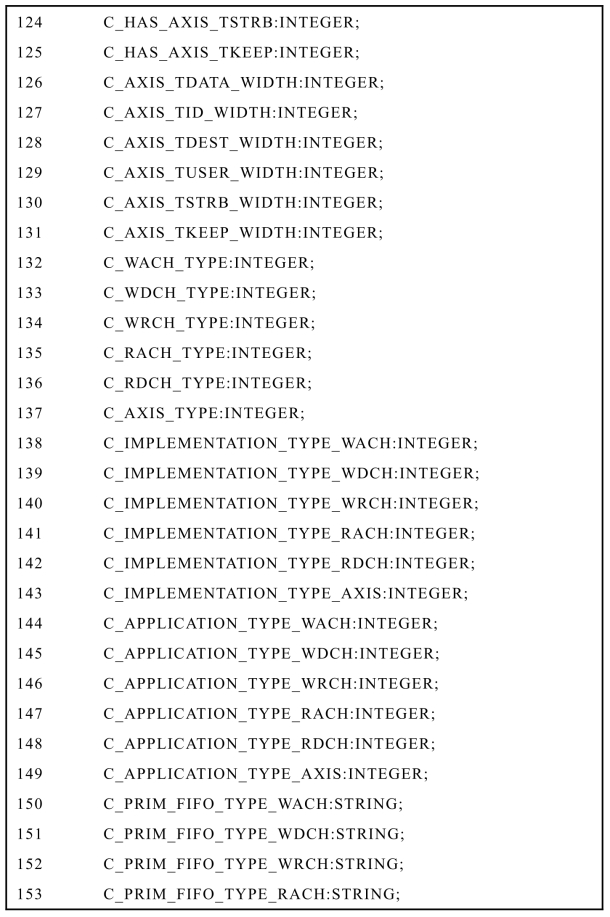

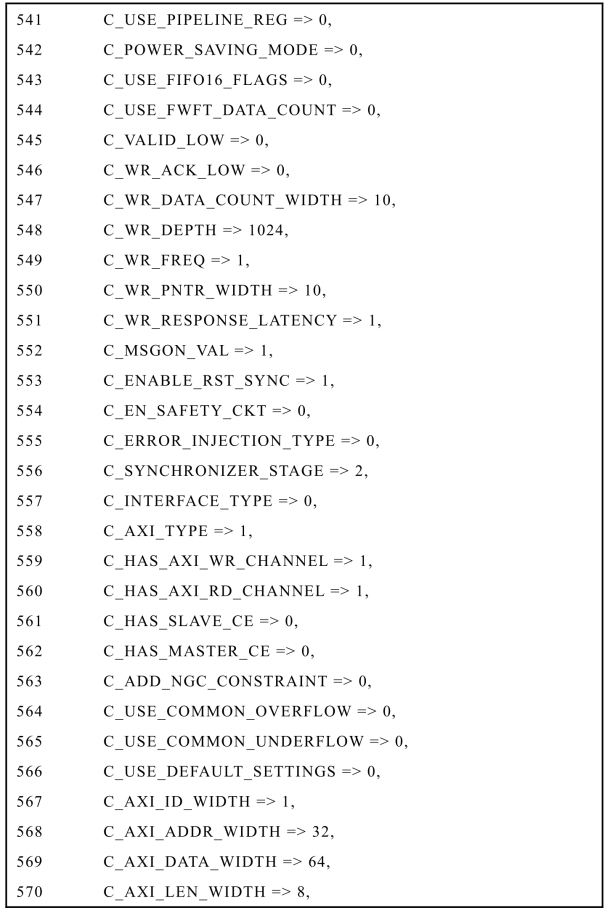

在图3.37所示配置界面中,“Component Name”用于设置例化IP核的名字;Basic选项卡主要设置FIFO支持的接口类型。

图3.37 Basic配置界面

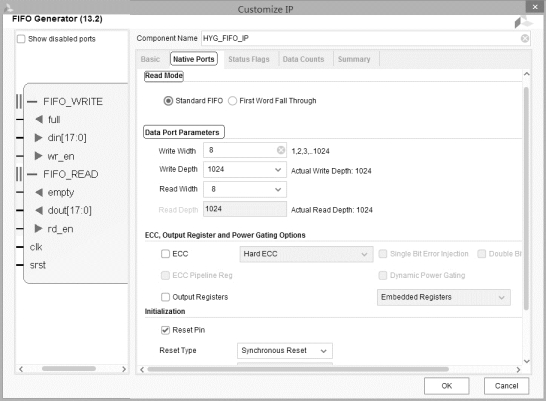

图3.38 Native Ports界面

在图3.38所示配置界面中,有两个标签需要配置:Read Mode(读模式)和Data Port Parameters(端口参数)。

在Read Mode中:

Standard FIFO(标准FIFO):FIFO的读数据延迟读请求一个时钟周期输出;

First word fall through:FIFO的读数据在读请求的同一个时钟周期内输出。

在Data Port Parameters中点击“OK”按钮进入下一步,可以设置读取深度和读取宽度等信息。

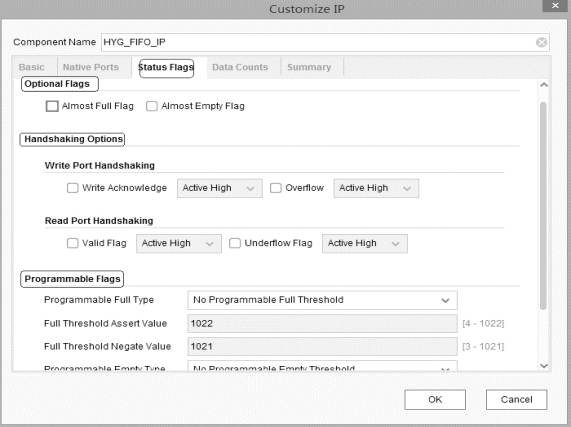

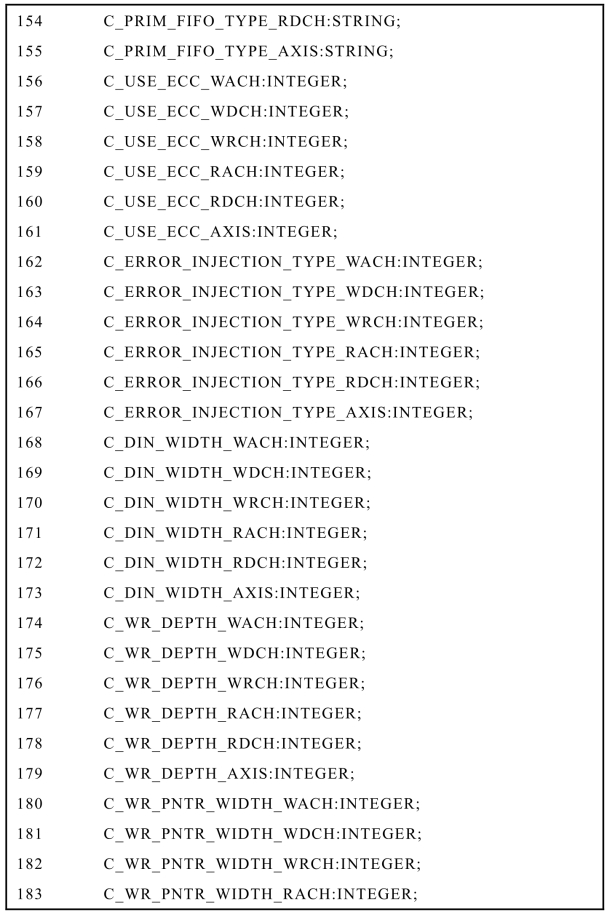

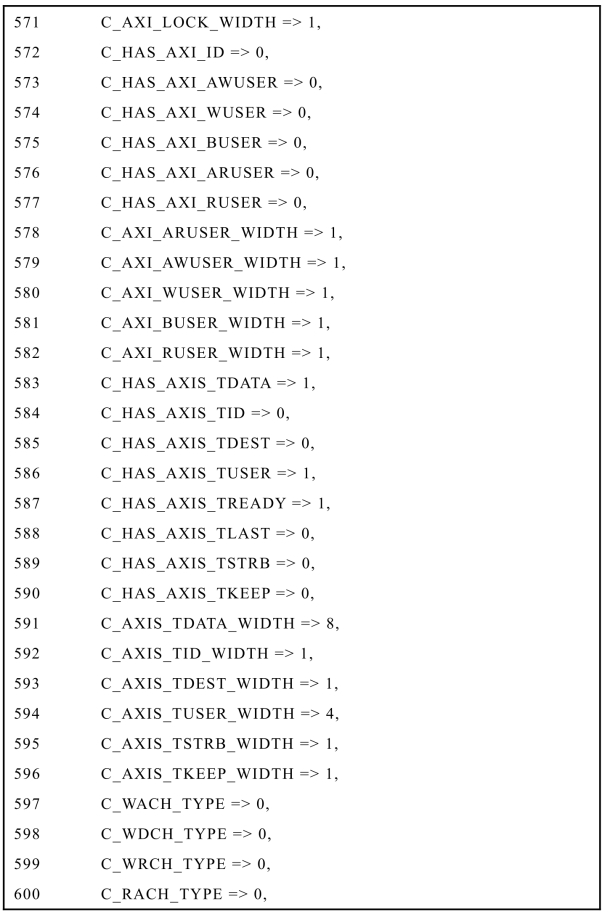

图3.39 Status Flags设置界面

接下来对图3.39所示配置界面进行介绍。

在Optional flags栏中:

Almost FULL flag(几乎满了标志位):表示FIFO里存的数据还差一个就满了;

Almost Empty Flag(几乎空了标志位):表示FIFO里面存的数据只剩一个了。

在Write Port Handshaking 栏中:

Write Acknowledge:表示一次成功的写操作标志位;

Overflow Flag:表示一次无效的写操作标志位(溢出了)。

在“Read Port Handshaking”栏中:

Valid Flag:表示该端口的数据是有效的;

Underflow Flag:表示一次无效的读操作标志位。

在“Programmable Full Type”栏中:

No Programmable Full Threshold”:不设置可编程溢出阈值;

Single Programmable Full Threshold Constant:设置一个可编程溢出阈值常量;

Multiple Programmable Full Threshold Constant:设置多个可编程溢出阈值常量;

Single Programmable Full Threshold Input Port:在输入端口设置一个可编程溢出阈值;

Multiple Programmable Full Threshold Input Port:在输入端口设置多个可编程溢出阈值。

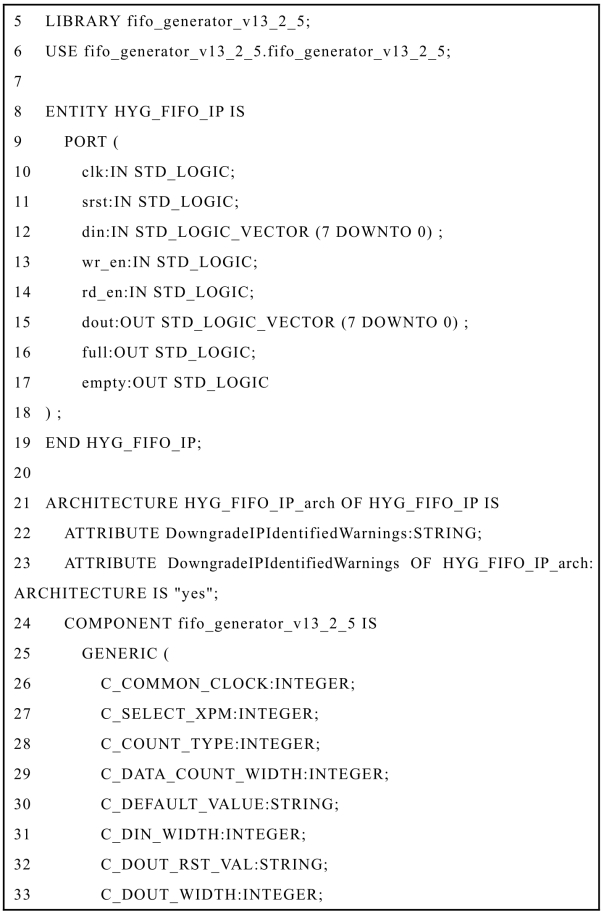

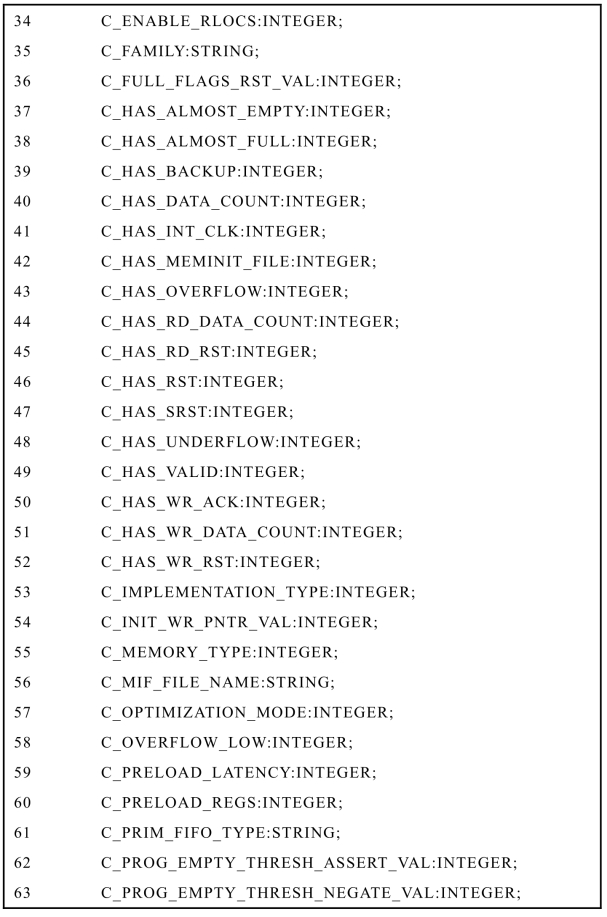

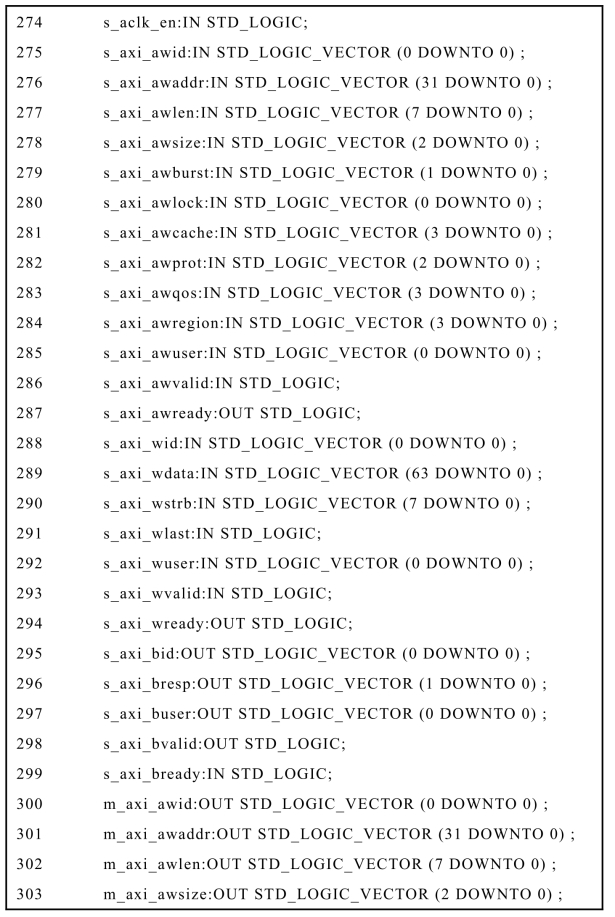

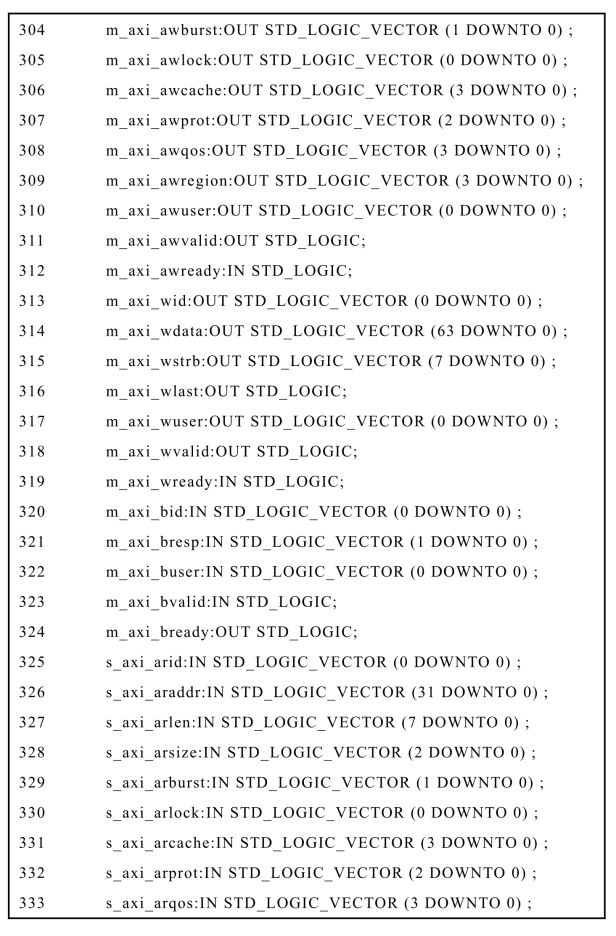

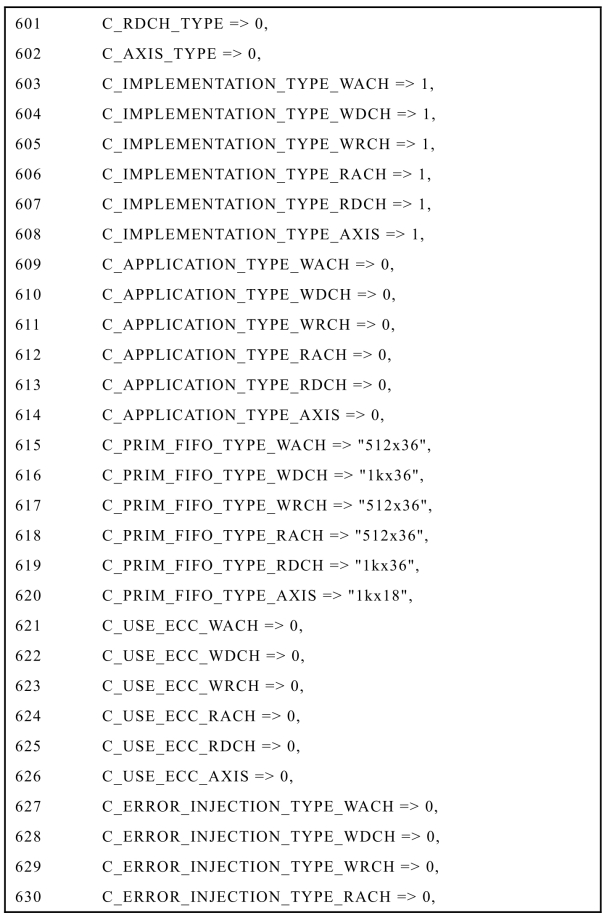

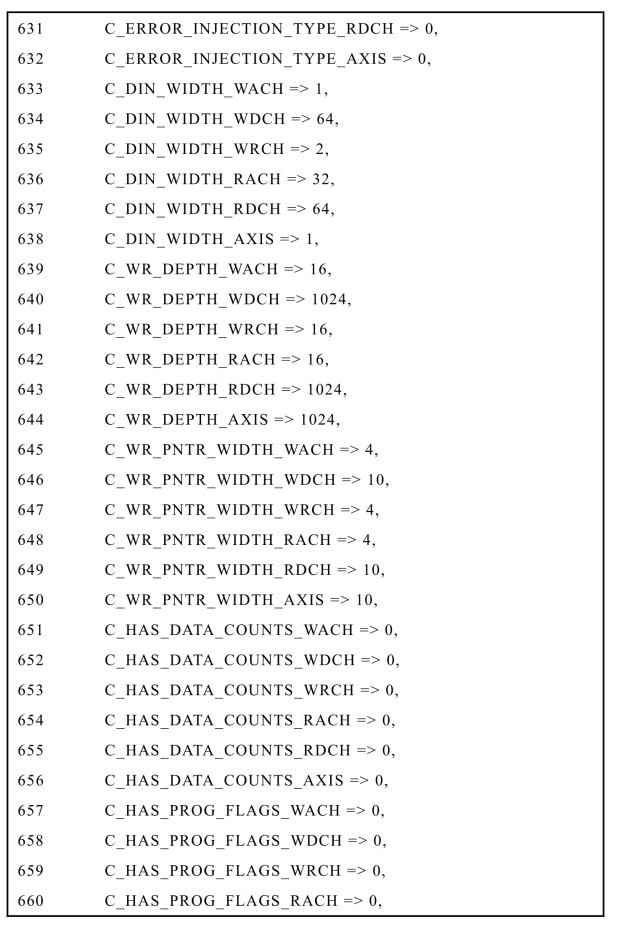

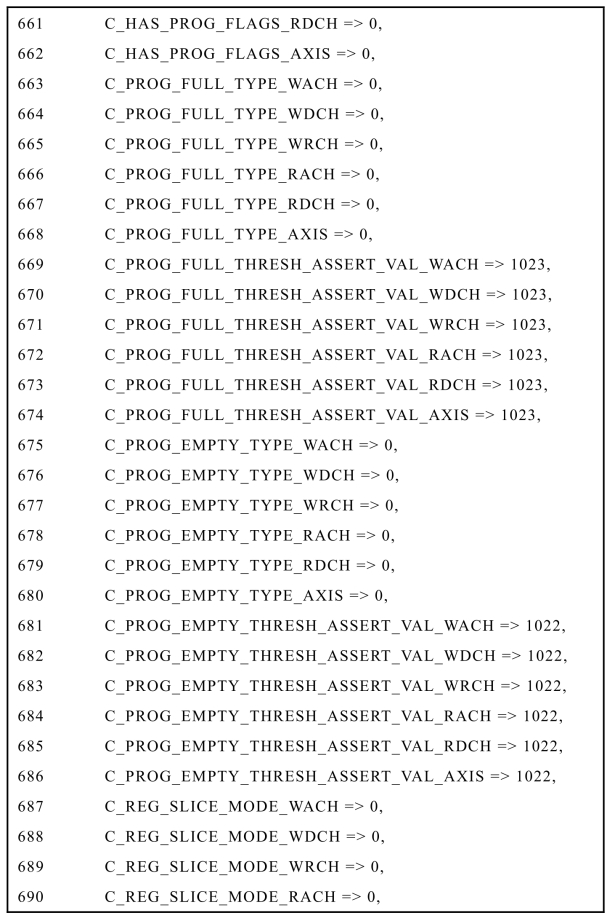

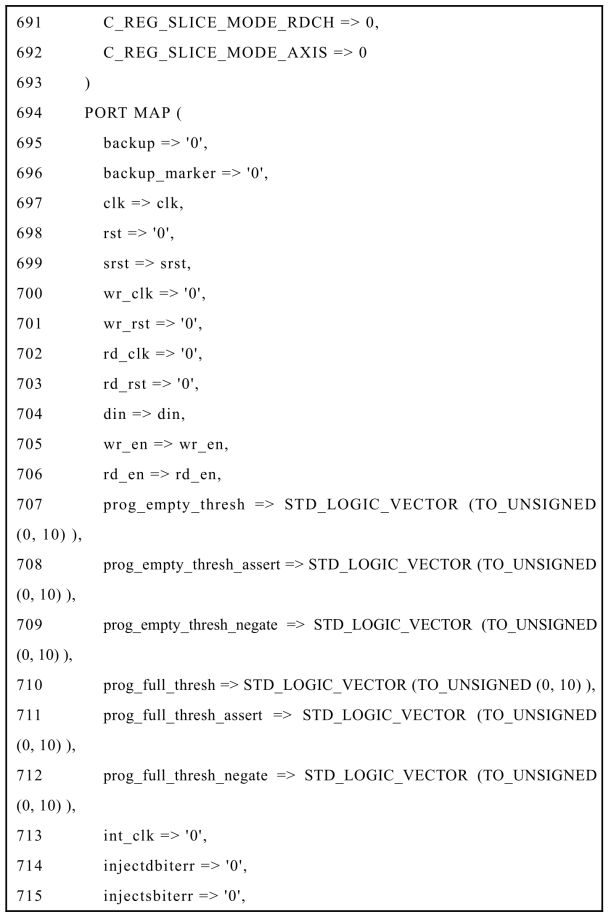

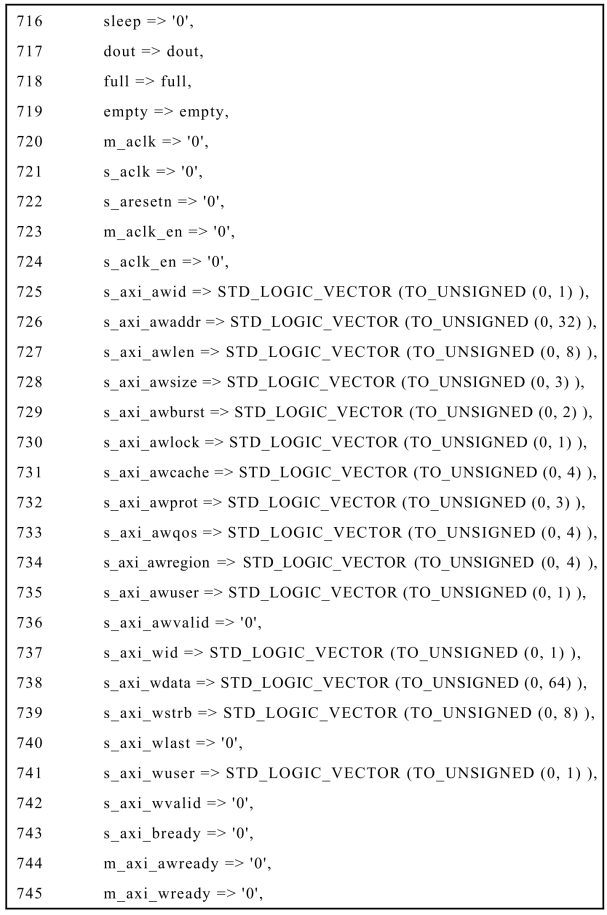

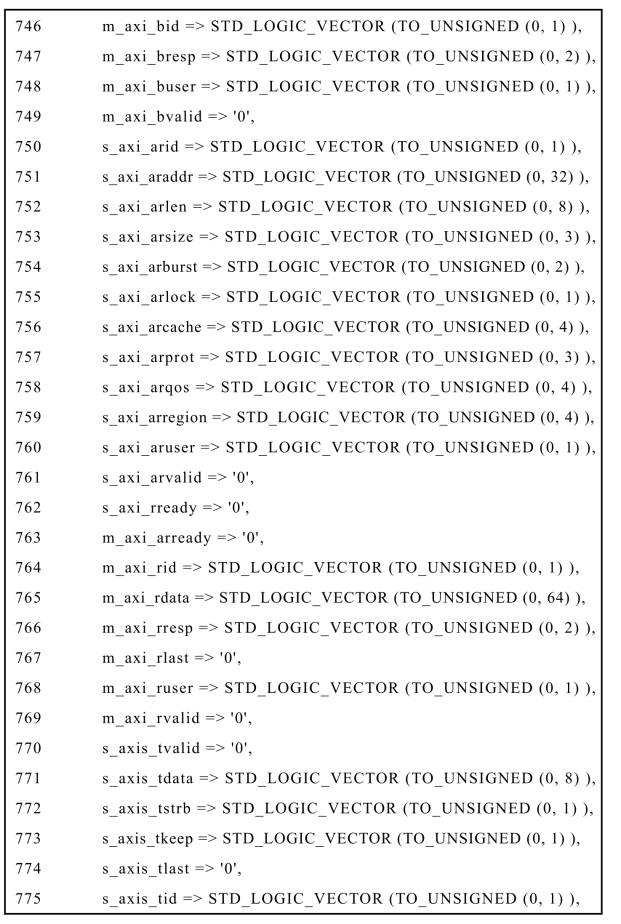

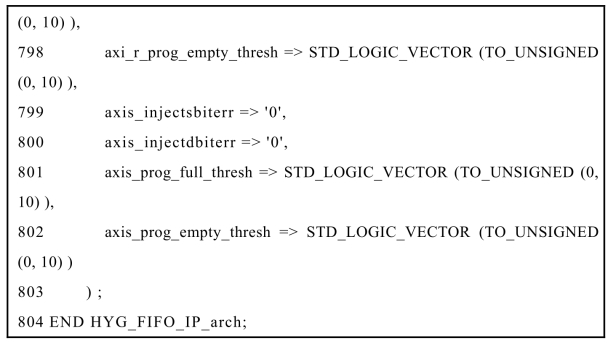

设置完后单击“OK”按钮,完成FIFO中核定制,生成源文件,见【代码3-8】。(https://www.xing528.com)

其实FIFO IP核和RAM IP核使用方法是差不多的。在RAM IP核中需要写使能、写数据、读使能、读数据以及时钟和地址,在FIFO IP核中则需要写使能、写数据、读使能、读数据、时钟、空表示、满表示以及数据计数等,如果去掉这些标志信号,那么可以发现FIFO IP核剩下的信号是和RAM IP核是一样的,唯一不同的是RAM IP核读写操作需要地址,而FIFO IP核不需要使用地址,只要使能信号打开并且时钟到来,数据就可以读出和写入,比RAM IP核使用起来更简单。

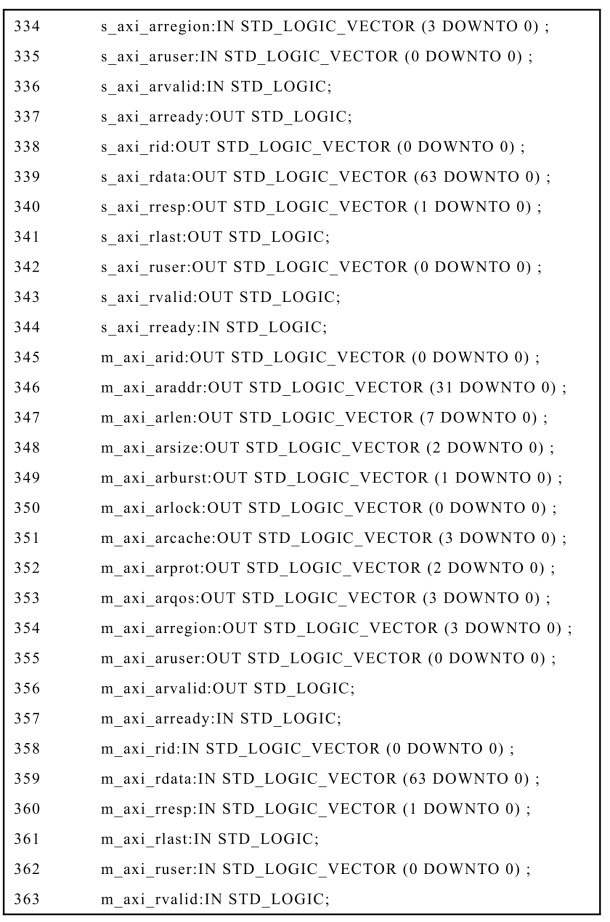

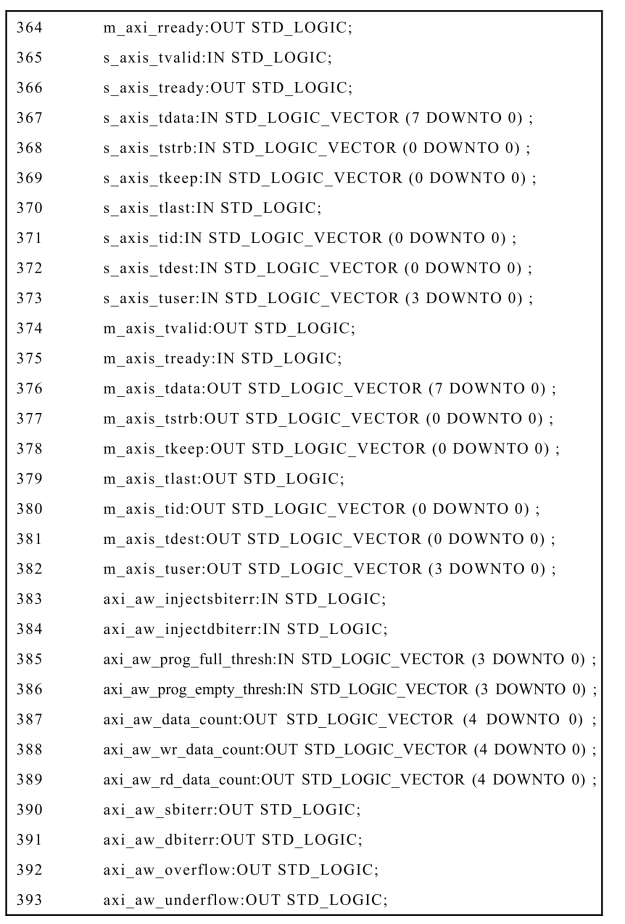

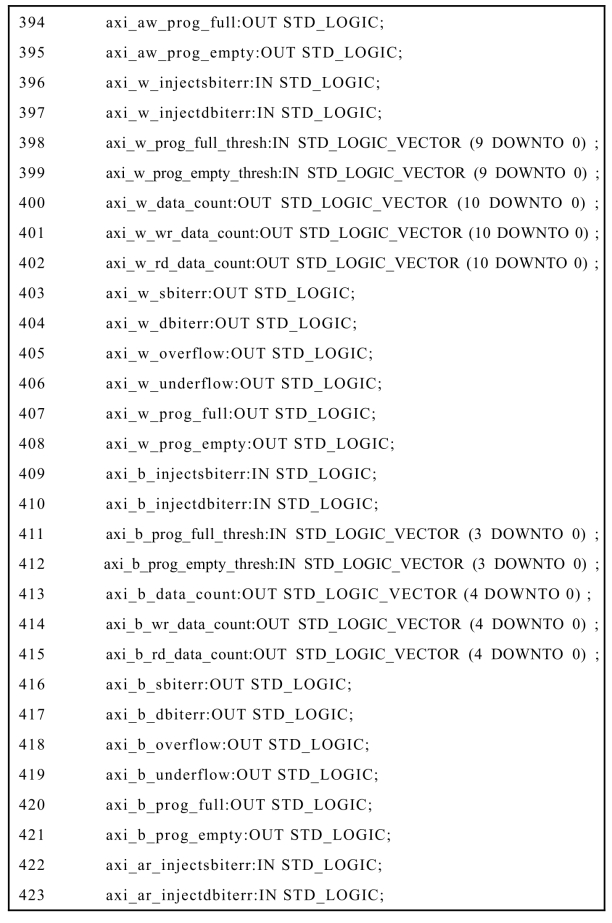

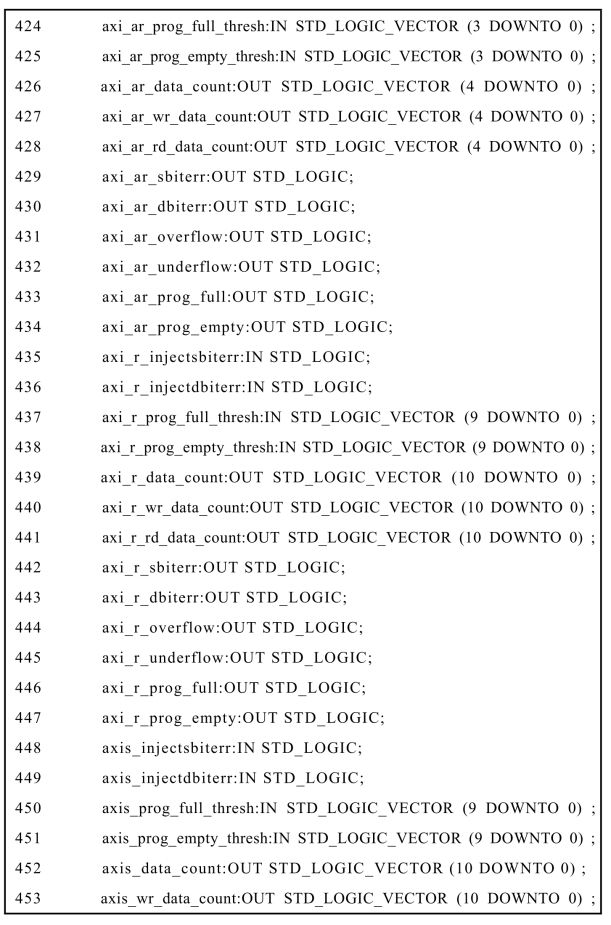

【代码3-8】FIFO IP核生成源文件代码

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。