随机存储器(RAM),可以随时从任一指定地址读出数据,也可以随时把数据写入任何指定的存储单元,且读写的速度与存储单元在存储芯片的位置无关,其主要用来存放程序及程序执行过程中产生的中间数据、运算结果等。RAM按照存储单元的工作原理可以分为静态RAM和动态RAM,也就是常说的SRAM和DRAM。

SRAM速度非常快,是目前读写最快的存储设备,比如CPU的一级缓冲,二级缓冲就采用了SRAM。而计算机内存就是DRAM,比SRAM价格低,但性能不如SRAM。这里要说明的是,DRAM与SRAM相比速度较慢,但是它与ROM相比较速度还是很快的。与ROM IP核一样,xilinx也提供了两种RAM IP:一种是单端口的RAM IP,另一种是双端口的

RAM IP。

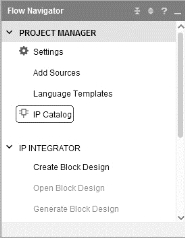

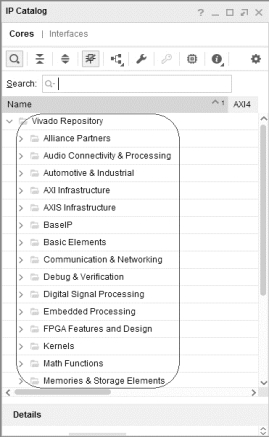

如图3.28所示,在VIVADO左侧的“Flow Navigator”项目设计流程管理窗口中,左键单击“IP Catalog”(IP目录),随即弹出“IP Catalog”对话框IP库资源界面,如图3.29所示。

图3.28 Flow Navigator工程管理器窗口

图3.29 IP资源库列表

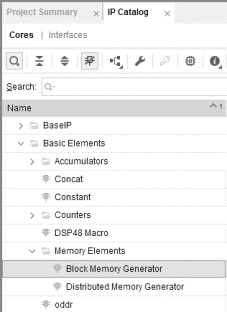

在IP资源库列表中单击【Basic Elements】→【Memory Elements】选项,展开如图3.30所示列表菜单选项,再单击“Block Memory Generator”,便可启动存储器IP核管理单元。

图3.30 存储器IP核的位置

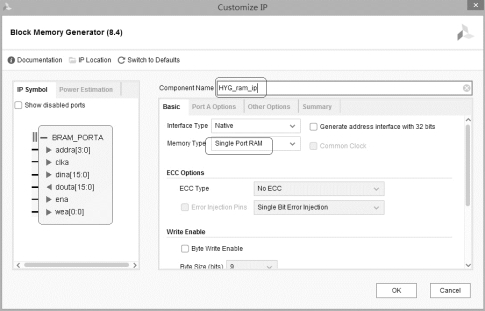

在图3.31所示的RAM IP核配置界面中,“Component Name”用于设置例化IP核的名字;“Memory Type”用于设置RAM的类型,有单端口RAM、双端口RAM和真双端口RAM三种类型。

图3.31 RAM IP核配置界面

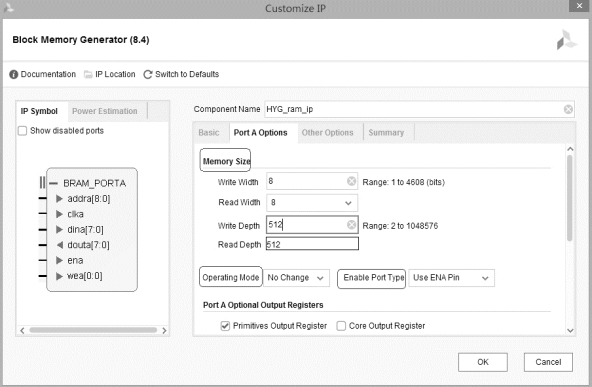

在图3.32所示页面中,有三个可供修改的标签:“Memory Size”(存储器大小)、“Operating Mode”(操作模式)和“Enable Port Type”(使能端口类型)。在“Memory Size”栏,我们可以配置存储器的“Read Width”(读数据的位宽)和“Read Depth”(读数据的深度)等。

在“Operating Mode”栏,可供选择的有“Write First”“Read First”和“No Change”,默认选择“Write First”。

“Write First”(先写模式):数据先写入RAM中,然后在下一个时钟输出该数据。

“Read First”(先读模式):数据先写入RAM中,同时输出内存中同地址的上一次数据。

“No Change”(无变化模式):读写分开操作,不能同时进行读写。

在“Enable Port Type”栏,我们可以选择使能信号为“Always Enable”(一直有效选择)或者“Use ENA Pin”(配置一个使能信号)。

“Port A Optional Output Resisters”(可选输出寄存器)中“Primitives Output Register”表示源于的输出端口A处增加寄存器级;“Core Output Register”表示在IP核的输出端口A处增加寄存器级。

图3.32 PORT A选项设置

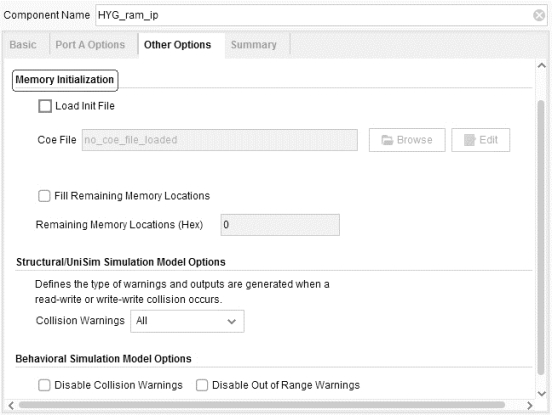

图3.33 RAM初始化(https://www.xing528.com)

在图3.33所示页面中,标签“memory Initialization”(存储器初始化)可以用来载入coe文件对ROM IP核进行初始化;在“File Remaining Memory Locations”(填补剩余的内存位置)选项可以将剩余内存填充上用户指定的数值。

标签“Structural/Unisim Simulation Model Options”用来定义警告的类型和当发生读-写或写-写冲突的输出,其中:

All:冲突检测特性将在模型中使能以处理任何情况下的冲突。

None:冲突检测特性将在模型中失能,冲突期间的行为将留给仿真软件处理。

Warning Only:仅仅显示警告。

Generate-X Only:仅仅产生-X。

标签“Behavioral Simulation Model Options”为行为仿真模型选项,其中:

Disable Collision Warnings:忽视读-写和写-写冲突的警告信息。

Disable Out of Range Warnings:“忽视超出范围的警告”信息。

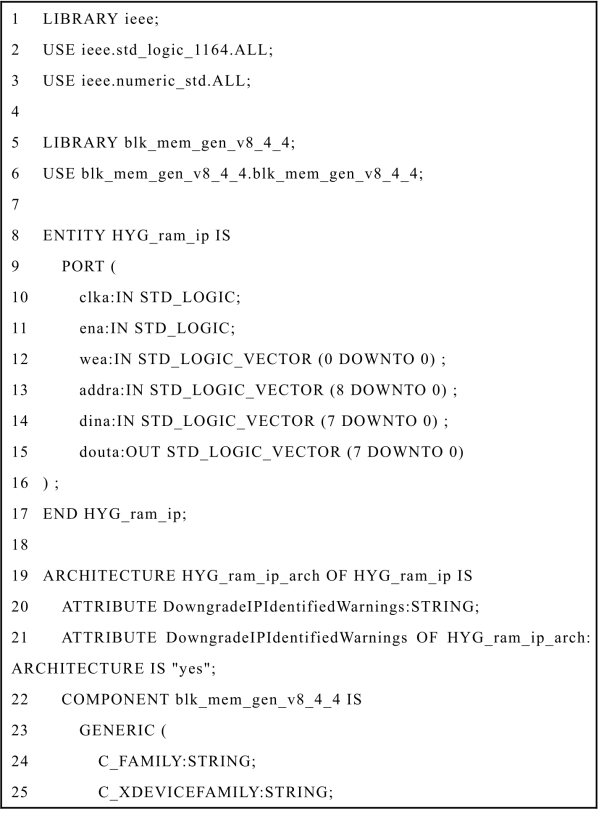

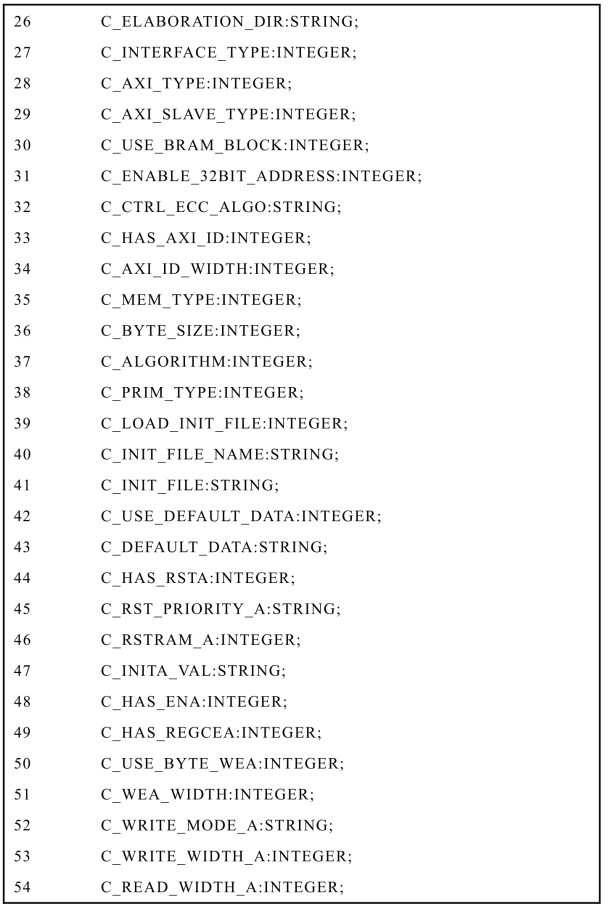

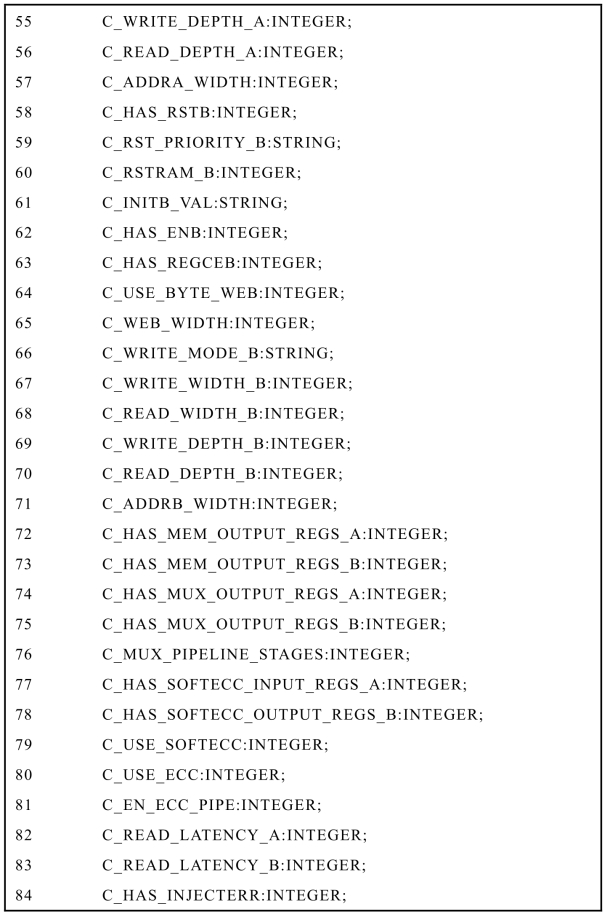

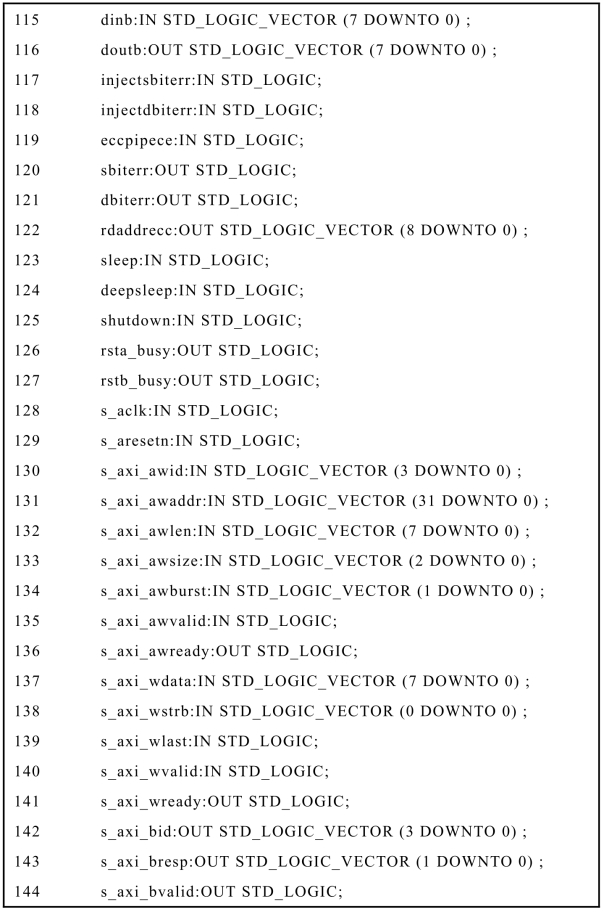

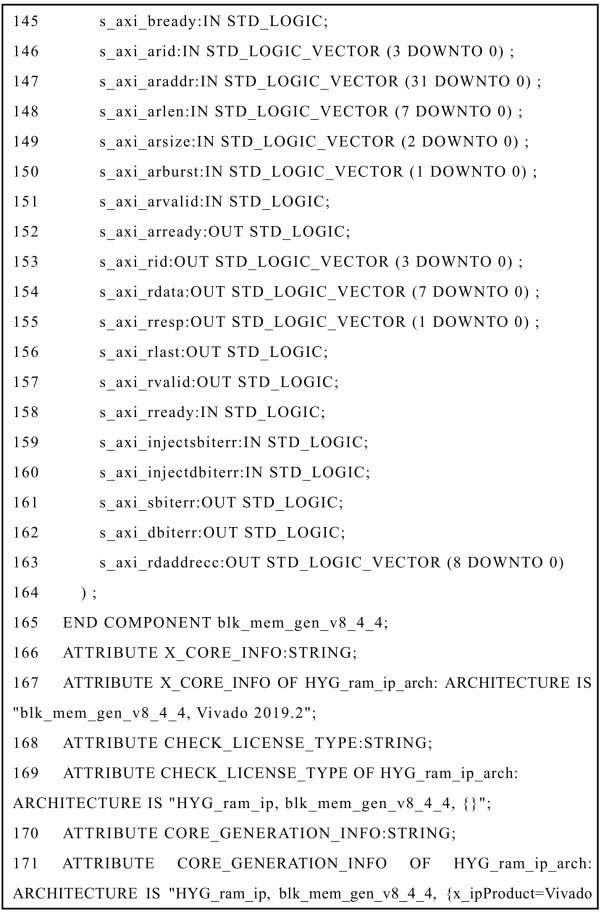

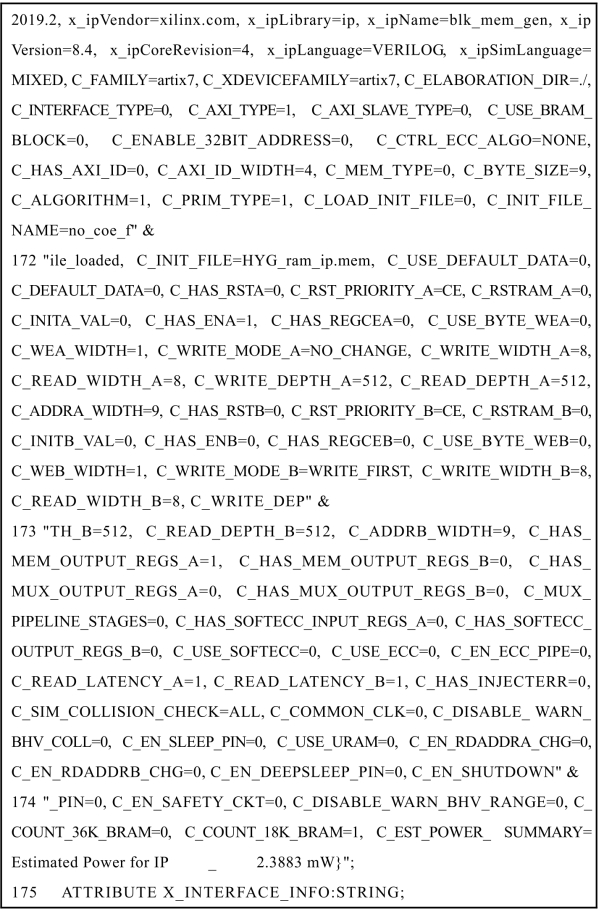

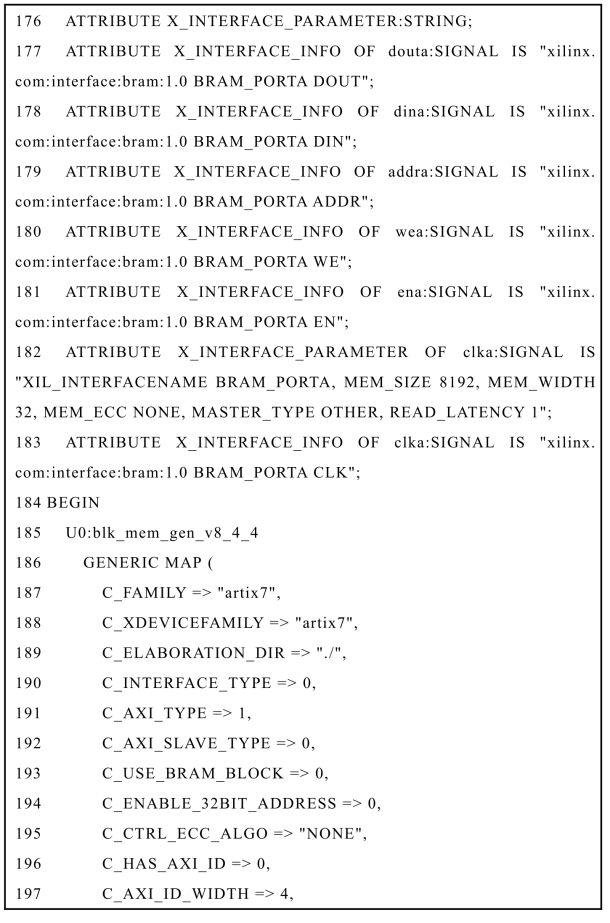

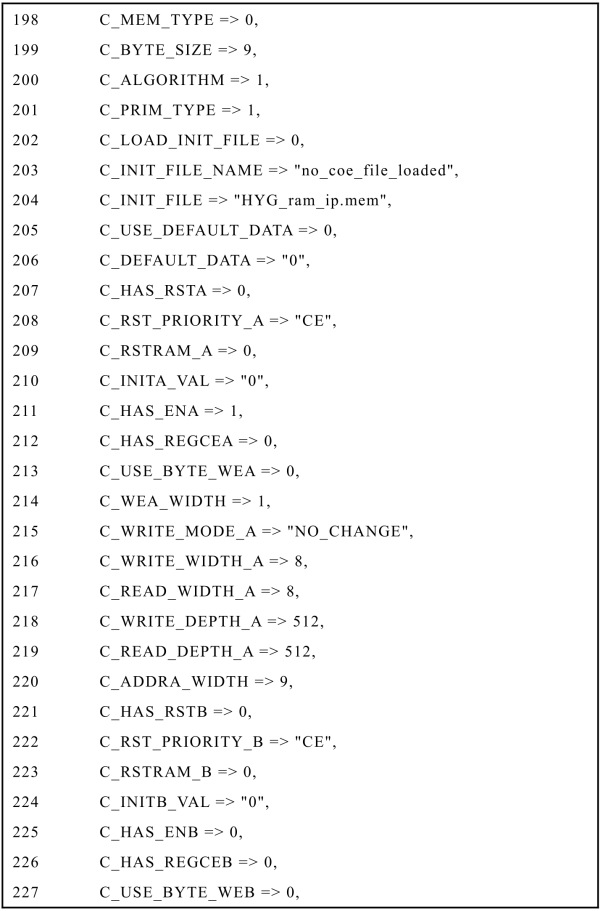

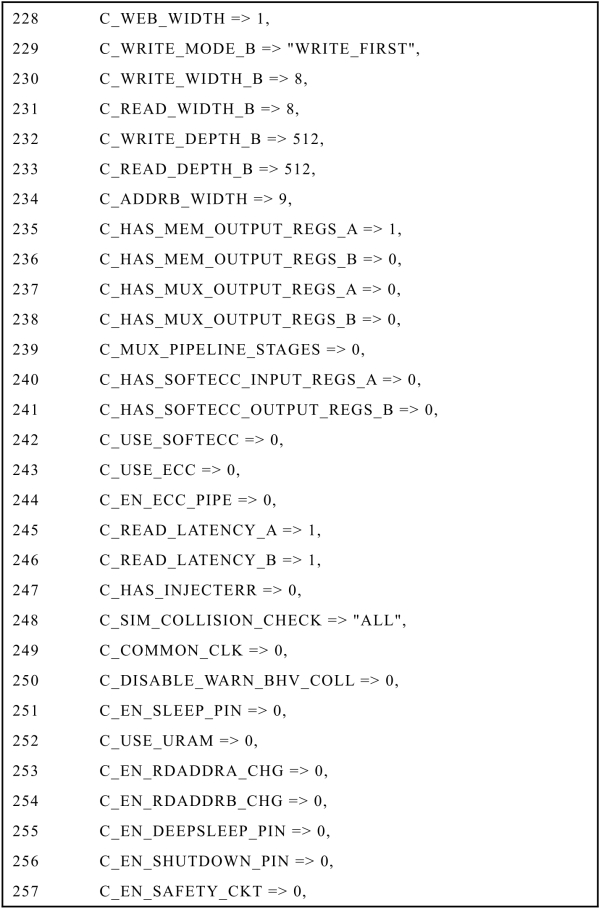

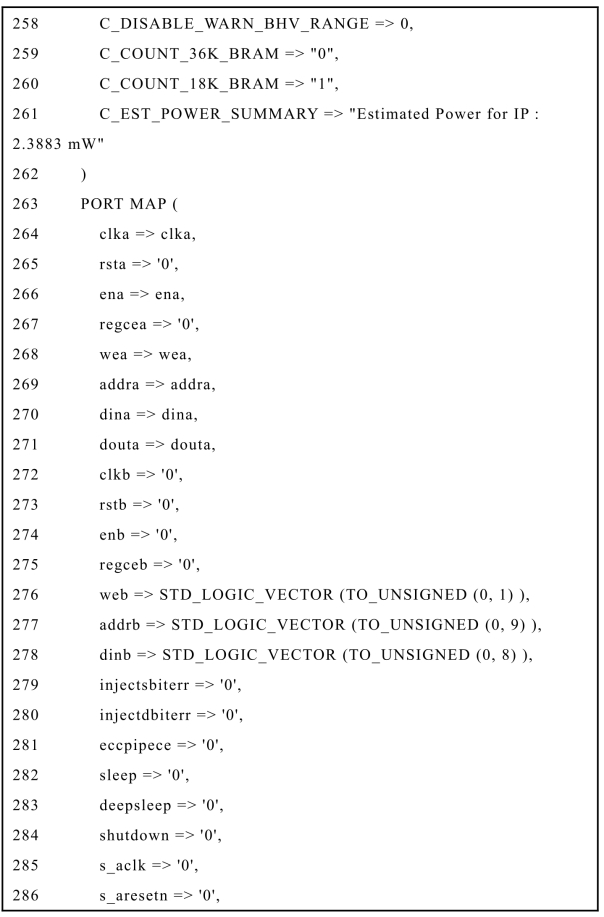

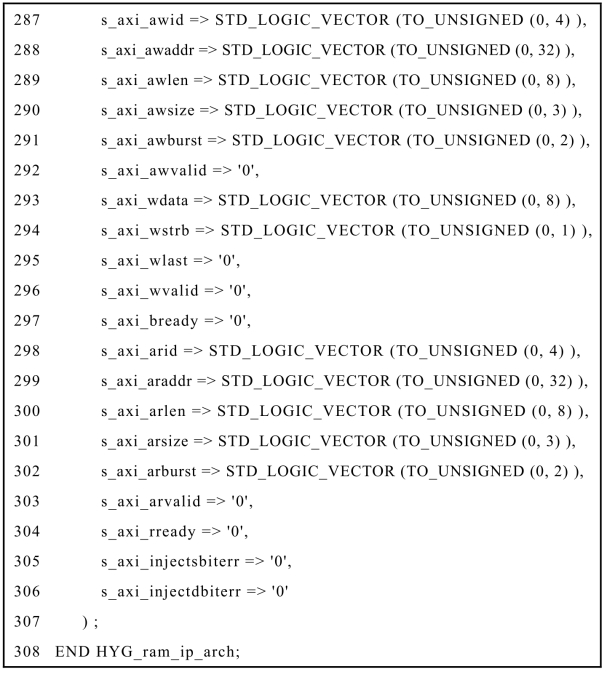

配置完相关参数后,直接单击完成,即可实现IP核定制,其代码生成结果见【代码3-6】。

【代码3-6】RAM IP核定制代码

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。