1.功能和特点

Xilinx基于RAM的移位寄存器IP核提供非常有效的多比特宽度移位寄存器,可以用作类似于FIFO(先进先出)的数据缓存或延时线功能,用这个IP核可以创建固定长度和可变长度的移位寄存器。其主要功能和特性包括:

(1)用LUT的SRL16/SRL32模式实现快速、简洁的FIFO型移位寄存器或延时线。

(2)可以创建定长或变长移位寄存器。

(3)可以对变长移位寄存器设置速度最优或资源最优。

(4)对变长移位寄存器可以通过时钟使能和同步控制实现输出寄存器选择。

2.接口说明

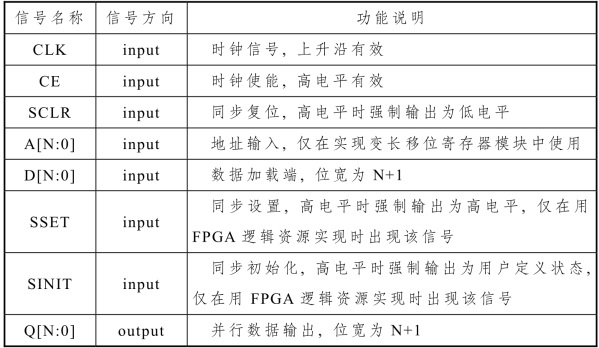

基于RAM的移位寄存器IP核的原理图符号如图2.15所示,其端口及功能说明如表2.3所示。

图2.15 移位寄存器IP核的原理图符号

表2.3 基于RAM的移位寄存器IP核端口及功能说明

(https://www.xing528.com)

(https://www.xing528.com)

3.调用技巧

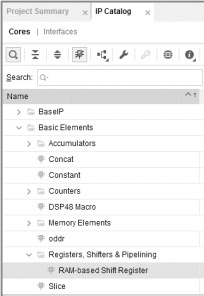

(1)在VIVADO工程中,打开IP核管理器【IP Catalog】→【Basic Elements】→【Registers,Shifters&Pipelining】→【RAM-based Shift Register】,如图2.16所示。

图2.16 基于RAM的移位寄存器IP 核存放位置

(2)参数配置。

在图2.17所示对话框中,主要设置“Shift Register Type”(移位寄存器类型),分为固定长度和长度可变两种类型;以及“Dimensions”宽度和存储深度设置。

图2.17 基于RAM的移位寄存器IP 核参数配置

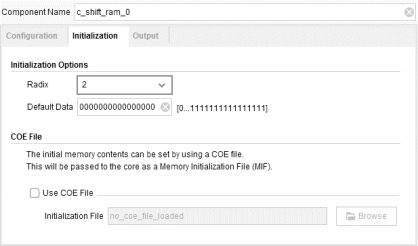

在图2.18所示对话框中,设置移位寄存器内容初始化,“Initialization Options”包含设置进制类型和默认数据值两个参数;“COE File”添加COE格式的初始化文件。

图2.18 初始化参数设置

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。