1.功能和特点

Xilinx二进制计数器IP核可以实现递增计数、递减计数或者递增/递减计数,模块功能可以在单个XtremeDSP上或基于FPGA芯片内部逻辑资源实现。二进制计数器IP核提供一个可编程的门限信号输出,当计数器值达到用户自定义的值时该信号有效。计数器IP核可以灵活配置,计数上限是可编程的,计数增量值也是可以自定义的。当计数达到最终值或用户自定义值后,下一个计数值为零。计数器IP核的主要功能和特性包括:

(1)可以生成递增、递减或递增/递减计数器。

(2)以FPGA逻辑资源实现时支持1~256位计数,以DSP48实现时支持从1~36位或1~48位输出(与FPGA芯片系列有关)。

(3)支持流水,最大化速度性能。

(4)提供用于门限的预检测和终止计数检测。

(5)支持可选的可编程门限输出,计数器增量值可以自定义,计数上限可编程。

(6)支持可选的时钟使能和同步复位(SCLR),以及同步设置和同步初始化能力。

2.接口说明

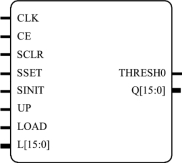

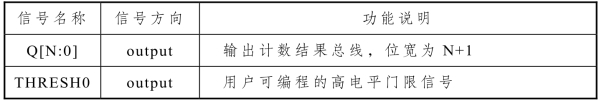

图2.10所示是二进制计数器IP核元件符号图,其接口端口及功能如表2.2所示。

图2.10 二进制计数器IP核原件图符号

表2.2 二进制计数器IP核端口及功能说明

续表

3.设计考虑

1)输入信号的优先级

(1)SCLR/SSET:SCLR相对于SSET的优先级可以通过“同步设置和复位优先级”参数设置。

(2)LOAD:同步控制信号(SCLR、SSET和SINIT)的优先级高于LOAD的优先级。

需要注意的是,如果SCLR、SSET和SINIT由CE决定(在“同步控制和时钟使能(CE)优先级”参数中设置),则CE为低电平时忽略上述信号。例如,如果SCLR由CE决定,则在CE为低电平时,LOAD重载SCLR信号。

2)计数限制

计数限制选项使用的是“等于”检测而不是“大于等于”检测,如果计数器的计数值不等于最终计数值,则计数器会一直计数到其数据位宽所能表示的最大值。这样,计数限制允许的参数限制为:计数模式不能是UPDOWN;SSET必须为假,即设置为不选中相应选项。

另外,实现“流水”时还要考虑更多的限制,对于递增计数和递减计数限制也不同。

(1)递增计数器。递增计数器的计数以增量值为单位,直到Q等于最终计数值,在其后的时钟周期计数器复位为0。对于递增计数器,有两个基本限制:最终计数值必须是计数增量值的整数倍;计数增量值必须小于等于最终计数值。

另外,还需要如下设置:如果使用了SINIT,需要设置初始值;设置上电复位时的初值(AINIT值);在L数据端口加载所有数据。(https://www.xing528.com)

(2)递减计数器。递减计数器的计数以增量值为单位,直到Q等于最终计数值,在其后的时钟周期计数器复位为0,同时计数器继续递减计数。对于递减计数器,有两个基本的限制:(2N-最终计数值)必须是计数增量值的整数倍;计数增量值必须小于等于(2N-最终计数值)。

另外,还需要如下设置:如果使用了SINIT,需要设置初始值;设置上电复位时的初值(AINIT值);在L数据端口加载所有数据。

3)LOAD的使用

计数器能够检测上电复位时初始值是否满足上述约束条件,但是不能检测通过L数据端口加载的数据是否满足约束条件。因此,如果加载的值不满足约束条件,则可能导致错误结果。例如,假设计数器的最终计数值设置为8,计数增量值设置为2,如果在L数据端口加载的数据为3,则计数器只以奇数计数,则会错过最终计数值,不会在达到最终计数值(因为计数结果永远不会等于最终计数值)后复位到0。

如果是用XtremeDSP(DSP48)实现的二进制计数器,则用DSP48的操作模式控制。这种控制会影响用于控制结束计数复位属性的某些相同数据,但需要额外的逻辑来处理这些被影响的数据,这样会导致性能变差或者在反馈路径上出现附加延时。加载路径上的附加延时要求为DSP48的D端口和用于计数增量值的C端口设置寄存器。尽管计数增量值是常数,但还是需要寄存才能保证从SCLR开始的延时与加载(LOAD)延时匹配。因此,用DSP48实现的二进制计数器的延时与数据位宽有关,而且随着计数限制、是否加载、加载设置、输出数据位宽的变化而变化,并且与所选择的FPGA芯片系列相关。

在创建二进制计数器时,如果使用计数限制条件,则建议不要使用加载(LOAD)模式,如果在某些应用中必须使用加载(LOAD)模式,则最好用外部逻辑创建一个“大于等于”的检测条件代替IP核默认的“等于”检测条件来确保计数器能正常工作。另外,也可以通过确保计数器的计数增量值比较简单,如等于1,这样就不会加载一个超过最终计数值的数,从而可以保证计数器正常工作。

4)流水操作

在流水操作时,计数结束检测要求检测的实际值是最终计数值减去计数增量值的整数倍,倍数由延时时钟总数决定,这增加了对计数增量值和最终计数值之间关系的限制,如果加载的数值可能导致无法实现用最终计数值结束计数,综合过程将给出警告。

为实现更好的性能,二进制计数器IP核提供了4个参数:延时设置、延时值、反馈延时设置和反馈延时值。前两个参数描述的是覆盖从SCLR开始或从LOAD值开始的时钟周期数,即前向数据路径中的串行寄存器个数。当延时设置模式为人工设置时,延时值设定为针对指定延时的特定值;如果延时设置模式为自动设置,在IP核内部将计算实现最优性能的延时值。所谓最优性能,是指操作时钟频率大于等于全流水XtremeDSP的操作速度,实现过程通过将主计数操作的进位链分割成多个拼接链实现。拼接链的个数由计数器的数据位宽和所用FPGA芯片决定。反馈延时和反馈延时值是指在最终计数反馈电路中设置的延时,因此仅用于有计数限制的情况。当反馈延时设置模式为人工设置时,延时值被设定为针对指定延时的一个特定值;如果延时设置模式为自动设置,在IP核内部将计算实现最优性能的延时值。

4.调用技巧

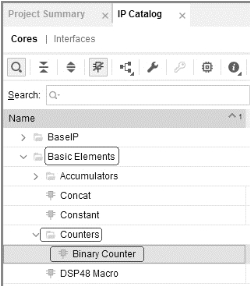

(1)在VIVADO工程中,打开IP核管理器【IP Catalog】→【Basic Elements】→【Counters】→【Binary Counter】,如图2.11所示。

图2.11 Binary Counter存放位置

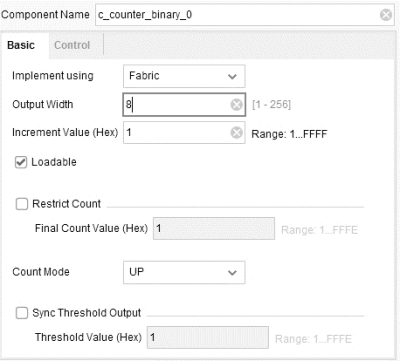

(2)参数配置界面如图2.12所示。“Component Name”设置调用元件的名字,“Basic”页面可设置以下参数:

Output Width:设置计数器输出位宽;

Increment Value(HEX):设置计数器的步进值;

复选框Loadable:表示是否允许加载计数初值,勾选表示使用端口“LOAD”和“L[N:0]”;

图2.12 Binary Counter配置界面

“Count Mode”:是计数模式设置,主要有三种选项选择,分别是“UP”“DOWN”和“UPDOWN”,表示递增模式、递减模式和加减可逆模式,如图2.13所示。

图2.13 计数模式选择

“Control”页面主要设置控制信号,勾选相应的复选框即可使用相关功能端口,如图2.14所示。

图2.14 Control设置界面

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。