1.功能特点

Xilinx乘加器(Multiply Adder)IP核基于XtremeDSP资源实现。模块接收3个操作数A、B和C,实现两个操作数的乘法并将结果与第三个操作数进行加/减法运算,得到输出结果。乘加器IP核的主要功能和特性包括:

(1)生成乘加和乘减功能。

(2)支持两组有符号数和无符号数操作。支持的数据范围是:对于乘法器,支持1~52位的无符号数据输入或2~53位的有符号数据输入;对于加法或减法操作,支持1~105位的无符号数据或2~106位的有符号数据操作。

(3)支持可选的时钟使能和同步复位(SCLR)。

(4)可选流水操作。

2.接口说明

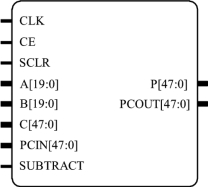

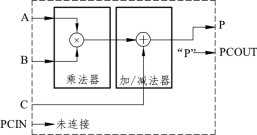

VIVADO IP核管理器中乘加器IP核的原理图符号及接口信号如图2.3所示。

图2.3 乘加器原理图符号

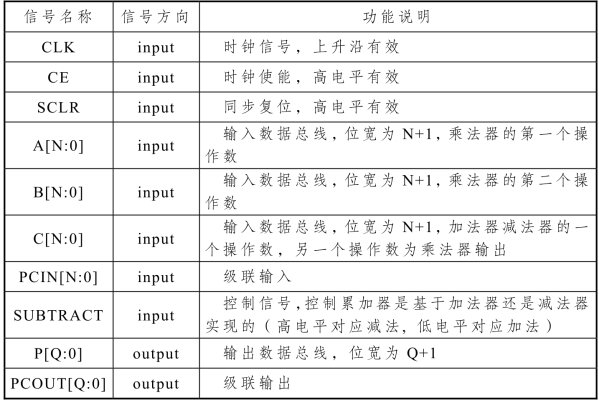

乘加器端口及功能说明如表2.1所示。

表2.1 乘加器端口及功能说明

3.功能描述

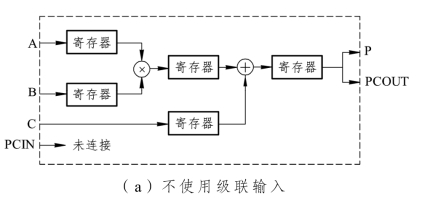

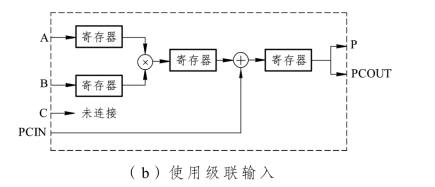

乘加器实现时考虑两条延时路径,一条是从输入端口A和B到输出端口P的延时路径,另一条是从输入端口C或PCIN到输出端口P的延时路径,分别定义为A:B-P延时和C-P延时。这些延时的取值只有-1或0,其中0表示没有延时,-1表示最大、最优延时。如果其中一个延时设置为-1,则两条路径的延时都按照-1执行,即实现最大、最优延时。是否使用级联PCIN端口是影响流水延时重要因素,图2.4给出了在单个XtremeDSP内实现乘加器时是否使用PCIN端口时不同的寄存器配置。

图2.4 乘加器内部寄存器配置(https://www.xing528.com)

另外,如果用多个XtremeDSP单元实现乘加器,那么相当于乘法器和加/减法器用不同的XtremeDSP实现,则端到端的延时为乘法器延时与加/减法器延时之和,图2.5所示。

图2.5 多个XtremeDSP Slice实现乘加器时的延时示意图

使用乘加器IP核实现乘加功能模块时,还要考虑数据对齐问题。乘加器IP核的所有输入在核内部都是以右对齐方式进行操作的,正常的LSB(最低有效位)或MSB(最高有效位)以及输入符号扩展(相对于二进制数)由用户指定。

在乘加器中没有对乘法器的输出进行截断或取整,而是全精度的。端口C的输入LSB与乘法结果的LSB对齐进行加/减法运算。例如,如果端口A、B和C的输入数据宽度分别为6、8和8,则A×B+C运算过程以二进制表示,运算结果中MSB的最低位为11,如图2.6所示。

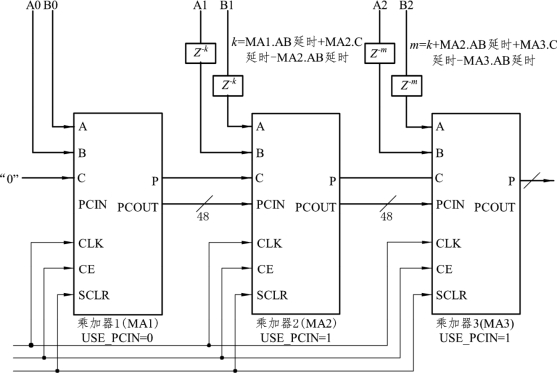

下面给出一个用多个乘加器级联实现矢量乘法的例子,两个矢量分别为A=[A0 A1 A2]和B=[B0 B1 B2],计算C=A×BT,可以用如图2.7所示的结构实现。

图2.6 乘加器运算过程

图2.7 用乘加器实现矢量乘法

4.调用技巧

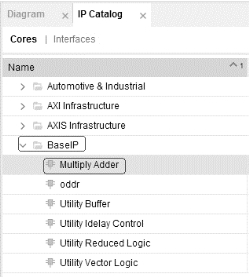

(1)在VIVADO工程中,打开IP核管理器【IP Catalog】→【BaseIP】→【Multiply Adder】,如图2.8所示。

图2.8 乘加器存放位置

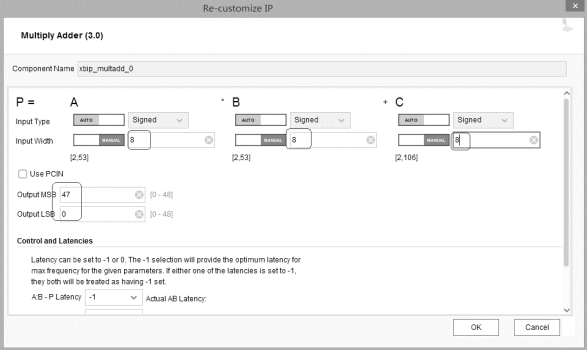

(2)参数配置。在使用乘加器IP核时,参数配置界面如图2.9所示。应根据实际功能需要设置三个输入对象A、B、C以及输出端口的数据位宽。在改变数据输入位宽时,需将Input Width的状态由“AUTO”切换为“MANUAL”,此时才允许修改相应参数。“Use PCIN”复选框表示是否使用级联输入功能,配置界面中共还可以设置延时特性。

图2.9 乘加器IP核参数设置界面

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。