按照存储器的存取功能,存储器可分为只读存储器ROM和随机存取存储器(RAM)两大类。

1.数据存储器RAM芯片

(1)静态RAM(Static RAM,SRAM)芯片 它的电路是一个稳态触发器,用触发器的两个稳定状态来表示二进制0、1。每一个位都是一个双稳态触发电路,8个位就是8个触发器组成1字节。SRAM的一个特点是它的状态一旦实现,可以保持住,即带电信息可长期保存,功效好,体积也小。下面对SRAM芯片的基本存储电路的结构进行介绍。

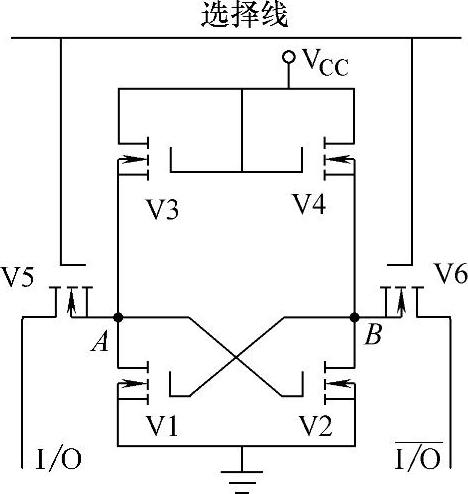

1)基本存储电路。SRAM的基本存储电路通常由如图8-1所示的6个MOS管组成。在此电路中,V1~V4组成双稳态触发器:V1、V2为放大管,V3、V4为负载管,V5、V6为控制管。若V1截止,则A点为高电平,它使V2导通,于是B点为低电平,这又保证了V1的截止。同样,V1导通而V2截止,这是另一个稳定状态,因此可用V1的两种状态分别表示“1”或“0”。由此可知SRAM保存信息的特点是和这个双稳态触发器的稳定状态密切相关的。其读/写操作过程如下:

①写操作。当地址译码器的某一个输出线送出高电平到控制管V5、V6的栅极时,V5、V6导通,于是,A点与I/O线相连,B点与 线相连。这时如果要写“1”,则I/O为“1”,

线相连。这时如果要写“1”,则I/O为“1”, 为“0”,它们通过V5、V6与A、B点相连,即A=“1”,B=“0”,使V1截止,V2导通。而当写入信号和地址译码信号消失后,V5、V6截止,该状态仍能保持。如要写“0”,I/O线为“0”,

为“0”,它们通过V5、V6与A、B点相连,即A=“1”,B=“0”,使V1截止,V2导通。而当写入信号和地址译码信号消失后,V5、V6截止,该状态仍能保持。如要写“0”,I/O线为“0”, 线为“1”,这使V1导通,V2截止,只要不掉电,这个状态会一直保持,除非重新写入一个新的数据。

线为“1”,这使V1导通,V2截止,只要不掉电,这个状态会一直保持,除非重新写入一个新的数据。

图8-1 静态RAM的基本存储电路

②读操作。需地址译码器的某一输出线送出高电平到V5、V6栅极,即此存储单元被选中,此时V5、V6导通,于是V1、V2的状态被分别送至I/O和 线,这样就读出了所保存的信息。显然,存储的信息被读出后,所存储的内容并不改变,除非重写一个数据。

线,这样就读出了所保存的信息。显然,存储的信息被读出后,所存储的内容并不改变,除非重写一个数据。

由于SRAM存储电路中,MOS管数目多,故集成度较低,而V1、V2组成的双稳态触发器必有一个是导通的,功耗也比动态RAM大,这是SRAM的两大缺点。其优点是不需刷新电路,从而简化了外部电路。

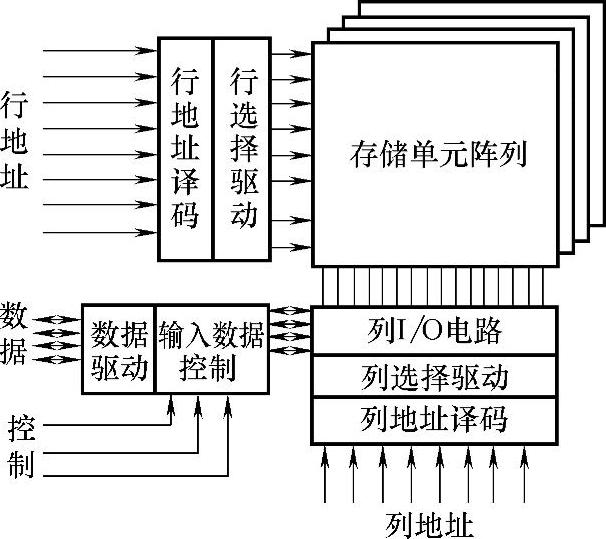

图8-2 SRAM芯片的功能框图

2)SRAM的结构。SRAM芯片内部是由很多基本存储电路组成的,所有基本单元排列成m×n的存储矩阵。芯片容量为单元数与数据线位数之乘积,如1KB=1K×8bit=1024×8bit。为了选中某一个单元,往往利用矩阵式排列的地址译码电路,即存储器内部为双向地址译码,以节省内部引线和驱动器。例如:1K单元的内存芯片,需10根地址线,其中5根用于行译码,另5根用于列译码,译码后在芯片内部排列成25=32条行选择线和25=32条列选择线,总共需要64根译码线和64个驱动器,就可选中1024个单元中的任何一个。如果采用单向译码需要1024根译码输出线和驱动器。而每一个单元中的基本存储电路个数与数据线位数相同,即每个存储单元由若干个基本存储电路组成。常用的典型SRAM芯片的功能框图如图8-2所示。

(2)动态RAM(Dynamic RAM,DRAM)芯片 这类芯片用得更加广泛,一般用在大型设备上。他不是由触发器组成的,而是由一个电容构成的存储电路,用电容电荷的有、无来表示1或0,这种电路的集成度更高。因为电容容易漏电,所以必须不断进行刷新,即充电,把原来的状态维持住。下面对动态RAM芯片基本存储电路的结构进行介绍。

1)DRAM的存储电路。SRAM每个单元电路需6个MOS管,功耗大且集成度低。为提高集成度和降低功耗,进一步研制出了DRAM器件,其基本存储电路为单管动态存储电路,如图8-3所示。由图可见,DRAM存放信息靠的是电容器C,电容器C有电荷时,为逻辑“1”,没有电荷时,为逻辑“0”。由于任何电容器都存在漏电,因此当电容器C存有电荷时,过一段时间由于电容器的放电过程导致电荷流失,信息也就丢失。解决的办法是刷新,即每隔一定时间(一般2ms)就要刷新一次,使原来处于逻辑电平“1”的电容器的电荷又得到补充,而原来处于电平“0”的电容器仍保持“0”。其读/写操作过程如下:

图8-3 单管动态存储电路

①读操作。根据行地址译码,使某一条行选择线为高电平,使本行上所有的基本存储电路中的V1导通,使连在每一列上的刷新放大器读取对应存储电容器上的电压值。刷新放大器将此电压值转换为对应的逻辑电平“0”或“1”,又重写到存储电容器,列地址译码产生列选择信号,选中该列的基本存储电路,从而读取信息。

②写操作。行选择信号为高电平“1”,V1处于导通状态,此时列选择信号也为高电平“1”,则此基本存储电路被选中,于是由外接数据线送来的信息通过刷新放大器和V1送到电容器C上。

刷新是逐行进行的,当某一行选择信号为“1”时,选中了该行,电容器上的信息送到刷新放大器上,刷新放大器又对这些电容器立即进行重写。由于刷新时,列选择信号总为低电平“0”,因此电容器C上的信息不可能被送到数据总线上。

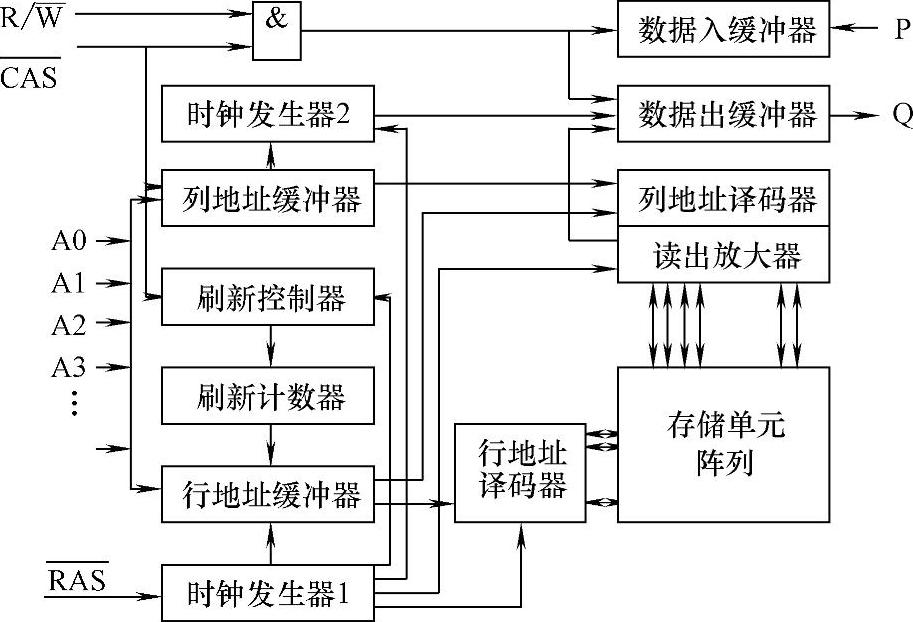

图8-4 DRAM芯片的内部结构框图

2)DRAM的结构。图8-4所示是一个2116 DRAM芯片的内部结构框图,DRAM芯片由存储矩阵、读/写控制及刷新控制电路构成。图中,芯片上的行地址选通 和列选通

和列选通 分别选通和锁存行地址和列地址。在行地址中,包括了存储地址和刷新地址,因此要有刷新多路器,该多路器让刷新地址在刷新期间通过。行地址A0~A6和刷新地址RA0~RA6通过刷新多路器送往行/列多路器,再送往2116的对应引脚。通过

分别选通和锁存行地址和列地址。在行地址中,包括了存储地址和刷新地址,因此要有刷新多路器,该多路器让刷新地址在刷新期间通过。行地址A0~A6和刷新地址RA0~RA6通过刷新多路器送往行/列多路器,再送往2116的对应引脚。通过 、

、 及

及 信号的配合,实现对存储器的刷新与读/写。

信号的配合,实现对存储器的刷新与读/写。

2.程序存储器ROM芯片

(1)掩膜ROM所谓掩膜ROM,是指其状态已经不是一个双稳的状态,变成理论上单稳定状态或是“死”的状态,换句话说,用掩膜工艺把信息一次固化在里面。掩膜ROM适合于批量生产,产品已经定型,信息可以不变,由生产芯片的厂家固化信息,在最后一道工序用掩膜工艺写入信息,用户只可读。它的好处就是成本大幅降低。缺点是存储的数字信息不能再修改。

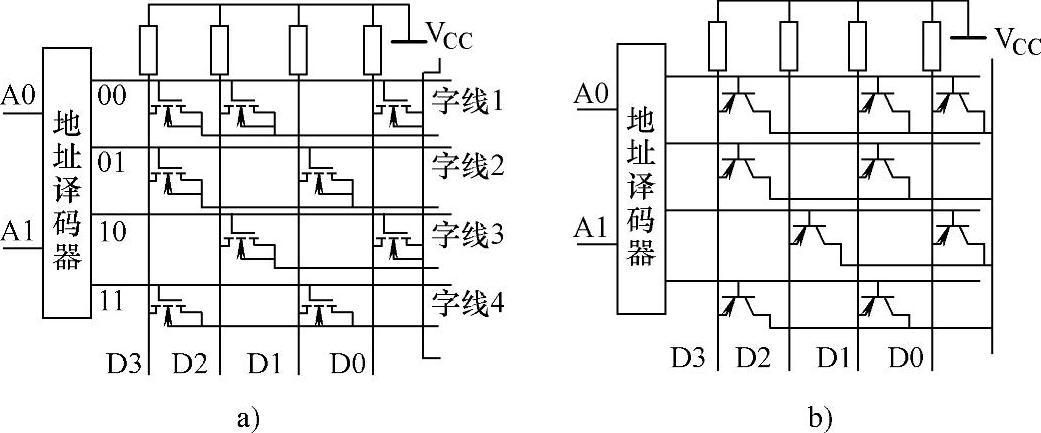

根据制造工艺可以将它们分为MOS型和双极型两种。MOS型ROM功耗小、速度慢,适用于一般微机系统;而双极型则速度快、功耗大,适用于速度较高的计算机系统。掩膜ROM结构原理图如图8-5所示。(https://www.xing528.com)

图8-5 掩膜ROM结构原理图

a)MOS型ROM b)双极型ROM

图8-5中是个简单的4×4位MOS(或双极型)管ROM,采用单译码结构,A0、A1上的地址信号经译码后,输出4条选择线,可分别选中4个单元,每个单元有4位输出。图中所示的矩阵中,在行和列的交点,有的连有MOS管,有的没有,这是由工厂根据用户提供的程序代码和数据对芯片图形(掩膜)进行二次光刻所决定的,所以称为掩膜ROM。若地址线A0、A1为00,即字线0为高电平,则选中0号单元,若有MOS管与其相连(如位线3、2和0),其相应的MOS管导通,位线输出为0,而位线1没有管子与字线相连,输出为1,即0号单元的内容为0010。

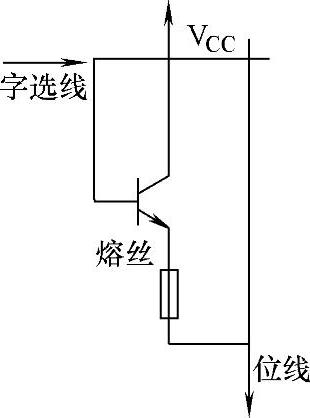

(2)可编程ROM(PROM) 由于掩膜ROM需产量较大才能降低其成本,人们就希望能生产一种通用的器件,通过编程的方法将数据写入器件中,当该通用器件的生产量将相当大时,就降低单片芯片的价格。人们首先根据电路熔丝得到了启发,在存储器每个存放数据的结点上加上一个熔丝(相当于通常电工用的熔丝),这样该器件在出厂时每个单元内容全部为1,如果希望某一位存放数据0,只需将该结点对应的熔丝烧断即可。通常用二极管或双极型晶体管作存储单元。图8-6所示是用双极型晶体管作存储单元电路,在这种存储单元中,每一位晶体管的发射极上串接一个可熔金属丝,出厂时所有晶体管的发射极上的熔丝是完整的,晶体管可将位线和字线连通,表示存有信息“0”(即整个芯片末使用前全为“0”)。用户编程时,根据程序要求,对需要写入“1”的位,通以足够大的脉冲电流,使相应位的熔丝烧断,该位便存入信息“1”。未被熔断的位仍为“0”,从而实现了信息的一次性写入。

该种存储器存在一些不足:由于在半导体电路中加入了金属丝,使生产工艺变得复杂;其次,由于可编程的部分是由熔丝构成的,这就决定了该存储器一旦将内容写错,其芯片就只能报废。

图8-6 双极型晶体管作存储单元电路

(3)可擦除重写ROM(EPROM) EPROM通常有紫外线可擦除只读存储器ROM(UVEP-ROM)和电可擦除ROM(EEPROM)。

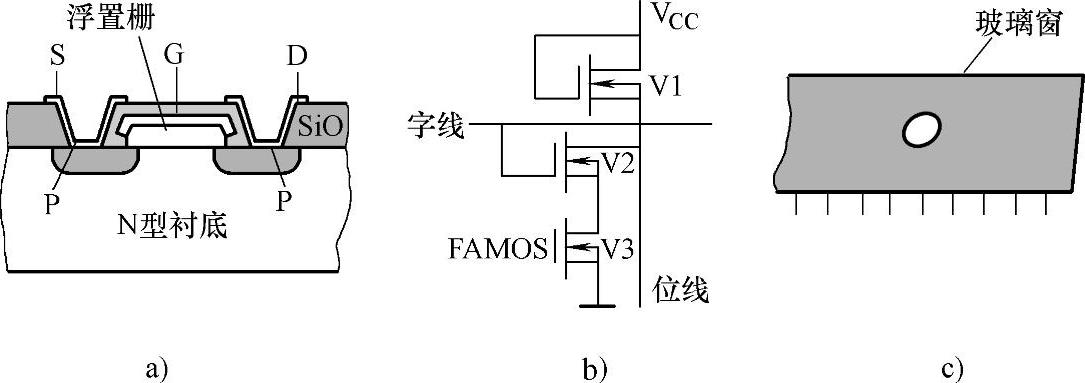

1)紫外线可擦除ROM(UVEPROM)。紫外线可擦除UVEPROM存储电路是利用浮栅MOS管构成的,又称FAMOS管,用户可以多次编程。编程加写脉冲后,某些存储单元的PN结表面形成浮动栅,阻挡通路,实现信息写入。用紫外线照射可驱散浮动栅,原有信息全部擦除,便可再次改写。浮栅MOS EPROM存储电路如图8-7所示,MOS晶体管与EPROM单元的两种工作状态如图8-8所示。

图8-7 浮栅MOS EPROM存储电路

a)FAMOS管的结构 b)EPROM存储单元 c)EPROM外型

该电路和普通P型沟道增强型MOS管相似,只是栅极没有引出端,而被二氧化硅绝缘层所包围,称为“浮栅”。原始的浮栅不带电荷,FAMOS管不导通,位线上是高电平,存储的信息为1。当FAMOS管的源极S与衬底接地电位、漏极D接较高电压(大于正常工作电压)时,漏极PN结反向击穿产生“雪崩”现象,使浮栅积累电荷,FAMOS管处于导通状态,位线被钳在低电平,存储的数据为0。由于浮栅被绝缘的二氧化硅包围,电荷不会丢失,即信息不会丢失,这种存储的信息可以安全保存20年以上,但为了防止平时日光中的紫外线的照射,在其玻璃窗口上贴上黑纸。

UVEPROM的优点是其内容可以擦除后重新写入数据,即使写错了也无所谓,缺点是其重新改写时需将存储器拆下来用专门的编程器来进行改写。由于其价格较低、使用方法较简单,所以现在使用得还相当广泛。

2)电可擦除ROM(EEPROM) 电可擦除ROM是在EPROM的基础上开发的,可以在加电的情况下进行全片或字节擦除,然后在电路上直接改写其擦除过的单元内容。具备ROM、RAM的优点,不但可以修改程序,还可以修改数据,但写入时间较长。

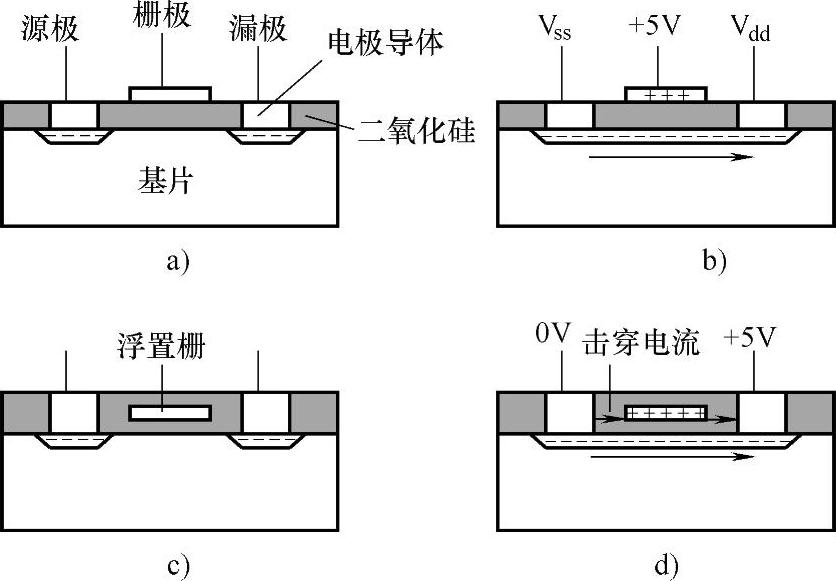

图8-8 MOS晶体管与EPROM单元的两种工作状态

a)MOS晶体管结构 b)MOS晶体管导通状态 c)EPROM晶体管结构 d)EPROM晶体管导通

EEPROM的内部电路,与EPROM电路类似,但其结构进行了一些调整,在浮栅上增加了一个隧道二极管(实际上是在浮栅与N型的衬底形成一层薄薄的氧化层后形成的),在编程时可以使电荷通过它流向浮栅,而擦除时可使电荷通过它流向漏极,不需要紫外线激发放电,即擦除和编程只需加电就可以完成了,且写入的电流很小。EEPROM内部电路结构如图8-9所示。

(4)快擦写ROM(Flash ROM) FlashROM是在EPROM和EEPROM的基础上发展起来的一种只读存储器,读/写速度很快,存取时间可达70ns,存储容量可达2~16KB,最近有16~64MB的产品问世,可擦写次数在1~100万次。

图8-9 EEPROM内部电路结构

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。