使用中断系统时,必须做好的准备工作称之为中断系统初始化。这一工作是在程序的初始化段用三种指令完成的。

1.开相应中断源的中断

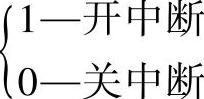

MCS-51系列单片机的中断系统由中断允许寄存器IE(A8H)来控制对各中断源的中断请求被开通(允许)或被关闭(禁止)。

SFR中(A8H)IE各位定义如图6-4所示,其作用是当IE的各位为

图6-4 中断允许寄存器IE各位定义

EA:中断总允许位。 EA=0时关闭总开关,禁止一切中断。

EA=1时接通总开关,才可能使各个中断源的请求传到CPU。

IE.6:保留位。

ET2:定时器/计数器2溢出中断允许位。 ET2=0时禁止该类中断。

ET2=1时接通源允许相应开关,将中断请求送到总允许部分。

ES:串行接口收、发中断允许位。 ES=0时禁止该类中断。

ES=1时接通源允许相应开关,将中断请求送到总允许部分。

ET1:定时器/计数器1溢出中断允许位。 ET1=0时禁止该类中断。

ET1=1时接通源允许相应开关,将中断请求送到总允许部分。

EX1:外部中断1( )允许位。 EX1=0时禁止该类中断。

)允许位。 EX1=0时禁止该类中断。

EX1=1时接通源允许相应开关,将中断请求送到总允许部分。

ET0:定时器/计数器0溢出中断允许位。 ET0=0时禁止该类中断。

ET0=1时接通源允许相应开关,将中断请求送到总允许部分。

EX0:外部中断0( )允许位。 EX0=0时禁止该类中断。

)允许位。 EX0=0时禁止该类中断。

EX0=1时接通源允许相应开关,将中断请求送到总允许部分。

注意:要使某个中断源的中断申请得到响应,必须保证EA=1和相应的允许位为1。中断允许寄存器IE既可按字节寻址,也可按位寻址。

例如:采用的中断初始化指令为:

ORL IE,#84H, 其作用就是对EA、EX1置1——开外中断1。

按位寻址为:SETB EA

SETB EX1

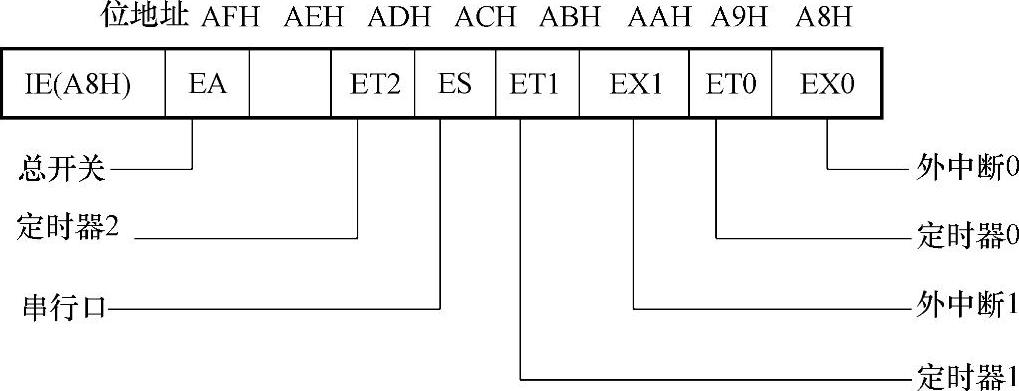

2.设定所用中断源的中断优先级

单片机采用了自然优先级和人工设置高、低优先级的策略,即可以由程序员设定哪些中断是高优先级、哪些中断是低优先级,由于只有两级,必有一些中断处于同一级别,处于同一级别的,就由自然优先级确定。即:

1)低优先级中断可被高优先级中断所中断,反之不能。

2)一种中断(不论是什么优先级),一旦得到响应,与它同级的中断源不能打断它。

3)当同时收到多个同级的中断请求时,哪一个首先得到中断服务,取决于单片机内部的查询顺序。

MCS-51系列单片机的5个中断源均可设为高低两个级别,由中断优先级寄存器IP来控制,IP各位的定义如图6-5所示。

图6-5 中断优先级寄存器IP各位定义

在响应中断时,CPU先响应高优先级中断;在同一级别中按表6-2中顺序来响应中断。

表6-2 MCS-51系列单片机中断优先排序表

3.设定中断服务程序始地址

将中断响应引入中断服务程序。在中断入口地址的3个字节中写入长跳转指令“LJMP SU-BI,SUBI”为相应中断源的中断服务程序的始地址。

例如:在6.1.4应用实例中

ORG 0013H; 的中断入口地址

的中断入口地址

LJMP PO16;PC←PO16(01E7H)转向中断 服务程序。

服务程序。

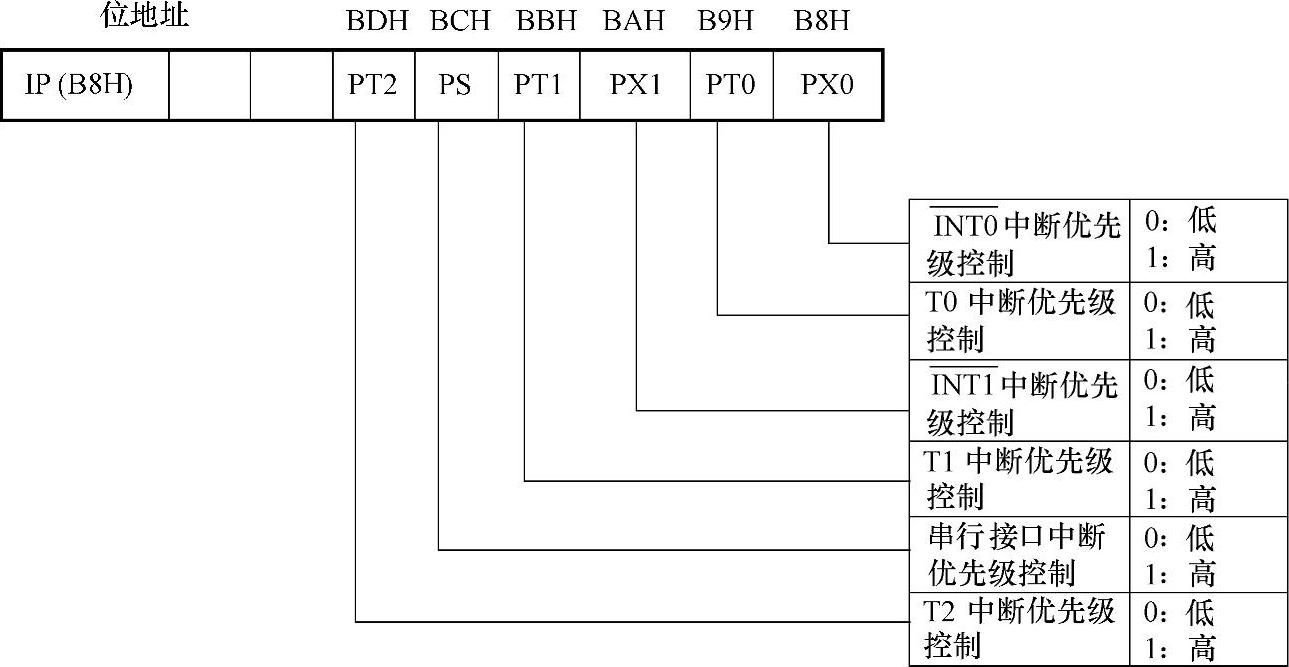

4.中断处理过程

中断处理过程可分为中断响应、中断处理和中断返回3个阶段。不同的单片机因其中断系统的硬件结构不同,中断响应的方式也有所不同。

(1)中断响应 中断响应是CPU对中断源中断请求的响应,包括保护断点和将程序转向中断服务程序的入口地址(通常称矢量地址)。CPU并非任何时刻都响应中断请求,而是在中断响应条件满足之后才会响应。

1)CPU响应中断的条件有:

①中断源发出中断请求。

②中断总允许位EA=1。

③申请中断的中断源允许。

满足以上基本条件,CPU一般会响应中断,但若有下列任何一种情况存在,则中断响应会受到阻断。

①CPU正在响应同级或高优先级的中断。

②当前指令未执行完。

③正在执行RETI中断返回指令或访问专用寄存器IE和IP的指令。

若存在上述任何一种情况,中断查询结果即被取消,CPU不响应中断请求而在下一机器周期继续查询,否则,CPU在下一机器周期响应中断。

CPU在每个机器周期的S5P2(图2-13)期间查询每个中断源,并设置相应的标志位,在下一机器周期S6期间按优先级顺序查询每个中断标志,如查询到某个中断标志为1,将在再下一个机器周期S1期间按优先级进行中断处理。

2)中断响应过程包括保护断点和将程序转向中断服务程序的入口地址。首先,中断系统通过硬件自动生成长调用指令(LCALL),该指令自动把断点地址压入堆栈保护(不保护累加器A、状态寄存器PSW和其他寄存器的内容);然后,将对应的中断入口地址装入程序计数器PC(由硬件自动执行),使程序转向该中断入口地址,执行中断服务程序。MCS-51系列单片机各中断源的入口地址由硬件事先设定,见表6-1。

使用时,通常在这些中断入口地址处存放一条绝对跳转指令,使程序跳转到用户安排的中断服务程序的起始地址上去。如采用定时器T1中断,其中断入口地址为001BH,中断服务程序名为CONT,因此指令形式为:

(2)中断处理 中断处理就是执行中断服务程序。中断服务程序从中断入口地址开始执行,到返回指令“RETI”为止,一般包括两部分内容,一是保护现场,二是完成中断源请求的服务。

通常,主程序和中断服务程序都会用到累加器A、状态寄存器PSW及其他一些寄存器,当CPU进入中断服务程序用到上述寄存器时,会破坏原来存储在寄存器中的内容,一旦中断返回,将会导致主程序的混乱。因此在进入中断服务程序后,一般要先保护现场,然后执行中断处理程序,在中断返回之前再恢复现场。

编写中断服务程序时还需注意以下几点:(https://www.xing528.com)

1)各中断源的中断入口地址之间只相隔8个字节,容纳不下普通的中断服务程序,因此在中断入口地址单元通常存放一条无条件转移指令,可将中断服务程序转至存储器的其他任何空间。

2)若要在执行当前中断程序时禁止其他更高优先级中断,需先用软件关闭CPU中断,或用软件禁止相应高优先级的中断,在中断返回前再开放中断。

3)保护和恢复现场时,为了不使现场数据遭到破坏或造成混乱,一般规定此时CPU不再响应新的中断请求。因此编写中断服务程序时,要注意在保护现场前关中断,在保护现场后若允许高优先级中断,则应开中断。同样,在恢复现场前也应先关中断,恢复之后再开中断。中断处理过程流程如图6-6所示。

图6-6中 断处理过程流程图

(3)中断返回 中断返回是指中断服务完成后,CPU返回原来断开的位置(即断点),继续执行原来的程序。中断返回由中断返回指令RETI来实现。该指令的功能是把断点地址从堆栈中弹出,送回到程序计数器PC,此外,还通知中断系统已完成中断处理,并同时清除优先级状态触发器。

(4)中断请求的撤除 CPU响应中断请求后即进入中断服务程序,在中断返回前,应撤除该中断请求,否则会重复引起中断而导致错误。MCS-51系列单片机各中断源中断请求撤销的方法各不相同,分别为:

1)定时器中断请求的撤除。对于定时器0或1溢出中断,CPU在响应中断后即由硬件自动清除其中断标志位TF0或TF1,无需采取其他措施。

2)串行接口中断请求的撤除。对于串行接口中断,CPU在响应中断后,硬件不能自动清除中断请求标志位TI、RI,必须在中断服务程序中用软件将其清除。

3)外部中断请求的撤除。外部中断可分为边沿触发型和电平触发型。

对于负边沿触发的外部中断0或1,CPU在响应中断后由硬件自动清除其中断标志位IE0或IE1,无需采取其他措施。

对于电平触发的外部中断,其中断请求撤除方法较复杂。因为对于电平触发外部中断,CPU在响应中断后,硬件不会自动清除其中断请求标志位IE0或IE1,也不能用软件将其清除,所以在CPU响应中断后,应立即撤除 或

或 引脚上的低电平。否则,就会引起重复中断而导致错误。而CPU又不能控制

引脚上的低电平。否则,就会引起重复中断而导致错误。而CPU又不能控制 或

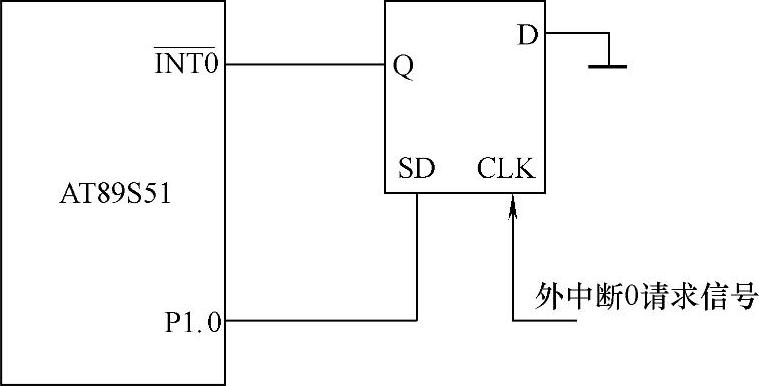

或 引脚的信号,因此只有通过硬件再配合相应软件才能解决这个问题。图6-7所示是撤除外部中断请求的电路之一。

引脚的信号,因此只有通过硬件再配合相应软件才能解决这个问题。图6-7所示是撤除外部中断请求的电路之一。

图6-7 撤除外部中断请求的电路

由图可知,外部中断请求信号不直接加在 或

或 引脚上,而是加在D触发器的CLK端。由于D端接地,当外部中断请求的正脉冲信号出现在CLK端时,Q端输出为0,

引脚上,而是加在D触发器的CLK端。由于D端接地,当外部中断请求的正脉冲信号出现在CLK端时,Q端输出为0, 或

或 为低,外部中断向单片机发出中断请求。利用P1接口的P1.0作为应答线,当CPU响应中断后,可在中断服务程序中采用两条指令撤除外部中断请求。

为低,外部中断向单片机发出中断请求。利用P1接口的P1.0作为应答线,当CPU响应中断后,可在中断服务程序中采用两条指令撤除外部中断请求。

ANL P1,#0FEH

ORL P1,#01H

第一条指令使P1.0为0,因P1.0与D触发器的异步置1端SD相连,Q端输出为1,从而撤除中断请求。第二条指令使P1.0变为1,Q=1,Q继续受CLK控制,即新的外部中断请求信号又能向单片机申请中断。第二条指令是必不可少的,否则将无法再次形成新的外部中断。

(5)中断响应时间 中断响应时间是指从中断请求标志位置位到CPU开始执行中断服务程序的第一条指令所持续的时间。CPU并非每时每刻对中断请求都予以响应,不同的中断请求其响应时间也是不同的,因此中断响应时间形成的过程较为复杂。以外部中断为例,CPU在每个机器周期的S5P2(图2-13)期间采样其输入引脚 或

或 端的电平,如果中断请求有效,则置位中断请求标志位IE0或IE1,然后在下1个机器周期再对这些值进行查询,这就意味着中断请求信号的低电平至少应维持1个机器周期。这时,如果满足中断响应条件,则CPU响应中断请求,在下1个机器周期执行一条硬件长调用指令“LACLL”,使程序转入中断矢量入口。该调用指令执行时间是2个机器周期,因此外部中断响应时间至少需要3个机器周期,这是最短的中断响应时间。

端的电平,如果中断请求有效,则置位中断请求标志位IE0或IE1,然后在下1个机器周期再对这些值进行查询,这就意味着中断请求信号的低电平至少应维持1个机器周期。这时,如果满足中断响应条件,则CPU响应中断请求,在下1个机器周期执行一条硬件长调用指令“LACLL”,使程序转入中断矢量入口。该调用指令执行时间是2个机器周期,因此外部中断响应时间至少需要3个机器周期,这是最短的中断响应时间。

如果中断请求不能满足前面所述的3个条件而被阻断,则中断响应时间将延长。例如1个同级或更高级的中断正在进行,则附加的等待时间取决于正在进行的中断服务程序的长度。如果正在执行的一条指令还没有进行到最后1个机器周期,则附加的等待时间为1~3个机器周期(因为一条指令的最长执行时间为4个机器周期)。如果正在执行的指令是RETI指令或访问IE或IE的指令,则附加的等待时间在5个机器周期之内(最多用1个机器周期完成当前指令,再加上最多4个机器周期完成下一条指令)。

若系统中只有1个中断申请,则中断响应时间为3~8个机器周期。

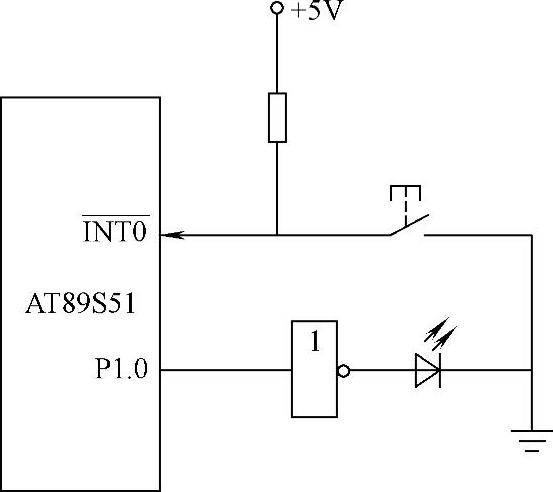

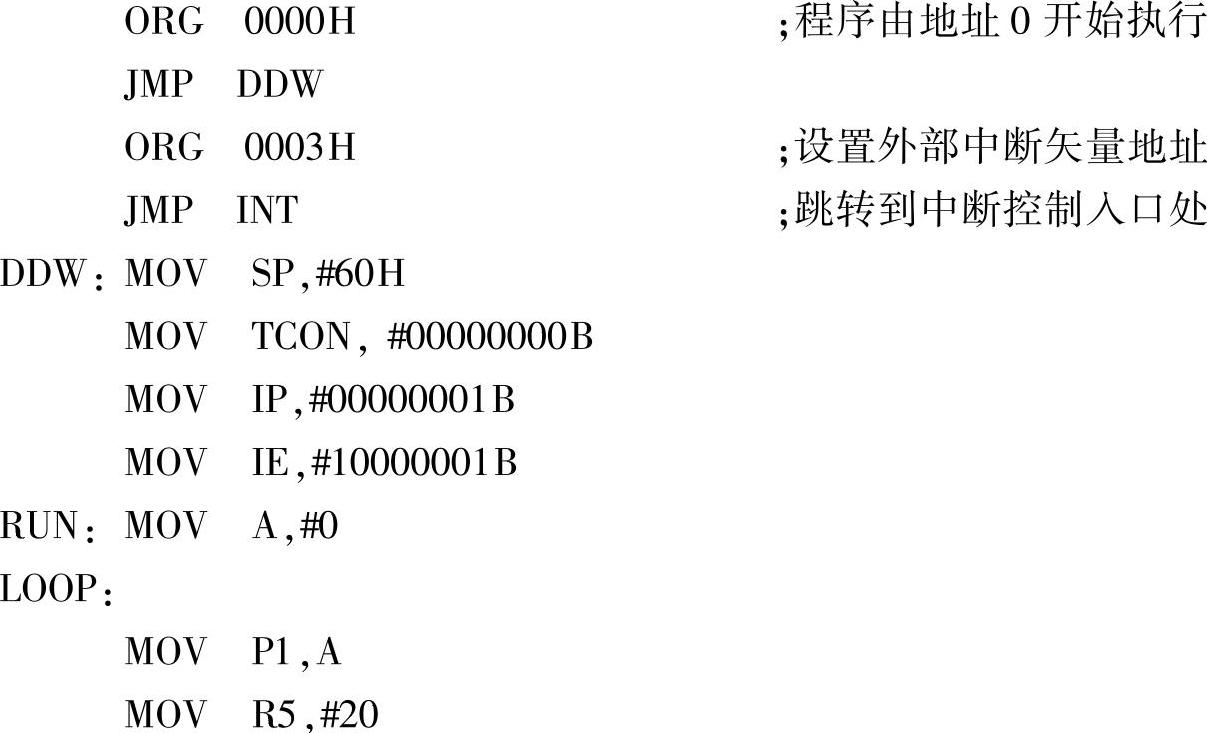

例1:要求每次按动按键,使外接发光二极管LED改变一次亮灭状态,其接线如图6-8所示。

解: 输入按键信号,P1.0输出改变LED状态。

输入按键信号,P1.0输出改变LED状态。

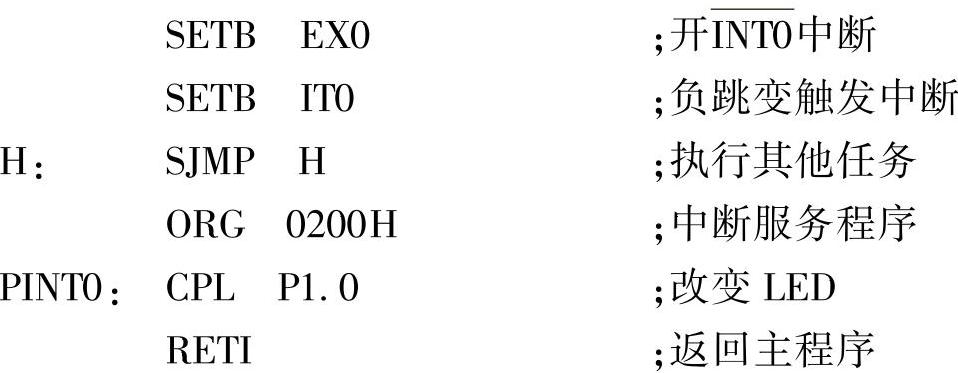

1)跳变触发:每次跳变引起一次中断请求。

图6-8 例1接线图

主程序如下:

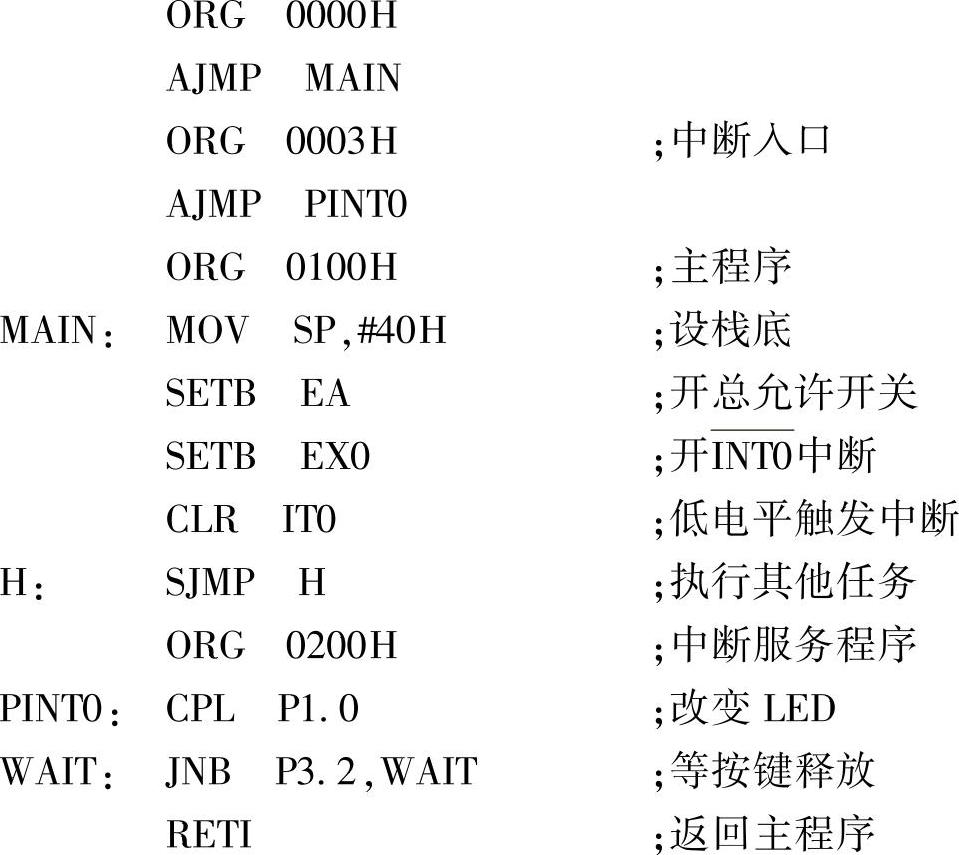

2)电平触发:避免一次按键引起多次中断响应。

①软件等待按键释放。

②硬件清除中断信号。

主程序如下:

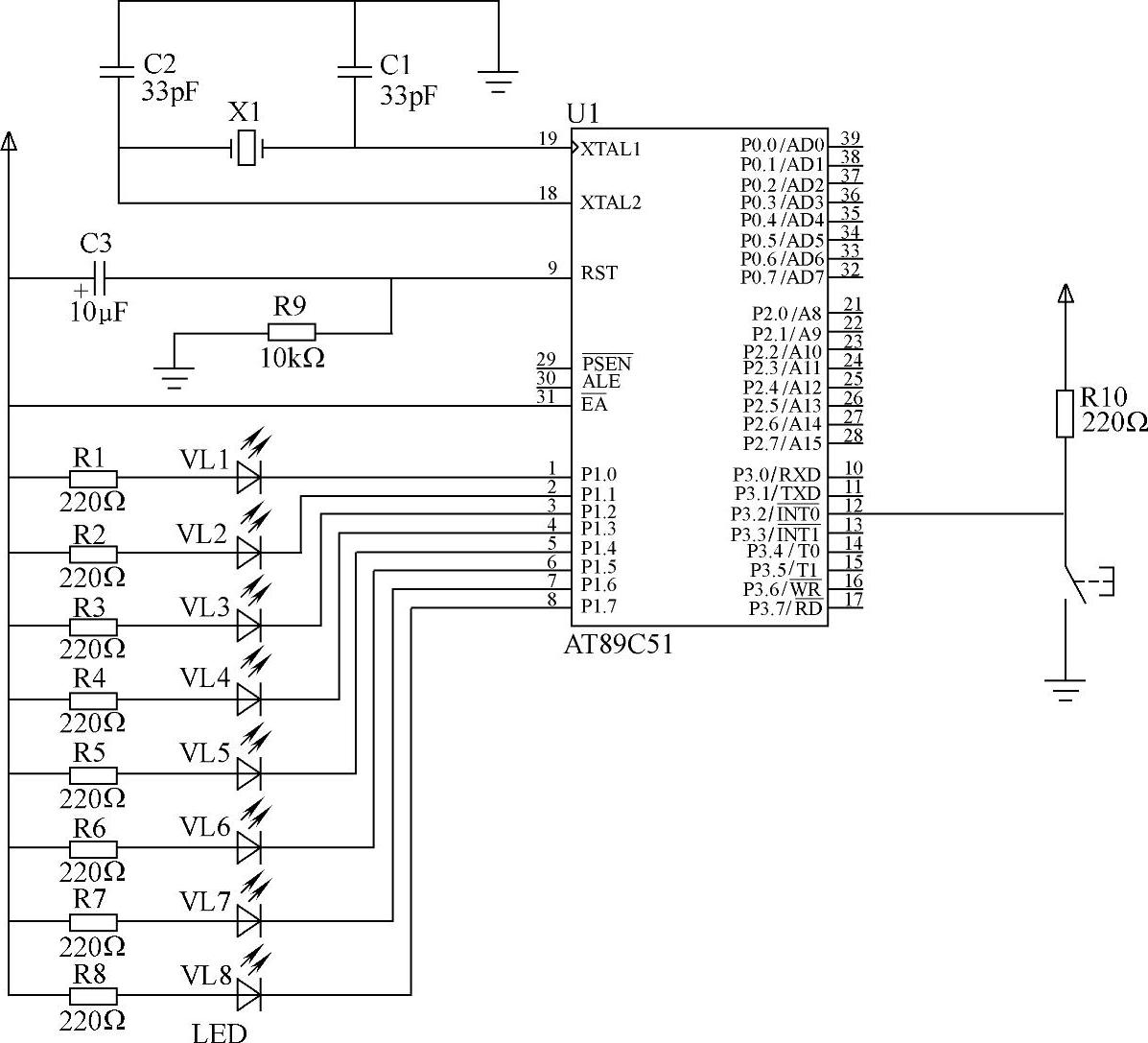

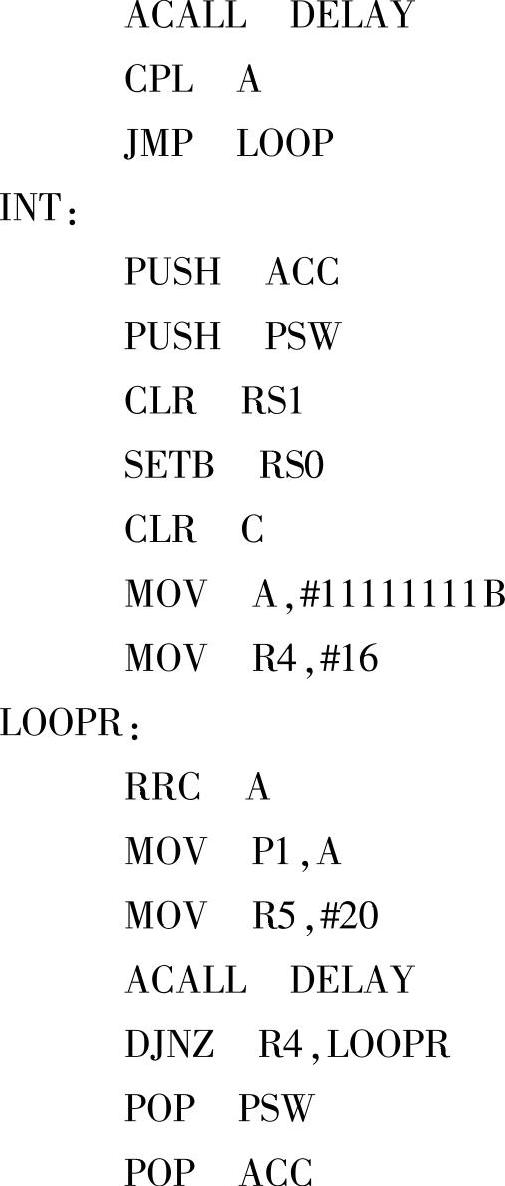

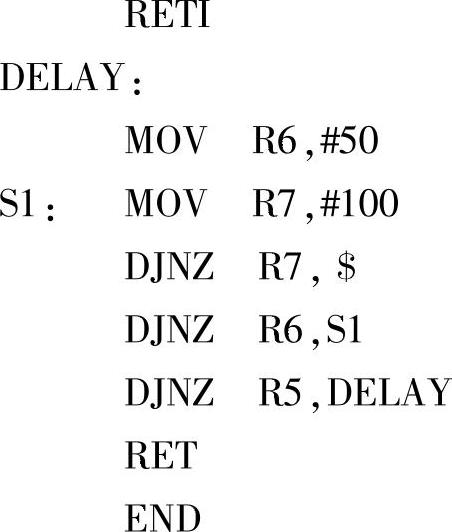

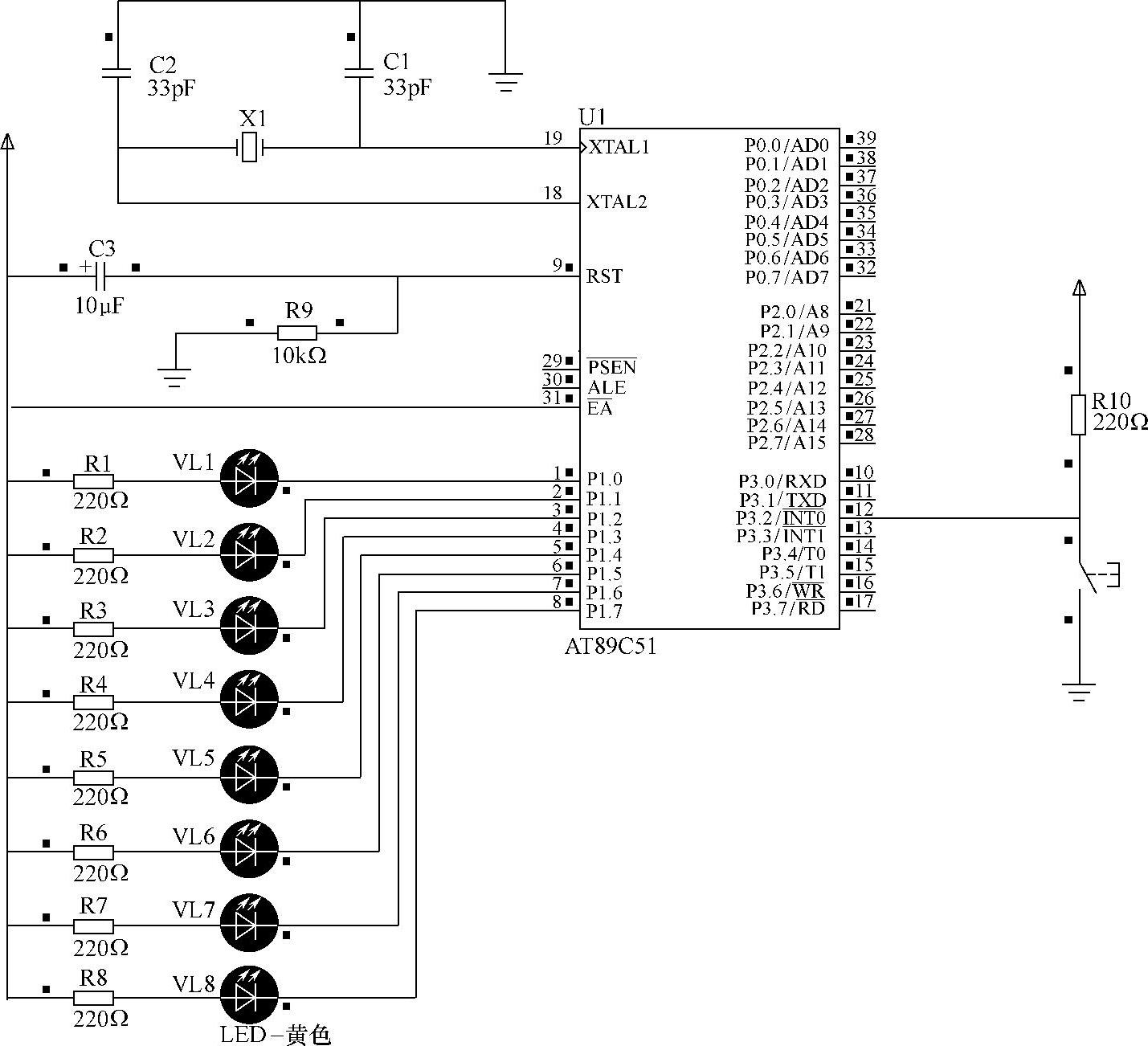

例2:要求没有中断申请时,8个发光二极管同时闪烁,每次按动按键,发光二极管轮流闪烁2遍。

接线图如图6-9所示。

开始,P1接口灯闪烁,中断产生,P1接口呈流水灯操作。

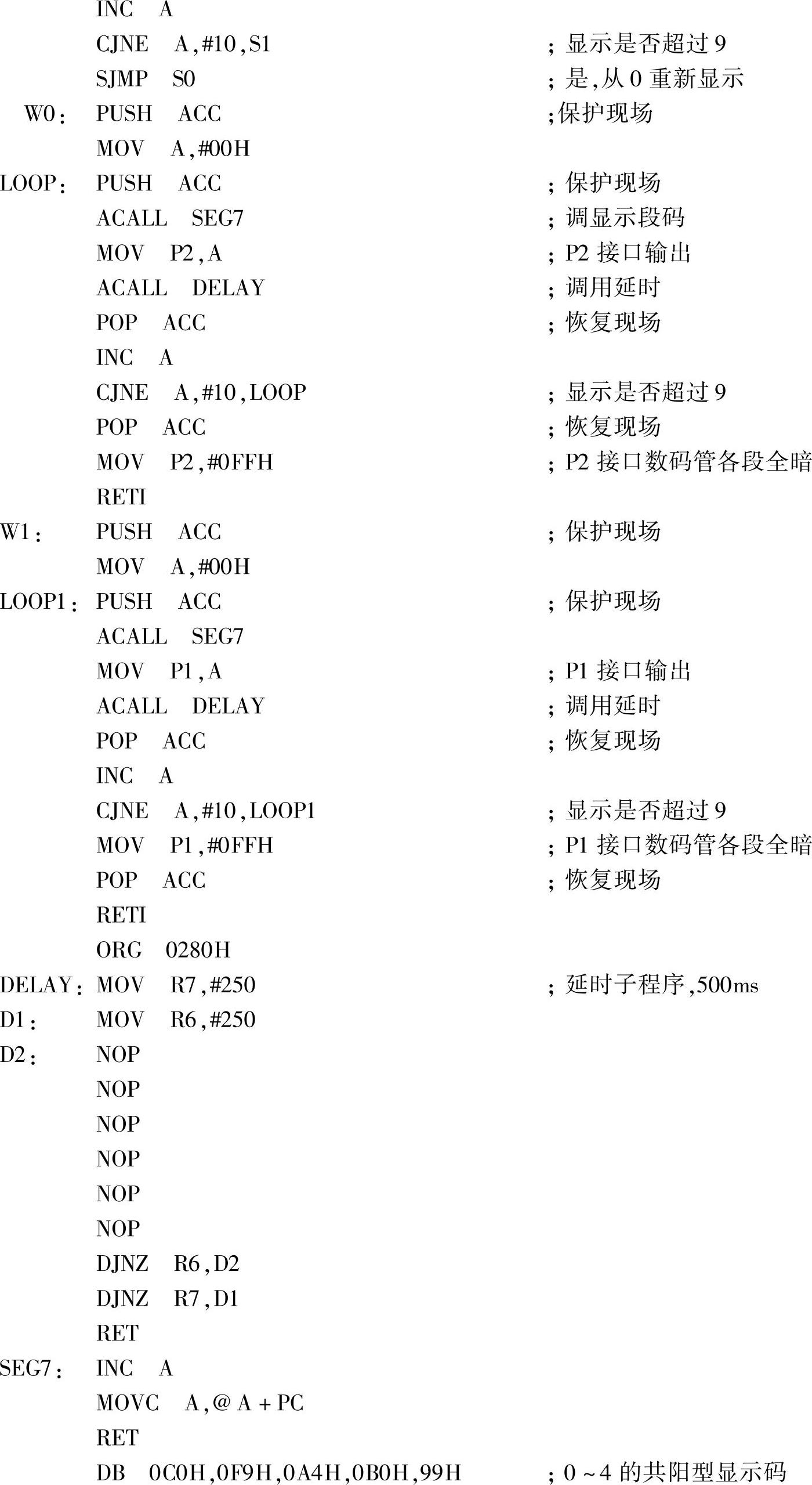

参考程序如下:

图6-9 例2接线图

主程序运行结果如图6-10所示,中断后运行结果如图6-11所示。

图6-10 主程序运行结果(见彩插)

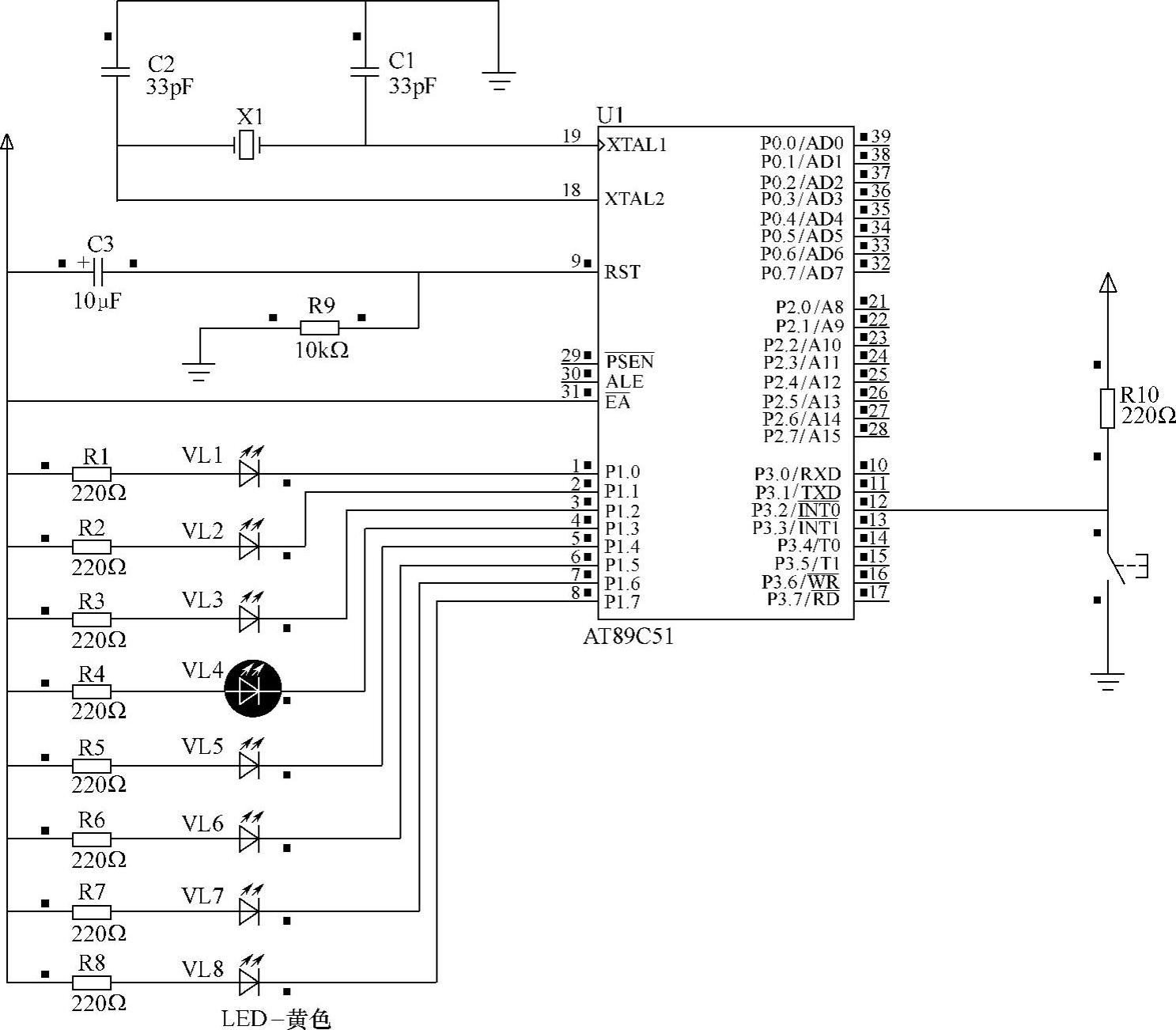

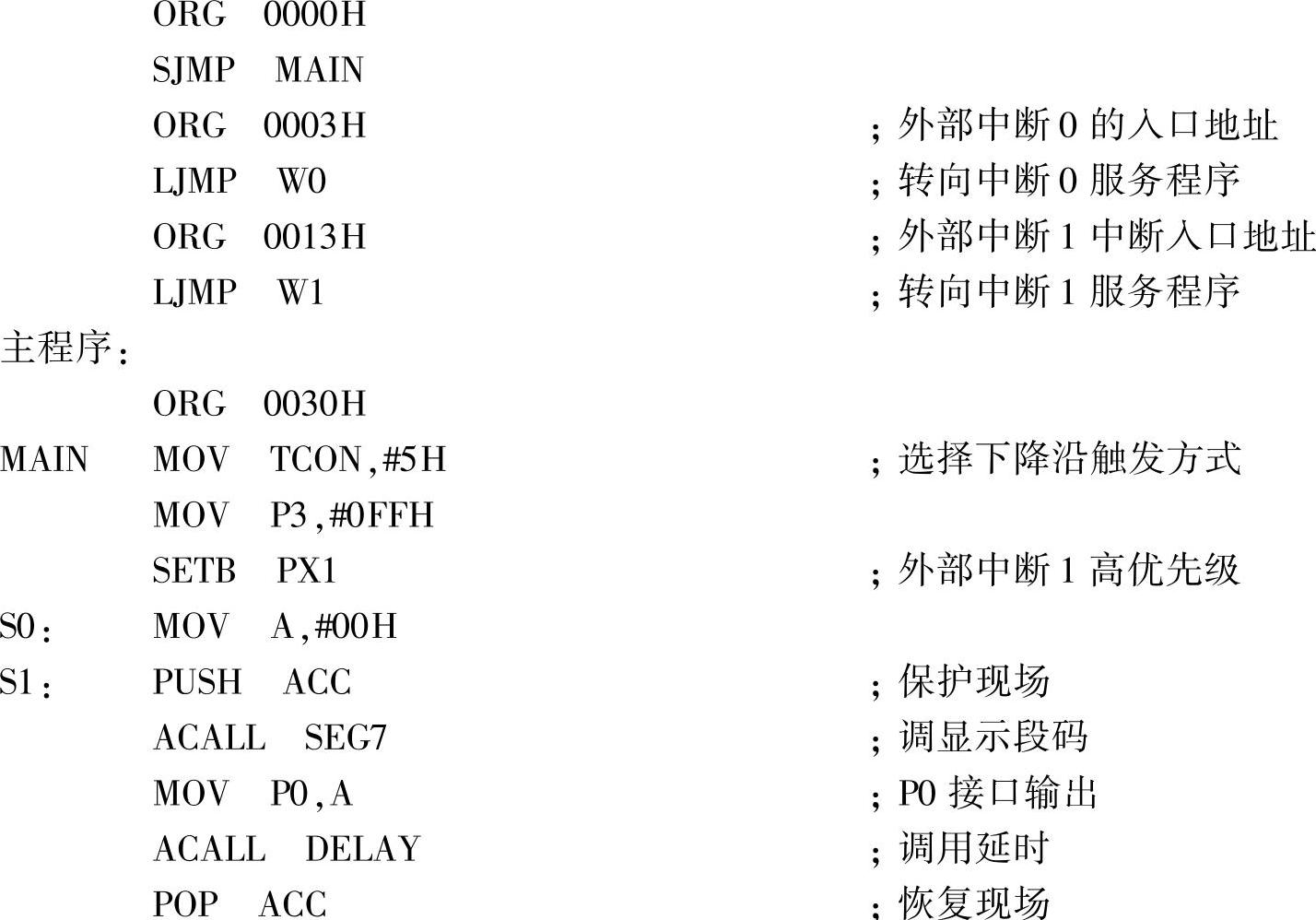

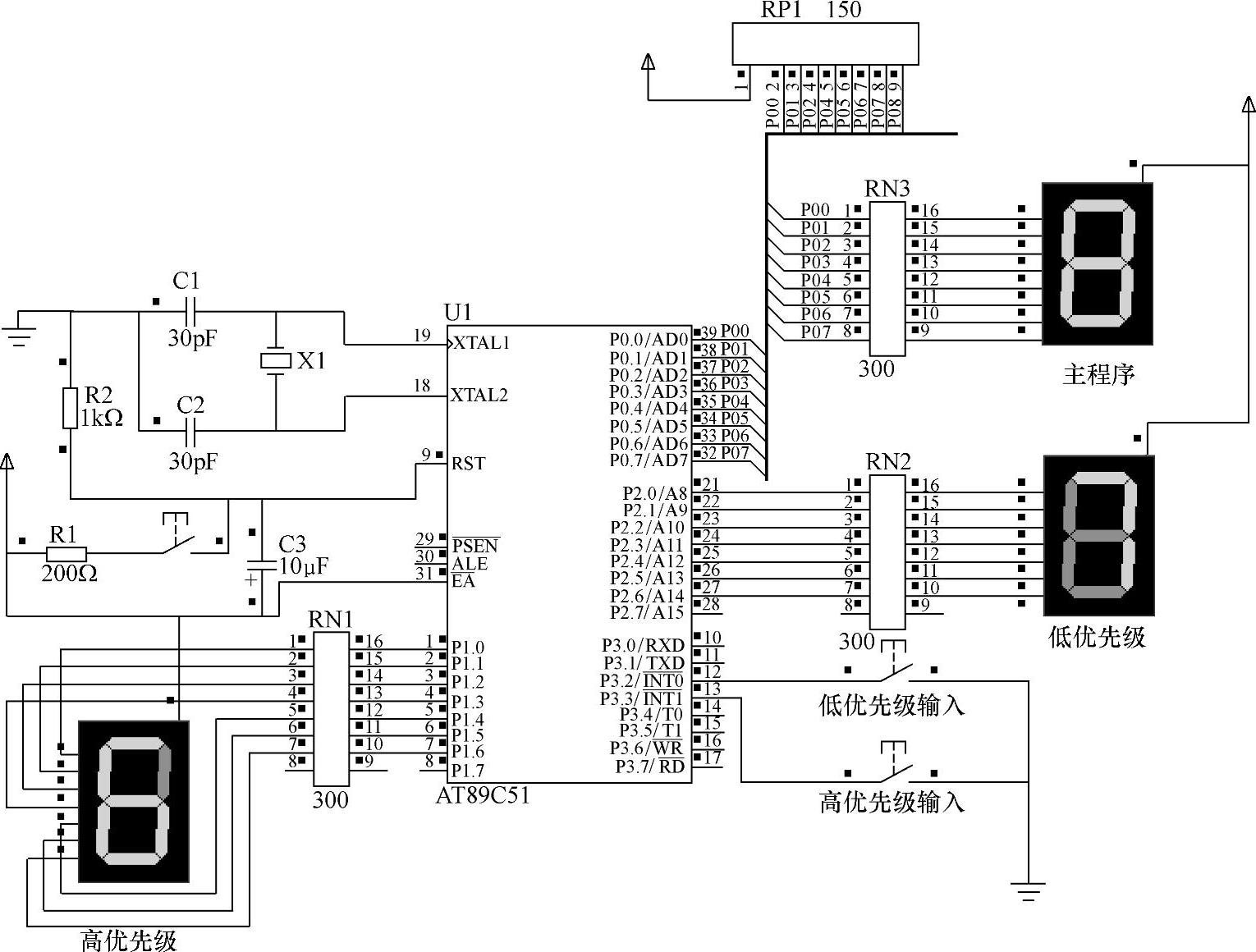

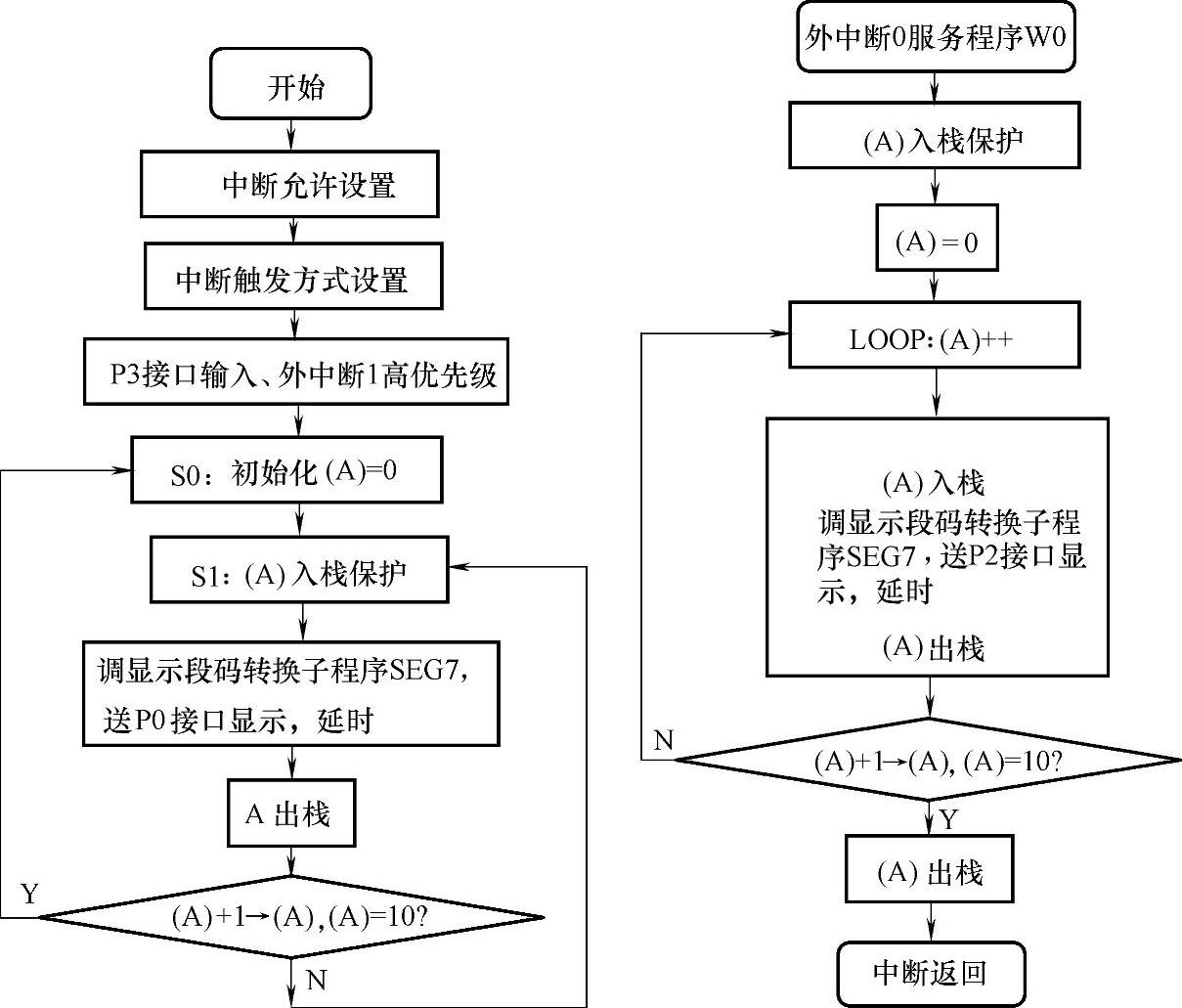

例3:AT89C51单片机中断优先级应用。

利用AT89C51单片机主程序控制P0接口数码管循环显示0~9;外中断0、外中断1发生时分别在P2、P1接口依次显示0~9;外中断1为高优先级,外中断0为低优先级。高优先级可以中断低优先级,低优先级不能中断高优先级,同一优先级不能相互中断。

接线如图6-12所示,流程如图6-13所示。在Protues中调用的器件有单片机AT89C51、瓷片电容CAP(30PF)、晶振CRYSTAL(12MHz)、电阻RES、排阻RX8、按钮BUTTON、电解电容CAP-ELEC、7SEG-COM-AN-GRN、排阻RESPACK-8。

图6-11 中断后运行结果(见彩插)

参考程序如下:

图6-12 接线图(见彩插)

图6-13 流程图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。