80c51系列单片机中涉及中断控制的有3个方面4个特殊功能寄存器:①中断请求控制寄存器,有定时/计数器和外中断控制寄存器tcon,串行控制寄存器scon;②中断允许控制寄存器ie;③中断优先级控制寄存器ip。

(1)中断请求控制寄存器 、

、 、t0、t1中断请求标志放在tcon中,串行中断请求标志放在scon中。

、t0、t1中断请求标志放在tcon中,串行中断请求标志放在scon中。

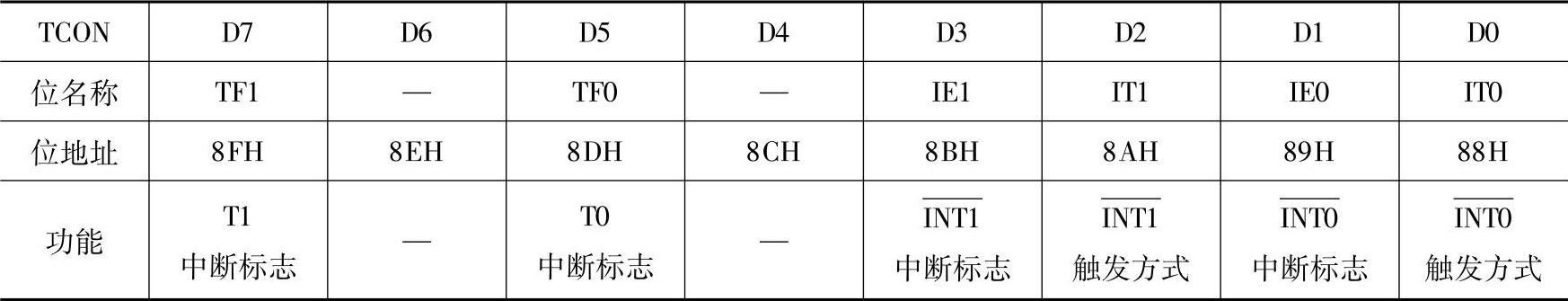

tcon的结构、位名称、位地址和功能见表41。

表4-1 tcon的结构、位名称、位地址和功能

1)tcon.7 tf1:定时器t1的溢出中断标志。t1被启动计数后,从初值,做加1计数,计满溢出后由硬件置位tf1,同时向cpu发出中断请求,此标志一直保持到cpu响应中断后才由硬件自动清0(也可由软件查询该标志,并由软件清0)。

2)tcon.5 tf0:定时器t0溢出中断标志,其操作功能与tf1相同。

3)tcon.3 ie1:外部中断1中断申请标志。ie1=1,外部中断1向cpu申请中断。

4)tcon.2 it1:外部中断1触发方式控制位。当it1=0时,外部中断1控制为电平触发方式。在这种方式下,cpu在每个机器周期的s5p2期间对(p33)引脚采样,若为低电平,则认为有中断申请,随即使ie1标志置位;若为高电平,则认为无中断申请,或中断申请已撤除,随即使ie1标志复位。在电平触发方式中,cpu响应中断后不能由硬件自动清除ie1标志,也不能由软件清除ie1标志,所以,在中断返回之前必须撤消引脚上的低电平,否则将再次中断导致出错。

5)tcon.1 ie0:外部中断0中断申请标志,其操作功能与ie1相同。

6)tcon.0 it0:外部中断0触发方式控制位,其操作功能与it1相同。

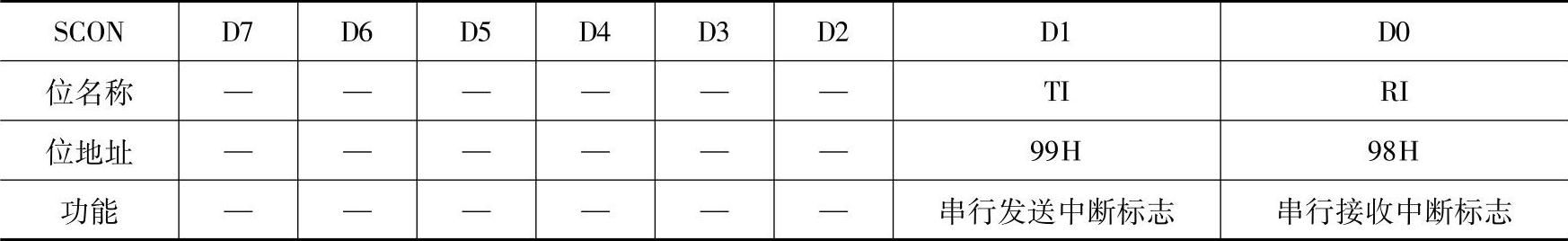

(2)scon寄存器中的中断标志scon是串口控制寄存器,其低两位ti和ri锁存串口的发送中断标志和接收中断标志。scon的结构、位名称、位地址和功能见表42。

1)scon.1 ti:串口发送中断标志。cpu将数据写入发送缓冲器sbuf时,就启动发送,每发送完一个串行帧,硬件将使ti置位。但cpu响应中断时并不清除ti,必须由软件清除。

表4-2 scon的结构、位名称、位地址和功能

2)scon.0 ri:串行接收中断标志。在串口允许接收时,每接收完一个串行帧,硬件将使ri置位。同样,cpu在响应中断时不会清除ri,必须由软件清除。

80c51系统复位后,tcon和scon均清0,应用时要注意各位的初始状态。

(3)ie寄存器中断的开放和禁止标志mcs-51系列单片机的5个中断源都是可屏蔽中断,其中断系统内部设有一个专用寄存器ie,用于控制cpu对各中断源的开放或屏蔽。ie寄存器各位的定义见表4-3。

表4-3 ie寄存器各位的定义

(https://www.xing528.com)

(https://www.xing528.com)

1)ea:cpu中断允许总控制位。ea=1,cpu开中断;ea=0,cpu关中断,且屏蔽所有5个中断源。

2)ex0:外中断 中断允许控制位。ex0=1,

中断允许控制位。ex0=1, 开中断;ex0=0,

开中断;ex0=0, 关中断。

关中断。

3)ex1:外中断 中断允许控制位。ex1=1,

中断允许控制位。ex1=1, 开中断;ex1=0,

开中断;ex1=0, 关中断。

关中断。

4)et0:定时/计数器t0中断允许控制位。et0=1,t0开中断;et0=0,t0关中断。

5)et1:定时/计数器t1中断允许控制位。et1=1,t1开中断;et1=0,t1关中断。

6)es:串口中断(包括串发、串收)允许控制位。es=1,串口开中断;es=0,串口关中断。

说明:80c51系列单片机对中断实行两级控制,总控制位是ea,每一中断源还有各自的控制位。首先要ea=1,其次还要自身的控制位置“1”。

(4)中断优先级寄存器ip mcs-51系列单片机的中断源优先级是由中断优先级寄存器ip进行控制的。5个中断源总共可分为2个优先级,每一个中断源都可以通过ip寄存器中的相应位设置成高级中断或低级中断,因此,cpu对所有中断请求只能实现两级中断嵌套。ip寄存器各位的定义见表4-4。

表4-4 ip寄存器各位的定义

1)ip.4 ps:串口中断优先控制位。ps=1,设定串口为高优先级中断;ps=0,设定串口为低优先级中断。

2)ip.3 pt1:定时器t1中断优先控制位。pt1=1,设定定时器t1中断为高优先级中断;pt1=0,设定定时器t1中断为低优先级中断。

3)ip.2 px1:外部中断1中断优先控制位。px1=1,设定外部中断1为高优先级中断;px1=0,设定外部中断1为低优先级中断。

4)ip.1 pt0:定时器t0中断优先控制位。pt0=1,设定定时器t0中断为高优先级中断;pt0=0,设定定时器t0中断为低优先级中断。

5)ip.0 px0:外部中断0中断优先控制位。px0=1,设定外部中断0为高优先级中断;px0=0,设定外部中断0为低优先级中断。

当系统复位后,ip低5位全部清0,所有中断源均设定为低优先级中断。

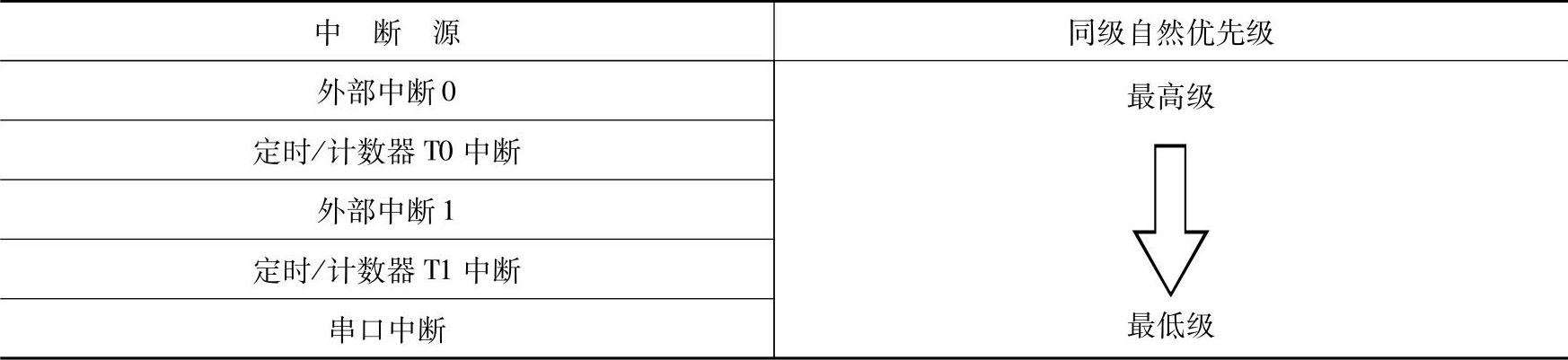

如果几个同一优先级的中断源同时向cpu申请中断,cpu通过内部硬件查询逻辑,按自然优先级顺序确定先响应哪个中断请求。自然优先级由硬件形成,排列见表4-5。

表4-5 自然优先级的排列

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。