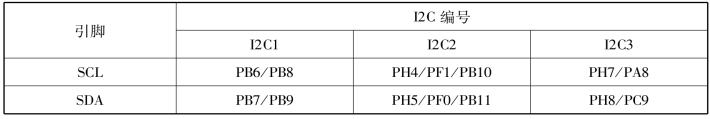

与SPI类似,STM32内置了三个I2C,对应复用的GPIO如表10-1所示。

表10-1 STM32F407的I2C

每个I2C的架构如图10-9所示,除了SDA与SCL外,端口还多了一个SMBA。系统管理总线(SMBus)是一个双线制接口。各器件可通过它在彼此之间或者与系统的其余部分进行通信。由于它以I2C的工作原理为基础,因此归在了I2C模块。实际使用I2C时,不需要使用SMBA。

图10-9 STM32F407的I2C架构

1.时钟控制

从架构图可以看到,SCL是双向传输的,作为主设备时,时钟主要由时钟控制寄存器CCR控制产生并由SCL输出;作为从设备时,SCL处于接收状态,接收主设备传输过来的时钟。

CCR寄存器可选择I2C通信的标准或快速模式,分别对应100kbps与400kbps的通信速率。在快速模式下对于SCL时钟的占空比可选Tlow/Thigh=2或Tlow/Thigh=16/9模式,通过占空比的设置适应从器件的特性。一般来说,这两个模式的比例差别并不大,若不是要求非常严格的从器件,都可以正常工作。

CCR寄存器中还有一个12位的配置因子CCR,它与I2C外设的输入时钟源共同作用,产生SCL时钟。与SPI类似,STM32的I2C外设都挂载在APB1总线上,使用APB1的时钟源PCLK1。SCL输出时钟公式计算如下:

标准模式100kbps:Thigh=CCR×Tpclk1,Tlow=CCR×Tpclk1

快速模式400kbps,当Tlow/Thigh=2时:Thigh=CCR×Tpclk1,Tlow=2×CCR×Tpclk1

快速模式400kbps,当Tlow/Thigh=16/9时:Thigh=9×CCR×Tpclk1,Tlow=16×CCR×Tpclk1

因此设置SCL时钟频率,可根据PCLK1与配置因子配合,比如fpclk1=42MHz时,配置100kbps,计算CCR的过程如下:

PCLK1的周期Tpclk1=1/42000000,SCL(实际就是波特率)的周期TSCL=1/100000,由(https://www.xing528.com)

Thigh=Tlow=CCR×Tpclk,TSCL=Thigh+Tlow

计算出CCR=210。

配置400kpbs,TSCL=1/400000,占空比Tlow/Thigh=16/9时,由

Tlow=16*CCR×Tpclk1,Thigh=9×CCR×Tpclk1,TSCL=Thigh+Tlow

计算出CCR=4.2。

配置400kpbs,TSCL=1/400000,占空比Tlow/Thigh=2时,由

Tlow=2×CCR×Tpclk1,Thigh=1×CCR×Tpclk1,TSCL=Thigh+Tlow

计算出CCR=35。

从计算结果可以看出,不同传送速度与不同占空比计算出的CCR有不同的数值。由于CCR寄存器只能存储整数,若CCR的计算结果为3.5,只能向下取整为3,这样得到的波特率会稍小或者稍大,但由于是同步通信,因此结果对传输的影响不大。

2.数据控制

STM32的I2C模块的数据控制寄存器包含数据寄存器(DR)、地址寄存器(OAR)与PEC寄存器。根据前面学习的I2C知识,SDA线上传送的信息包括两种:地址与数据。因此寄存器DR专门用于I2C的数据接收存储与发送存储,地址寄存器专门用于存放地址,而PEC寄存器则存放数据校验的结果(在控制寄存器中使能了数据校验)。

当在从机模式,接收到设备地址信号时,数据移位寄存器会把接收到的地址与STM32自身的I2C地址寄存器的值做比较,以便响应主机的寻址。STM32自身的I2C地址可通过修改自身地址寄存器修改,支持同时使用两个I2C设备地址,两个地址分别存储在OAR1和OAR2中。

3.控制逻辑

配置控制寄存器(CR1/CR2)的参数,对I2C的工作模式进行控制,读取状态寄存器(SR1与SR2),可以获取I2C的工作状态。除此之外,控制逻辑还负责控制产生I2C中断信号、DMA请求及各种I2C的通信信号(起始、停止、响应信号等)。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。