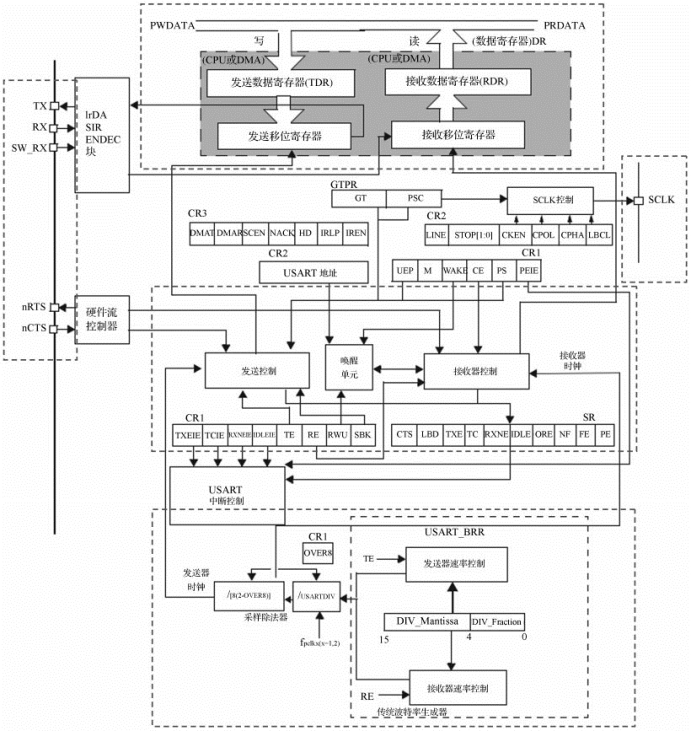

STM32内置的USART结构框图如图7-7所示。

图7-7 STM32内置的USART结构框图

1.引脚分配

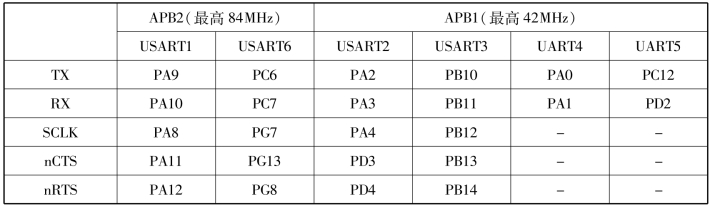

表7-1是STM32F407ZGTx的串口引脚分布,其中USART1和USART6挂在了APB2上,其余的挂在了APB1上。

当USART设置为UART时,SCLK不使用;当UART不使用硬件流时,nCTS、nRTS不使用。

表7-1 STM32F407ZGTx串口引脚分布

2.数据寄存器(USART-DR)

USART的数据寄存器(USART_DR)只有低9位有效,并且第9位数据是否有效取决于USART控制寄存器1(USART_CR1)的M位设置。M位为0表示8位数据字长,M位为1表示9位数据字长。这与51系列单片机的串口模式类似,有第9位可供使用,一般用于多机通信,在点对点的通信中,一般使用8位数据长度。

USART_DR包含了已发送的数据或接收到的数据。与51系列单片机的SBUF类似,USART_DR实际包含了两个寄存器,一个是专门用于发送的可写TDR,一个是专门用于接收的可读RDR。当进行发送操作时,向USART_DR写入的数据会自动存储在TDR内;当进行读取操作时,向USART_DR读取数据会自动提取RDR数据:这也与51系列单片机的SBUF的使用方法完全一样。

TDR寄存器有数据时,会将数据送入发送移位寄存器进行移位输出,移位寄存器的输出端连接至TX(GPIO);当接收移位寄存器从RX(GPIO)接收二进制数,收满数据后,会将其送至RDR寄存器。TDR、RDR与总线相连,负责与总线交换数据。

在使能奇偶校验位的情况下进行接收时,从MSB位中读取的值为接收到的奇偶校验位的值。

3.控制寄存器

控制器用于设置USART的工作模式、唤醒、中断、使能等,使用的寄存器有CR1、CR2、CR3、SR、GTPR等。下面将这些寄存器的含义列出来供查阅参考。

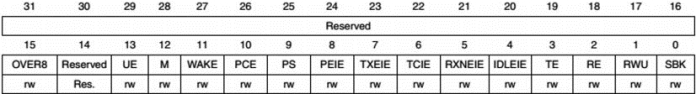

(1)USART_CR1(控制寄存器1)。

寄存器分布如图7-8所示:

图7-8 USART-CR1分布

具体使用的位设置说明如下:

·位15(OVER8,过采样模式):8倍过采样在智能卡、IrDA和LIN模式下不可用。

0:16倍过采样

1:8倍过采样

·位13(UE,使能):该位清0后,USART预分频器和TX输出将停止,并会结束当前字节传输以降低功耗。此位由软件置1和清0。

0:禁止USART预分频器和TX输出

1:使能USART

·位12(M,字长):该位决定了字长。该位由软件置1或清0。

0:1起始位,8数据位,n停止位

1:1起始位,9数据位,n停止位

·位11(WAKE,唤醒):该位决定了USART的唤醒方法。该位由软件置1或清0。

0:空闲线路

1:地址标记

·位10(PCE,奇偶校验控制使能):该位选择硬件奇偶校验控制(生成和检测)。使能奇偶校验控制时,计算出的奇偶校验位(如果M=1,则为第9位;如果M=0,则为第8位)被插入MSB位置,并对接收到的数据检查奇偶校验位。此位由软件置1和清0。

0:禁止奇偶校验控制

1:使能奇偶校验控制

·位9(PS,奇偶校验选择):该位用于在使能奇偶校验生成/检测(PCE位置1)时选择奇校验或偶校验。该位由软件置1和清0。将在当前字节的后面选择奇偶校验。

0:偶校验

1:奇校验

·位8(PEIE,PE中断使能):此位由软件置1和清0。

0:禁止中断

1:当USART_SR寄存器中PE=1时,生成USART中断

·位7(TXEIE,TXE中断使能):此位由软件置1和清0。

0:禁止中断

1:当USART_SR寄存器中TXE=1时,生成USART中断

·位6(TCIE,传送完成中断使能):此位由软件置1和清0。

0:禁止中断

1:当USART_SR寄存器中TC=1时,生成USART中断

·位5(RXNEIE,RXNE中断使能):此位由软件置1和清0。

0:禁止中断

1:当USART_SR寄存器中ORE=1或RXNE=1时,生成USART中断

·位4(IDLEIE,IDLE中断使能):此位由软件置1和清0。

0:禁止中断

1:当USART_SR寄存器中IDLE=1时,生成USART中断。

·位3(TE,发送器使能):该位使能发送器,由软件置1和清0。

0:禁止发送器

1:使能发送器

·位2(RE,接收器使能):该位使能接收器,由软件置1和清0。

0:禁止接收器

1:使能接收器并开始搜索起始位

·位1(RWU,接收器唤醒):该位决定USART是否处于静音模式,由软件置1和清0,并可在识别出唤醒序列时由硬件清0。

0:接收器处于活动模式

1:接收器处于静音模式

·位0(SBK,发送断路):该位用于发送断路字符,由软件置1和清0。该位应由软件置1,并在断路停止位期间由硬件重置。

0:不发送断路字符

1:发送断路字符

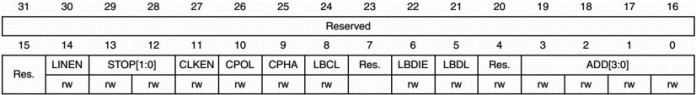

(2)USART_CR2(控制寄存器2)。

寄存器分布如图7-9所示:

图7-9 USART_CR2分布

具体使用的位设置说明如下:

·位14(LINEN,LIN模式使能):此位由软件置1和清0。

0:禁止LIN模式

1:使能LIN模式

·位13~位12(STOP[1:0]):停止位,这些位用于设定停止位的位数。0.5个停止位和1.5个停止位不适用于UART4和UART5。

00:1个停止位

01:0.5个停止位

10:2个停止位

11:1.5个停止位

·位11(CLKEN,时钟使能):该位允许用户使能SCLK引脚,不适用于UART4和UART5。

0:禁止SCLK引脚

1:使能SCLK引脚

·位10(CPOL,时钟极性):该位允许用户在同步模式下选择SCLK引脚上时钟输出的极性。它与CPHA位结合使用可获得所需的时钟/数据关系。不适用于UART4和UART5。

0:空闲时SCLK引脚为低电平

1:空闲时SCLK引脚为高电平

·位9(CPHA,时钟相位):该位允许用户在同步模式下选择SCLK引脚上时钟输出的相位。它与CPOL位结合使用可获得所需的时钟/数据关系。不适用于UART4和UART5。

0:在时钟第一个变化沿捕获数据

1:在时钟第二个变化沿捕获数据

·位8(LBCL,最后一个位时钟脉冲):该位允许用户在同步模式下选择与发送的最后一个数据位(MSB)关联的时钟脉冲是否必须在SCLK引脚上输出。不适用于UART4和UART5。

0:最后一个数据位的时钟脉冲不在SCLK引脚上输出

1:最后一个数据位的时钟脉冲在SCLK引脚上输出

·位6(LBDIE,LIN断路检测中断使能):该位用于断路中断屏蔽(使用断路分隔符进行断路检测)。

0:禁止中断

1:当USART_SR寄存器中LBD=1时,生成中断

·位5(LBDL,lin断路检测长度):该位用于选择11位断路检测或10位断路检测。

0:10位断路检测

1:11位断路检测

·位3~位0(ADD[3:0],USART节点的地址):该位用于指定USART节点的地址。该位域将在多处理器通信时于静音模式下使用,以通过地址标记检测进行唤醒。

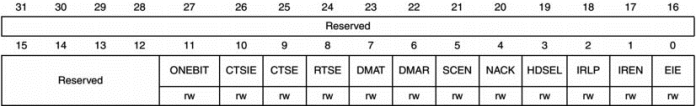

(3)USART_CR3(控制寄存器3)。

寄存器分布如图7-10所示:

图7-10 USART_CR3分布

具体位设置说明如下:

·位11(ONEBIT,一个采样位方法使能):该位允许用户选择采样方法。选择一个采样位方法后,将禁止噪声检测标志(NF)。

0:三个采样位方法

1:一个采样位方法

·位10 CTSIE(CTS中断使能):该位不适用于UART4和UART5。

0:禁止中断

1:当USART_SR寄存器中CTS=1时,生成中断

·位9(CTSE,CTS使能):如果该位在发送数据时使nCTS输入无效,数据会在停止之前完成发送。如果该位使nCTS有效时数据已写入数据寄存器,则将延迟发送,直到nCTS有效。该位不适用于UART4和UART5。

0:禁止CTS硬件流控制

1:使能CTS模式,仅当nCTS输入有效(连接到0)时才发送数据

·位8(RTSE,RTS使能):仅当接收缓冲区中有空间时才会请求数据。缓冲区发送完当前字符后应停止发送数据。该位可以在接收数据时使nRTS输出有效(连接到0)。不适用于UART4和UART5。

0:禁止RTS硬件流控制

1:使能RTS中断

·位7(DMAT,DMA使能发送器):该位由软件置1/复位。

1:发送使能DMA模式(https://www.xing528.com)

0:发送禁止DMA模式

·位6(DMAR,DMA使能接收器):该位由软件置1/复位。

1:针对接收使能DMA模式

0:针对接收禁止DMA模式

·位5(SCEN,智能卡模式使能):该位用于使能智能卡模式,不适用于UART4和UART5。

0:禁止智能卡模式

1:使能智能卡模式

·位4(NACK,智能卡NACK使能):该位不适用于UART4和UART5。

0:出现奇偶校验错误时禁止NACK发送

1:出现奇偶校验错误时使能NACK发送

·位3(HDSEL,双工选择):该位用于选择单线半双工模式。

0:未选择半双工模式

1:选择半双工模式

·位2 IRLP(IrDA低功耗):该位用于选择正常模式或低功耗IrDA模式。

0:正常模式

1:低功耗模式

·位1 IREN(IrDA模式使能):该位由软件置1和清0。

0:禁止IrDA

1:使能IrDA

·位0 EIE(错误中断使能):多缓冲区通信(USART_CR3中DMAR=1)如果发生帧错误、上溢错误或出现噪声标志(USART_SR寄存器中FE=1或ORE=1或NF=1),则需要使用错误中断使能位来使能中断生成。

0:禁止中断

1:当USART_CR3中的DMAR=1并且USART_SR中的FE=1或ORE=1或NF=1时,生成中断

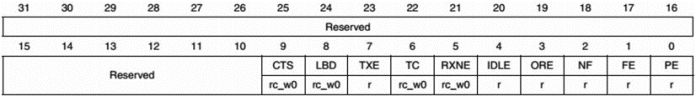

(4)USART_SR(状态寄存器)。

寄存器分布如图7-11所示:

图7-11 USART_SR分布

具体位设置说明如下:

·位9(CTS,CTS标志):如果CTSE位置1,当nCTS输入变换时,此位由硬件置1。通过软件将该位清0(通过向该位写入0)。如果USART_CR3寄存器中CTSIE=1,则会生成中断。不适用于UART4和UART5。

0:nCTS状态线上未发生变化

1:nCTS状态线上发生变化

·位8(LBD,LIN断路检测标志):检测到LIN断路时,该位由硬件置1。通过软件将该位清0(通过向该位写入0)。如果USART_CR2寄存器中LBDIE=1,则会生成中断。

0:未检测到LIN断路

1:检测到LIN断路

·位7(TXE,发送数据寄存器为空):当TDR寄存器的内容已传输到移位寄存器时,该位由硬件置1。如果USART_CR1寄存器中TXEIE=1,则会生成中断。通过对USART_DR寄存器执行写入操作,将该位清0。单缓冲区发送数据期间使用该位。

0:数据未传输到移位寄存器

1:数据传输到移位寄存器

·位6(TC,发送完成):如果已完成对包含数据的帧的发送并且TXE置1,则该位由硬件置1。如果USART_CR1寄存器中TCIE=1,则会生成中断。该位由软件序列清0(读取USART_SR寄存器,然后写入USART_DR寄存器)。TC位也可以通过程序写入“0”来清0。建议仅在多缓冲区通信时使用此清0序列。

0:传送未完成

1:传送已完成

·位5(RXNE,读取数据寄存器不为空):当RDR移位寄存器的内容已传输到USART_DR寄存器时,该位由硬件置1。如果USART_CR1寄存器中RXNEIE=1,则会生成中断。通过对USART_DR寄存器执行读入操作,将该位清0。RXNE标志也可以通过向该位写入0来清0。建议仅在多缓冲区通信时使用此清0序列。

0:未接收到数据

1:已准备好读取接收到的数据

·位4(IDLE,检测到空闲线路):检测到空闲线路时,该位由硬件置1。如果USART_CR1寄存器中IDLEIE=1,则会生成中断。该位由软件序列[1]清0(先读入USART_SR寄存器,然后读入USART_DR寄存器的过程)。直到RXNE位本身已置1时(即当出现新的空闲线路时)IDLE位才会被再次置1。

0:未检测到空闲线路

1:检测到空闲线路

·位3(ORE,上溢错误):在RXNE=1的情况下,当移位寄存器中当前正在接收的字准备好传输到RDR寄存器时,该位由硬件置1。如果USART_CR1寄存器中RXNEIE=1,则会生成中断。该位由软件序列清0(先读入USART_SR寄存器,然后读入USART_DR寄存器的过程)。当该位置1时,RDR寄存器的内容不会丢失,但移位寄存器会被覆盖。如果EIE位置1,则在进行多缓冲区通信时会对ORE标志生成一个中断。

0:无上溢错误

1:检测到上溢错误

·位2(NF,检测到噪声标志):当在接收的帧上检测到噪声时,该位由硬件置1。该位由软件序列清0(先读入USART_SR寄存器,然后读入USART_DR寄存器的过程)。

0:未检测到噪声

1:检测到噪声

·位1(FE,帧错误):当检测到去同步化、过渡的噪声或中断字符时,该位由硬件置1。该位由软件序列清0(先读入USART_SR寄存器,然后读入USART_DR寄存器的过程)。该位不会生成中断,因为该位出现的时间与本身生成中断的RXNE位出现的时间相同。如果传输中同时导致帧错误和上溢错误,仅有ORE位被置1。

0:未检测到帧错误

1:检测到帧错误或中断字符

·位0(PE,奇偶校验错误):当接收器模式下发生奇偶校验错误时,该位由硬件置1。该位由软件序列清0(读取状态寄存器,然后对USART_DR数据寄存器执行读或写访问)。将PE位清0前必须等待RXNE标志被置1。如果USART_CR1寄存器中PEIE=1,则会生成中断。

0:无奇偶校验错误

1:奇偶校验错误

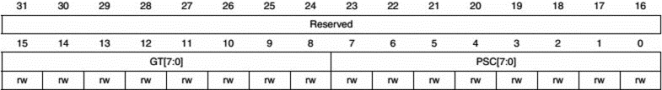

(5)USART_GTPR(预分频器寄存器)。

寄存器分布如图7-12所示:

图7-12 USART_GTPR分布

具体位设置说明如下:

·位15:8(GT[7:0],保护时间值):该位提供保护时间值(以波特时钟数为单位),用于智能卡模式。经过此保护时间后,发送完成标志置1。该位不适用于UART4和UART5。

·位7:0(PSC[7:0],预分频器值):该位不适用于UART4和UART5。

✧在IrDA低功耗模式下,PSC[7:0]=IrDA。低功耗波特率用于预分频器编程,通过分频获取更低的功耗,根据寄存器中给出的值(8个有效位)对源时钟进行分频:

00000000:保留,默认值,源时钟1分频

00000010:源时钟2分频

……

✧在正常IrDA模式下:PSC必须设置为00000001。

✧在智能卡模式下([7:5]不起作用):

PSC[4:0](预分频器值)

该位用于预分频器编程,进行系统时钟分频,以提供智能卡时钟。将寄存器中给出的值(5个有效位)乘以2,得出源时钟频率的分频系数:

00000:保留,不编程此值

00001:源时钟2分频

00010:源时钟4分频

00011:源时钟6分频

……

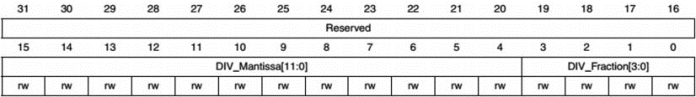

(6)USART_BRR(波特率寄存器)。

如果TE或RE位分别被禁止,则波特率计数器会停止计数。该寄存器用于计算波特率。

寄存器分布如图7-13所示:

图7-13 USART_BRR分布

具体位设置说明如下:

·位15:4(DIV_Mantissa[11:0]):这12个位用于定义USART除数(USARTDIV)的尾数,实际上代表着整数。

·位3:0(DIV_Fraction[3:0]):这4个位用于定义USART除数(USARTDIV)的小数,计算小数时除以16,得到小数数值。当OVER8=1时,不考虑DIV_Fraction[3:0]位,且必须将该位保持清0。

4.小数波特率生成器

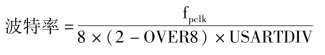

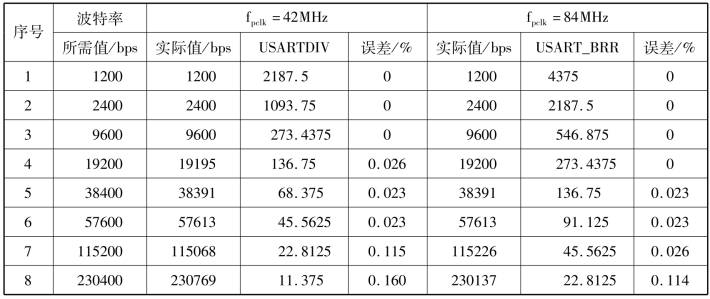

USART的发送器和接收器使用相同的波特率。计算公式如下:

其中,fpclk为USART时钟频率,时钟可以是APB1或者APB2;OVER8为USART_CR1寄存器的OVER8位对应的值;USARTDIV是一个存放在波特率寄存器(USART_BRR)中的无符号浮点数。其中DIV_Mantissa[11:0]位定义USARTDIV的整数部分,DIV_Fraction[3:0]位定义USARTDIV的小数部分,DIV_Fraction[3:0]位只有在OVER8位为0时有效,否则必须清0。

比如,USART_BRR值为0x271,如果OVER8=0,则DIV_Mantissa=39、DIV_Fraction=1,那么整数为39,USARTDIV的小数为1/16=0.0625,最终USARTDIV的值为39.0625。

反过来,假设OVER8=0,USARTDIV值为21.65,小数DIV_Fraction=16×0.65=10.4≈10,则DIV_Fraction[3:0]为0xA,整数DIV_Mantissa=21,DIV_Mantissa[11:0]为0x15,所以USART_BRR值为0x15A。

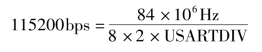

波特率的常用值有2400bps、9600bps、19200bps、115200bps。以USART1、115200bps为例计算USARTDIV。其中USART1的时钟为APB2,时钟频率为84MHz,fPLCK=84MHz,OVER8=0,波特率为115200bps,则

计算得到USARTDIV=45.57。则整数部分DIV_Mantissa=45,DIV_Mantissa[11:0]为0x2D,小数部分通过计算DIV_Fraction=0.57×16=9.12≈9,得到DIV_Fraction[3:0]为0x9。所以USART_BRR的值为0x2D9。

这里要注意的是,虽然STM32使用了小数波特率生成器和高频的时钟源,但是波特率还是存在误差,比如按照上述计算值代入波特率计算公式,得到的波特率为115226bps,存在0.026%的误差,这在允许范围之内。如果波特率为9600,计算得USARTDIV=546.875,USART_BRR=0x222E,反推的波特率也为9600bps,误差率为0,计算误差如表7-2所示。

表7-2 使用不同波特率在不同时钟下的误差(16倍过采样时,OVER8=0)

5.校验控制

使用校验位时,串口传输的长度将是8位的数据帧加上1位的校验位,总共9位,所以此时USART_CR1寄存器的M位需要设置为1。要启动奇偶校验控制,只需将USART_CR1寄存器的PCE位置1。奇偶校验由硬件自动完成。启动了奇偶校验控制之后,系统在发送数据帧时会自动添加校验位,在接收数据时会自动验证校验位。接收数据时如果出现奇偶校验位验证失败,系统会将USART_SR寄存器的PE位置1,并可以产生奇偶校验中断。

使能了奇偶校验控制后,每个字符帧的格式变成:起始位+数据帧+校验位+停止位。

6.中断控制

USART可以有多个中断请求事件,见表7-3。事件标志都可以引发中断。

表7-3 USART中断请求

7.发送与接收流程

(1)发送器。

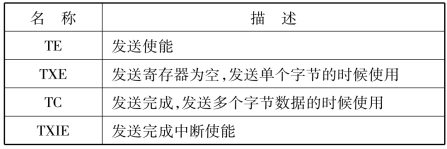

当USART_CR1寄存器的发送使能位TE置1时,启动数据发送,发送移位寄存器的数据会在TX引脚输出,如果是同步模式,SCLK也输出时钟信号。

当发送使能位TE置1之后,发送器开始会先发送一个空闲帧(一个数据帧长度的高电平),接下来就可以往USART_DR寄存器中写入要发送的数据。在写入最后一个数据后,如果USART状态寄存器(USART_SR)的TC位为1,表示数据传输完成;如果USART_CR1寄存器的TCIE位置1,将产生中断事件。需要使用的控制位如表7-4所示。

表7-4 USART发送控制位

(2)接收器。

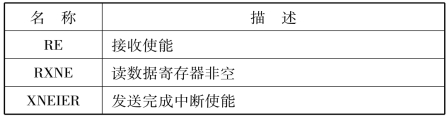

如果将USART_CR1寄存器的RE位置1,则使能USART接收,同时接收器在RX线开始搜索起始位。在确定起始位后USART接收器根据RX线电平状态把数据存放在接收移位寄存器内。接收完成后把接收移位寄存器数据移到RDR内,并把USART_SR寄存器的RXNE位置1,同时如果USART_CR2寄存器的RXNEIE置1就可以产生中断。需要使用的控制位如表7-5所示。

表7-5 USART接收控制位

为得到更准确的信号,需要用一个比这个信号频率高的采样信号去检测,称为过采样。这个采样信号的频率大小决定最后得到源信号的准确度。一般频率越高,得到的准确度越高,但要得到的频率越高,采样信号也越困难,运算和功耗等也会增加。接收器可配置不同过采样技术,以实现从噪声中提取有效的数据。USART_CR1寄存器的OVER8位用来选择不同的采样方法,如果OVER8位设置为1,则采用8倍过采样,即用8个采样信号采样一位数据;如果OVER8位设置为0,则采用16倍过采样,即用16个采样信号采样一位数据。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。