比如说有个时钟clk,频率是10MHz,那么把它进行2分频、4分频、6分频等操作,这叫作偶数分频。10MHz的信号进行2分频得到的是5MHz,4分频得到的是2.5MHz,以此类推。把它进行3分频、5分频、7分频等操作,这叫作奇数分频。

偶数分频

偶数分频实现方法一:偶数倍分频,通过计数器计数是完全可以实现的。如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。以此循环下去。这种方法可以实现任意的偶数分频。

偶数分频实现方法二:如进行N倍偶数分频,计数为0到N-1的循环。0到N/2-1是前一半计数,N/2到N-1是后一半计数。当计数过了一半时,即计数器counter不再小于N/2时,输出信号翻转;计数到N-1时,计数器清零。

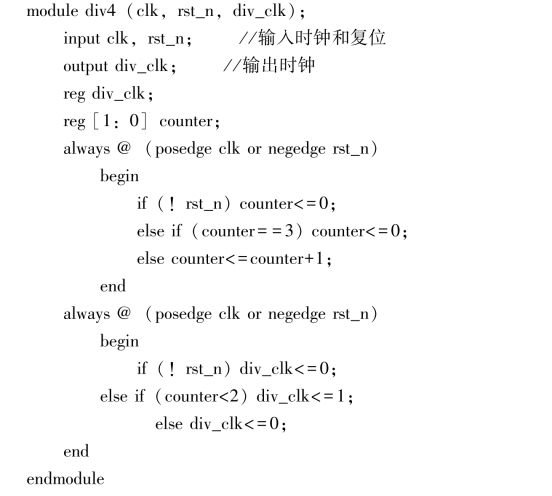

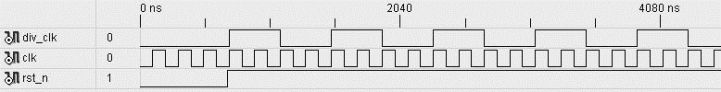

例17.35:设计一个4分频器。

实现原理:N=4,占空比50%,计数为0~3的循环。当计数小于一半时,输出信号div_clk输出1;计数器不再小于N/2时,输出信号div_clk输出0。

该4分频器的仿真结果如图17.48所示。

图17.48 偶数4分频器仿真结果

从图17.48可看出,每4个clk的时间长度,包含了一个完成的div_clk周期。

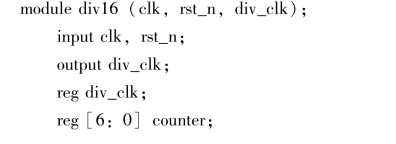

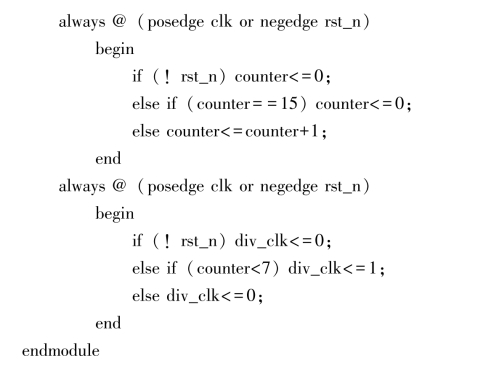

例17.36:设计一个16分频器。(https://www.xing528.com)

奇数分频

奇数分频的实现方法一:首先,完全可以通过计数器来实现,如进行三分频,通过待分频时钟上升沿触发计数器进行模三计数,当计数器计数到邻近值进行两次翻转,比如可以在计数器计数到1时,输出时钟进行翻转,计数到2时再次进行翻转。即是在计数值在邻近的1和2进行了两次翻转。这样实现的三分频占空比为1/3或者2/3。

奇数分频的实现方法二:如果要实现占空比为50%的三分频时钟,可以通过待分频时钟下降沿触发计数和上升沿同样的方法计数进行三分频,然后下降沿产生的三分频时钟和上升沿产生的时钟进行相或运算,即可得到占空比为50%的三分频时钟。这种方法可以实现任意的奇数分频。

例17.37:设计一个3分频计数器。

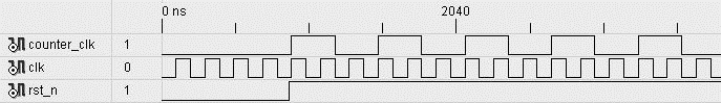

图17.49是3分频器的仿真结果。

图17.49 3分频器的仿真结果

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。