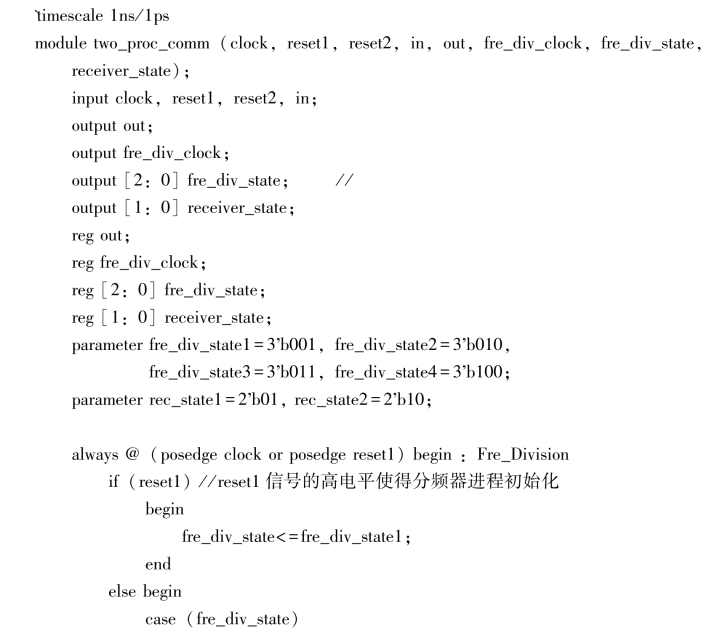

例17.34:编写一个双进程通信的有限状态机程序。

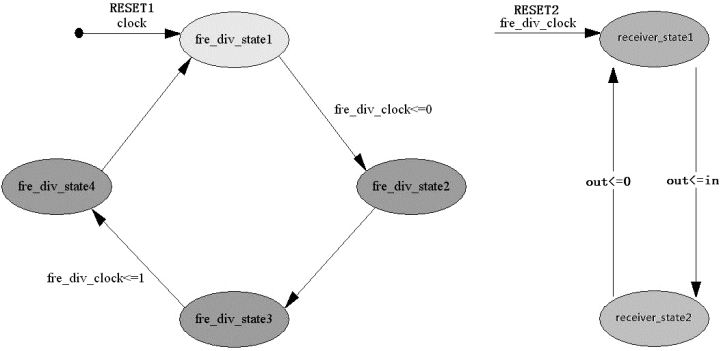

下面这个例子涉及两个进程之间的通信。如下图所示,左边进程1,4个状态从fre_div_state1~fre_div_state4,它在状态转换之间会生成一个分频信号fre_div_clock。把这个分频信号传递给右边的进程2作为进程2的触发时钟。进程2另外还有一个外界给它的输入in,进程2在状态转换之间对输入in做出反应,生成输出out。

图17.45 双进程通信的状态转换图

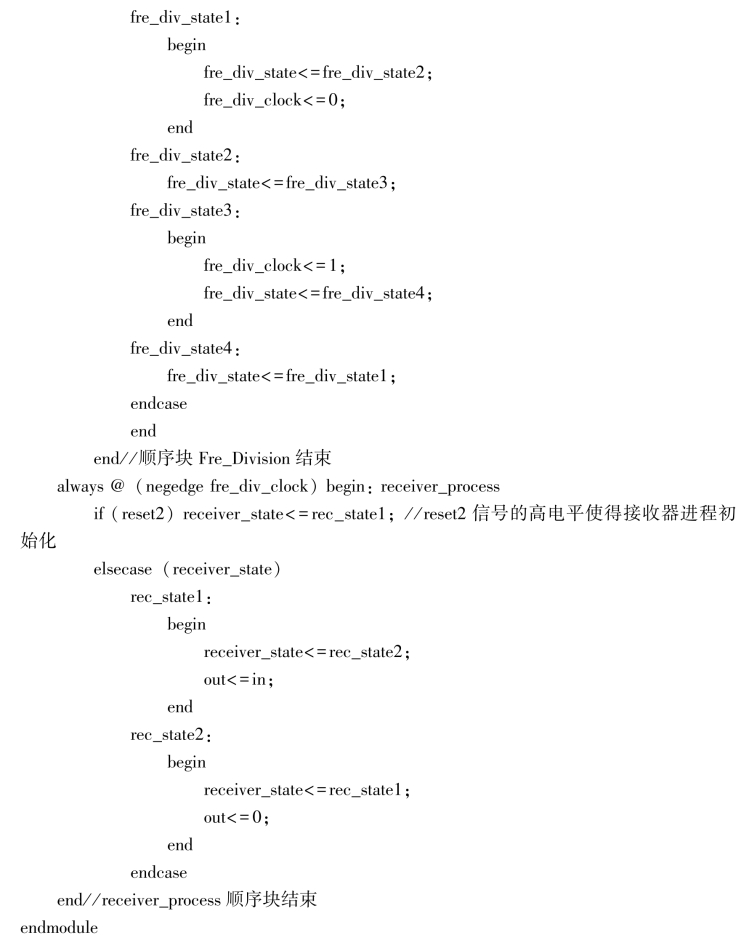

图17.46是Synplify综合的电路结构。左半边是分频器进程的,右半边是接收器进程的。分频器进程会产生一个fre_div_clock信号(图17.46正中间偏左的部分),该信号输送给接收器进程。输入的信号in通过一个D触发器(图17.46最右边部分),被传送给out。

图17.46 双进程通信综合的电路(https://www.xing528.com)

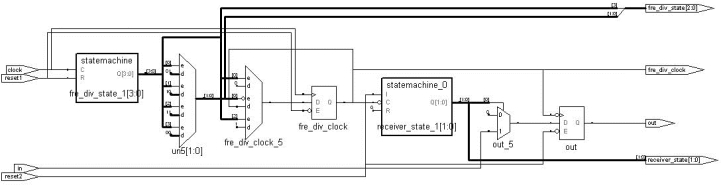

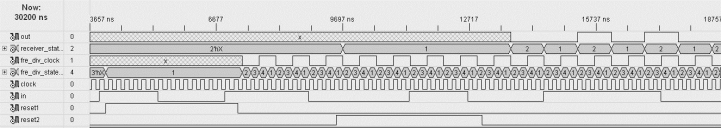

图17.47是仿真的结果。有两个清零信号,一个是控制分频器进程的reset1,另一个是控制接收器进程的reset2。系统启动之后,先给reset1赋值高电平,使得分频器进程初始化;然后给reset2赋值高电平,使得接收器进程初始化。

图17.47 双进程通信仿真的波形

clock信号的上升沿或者reset1信号的上升沿形成触发,进入分频器进程语句块执行。分频器进程有4个状态,把clock时钟4分频。

fre_div_clock信号是clock信号频率的四分之一。fre_div_clock信号的下降沿触发,进入接收器进程语句块。接收器进程里,把输入in信号传送给out。

fre_div_clock信号来自于clock信号,是两个进程之间沟通的桥梁。

这个例子仅仅是分频器进程通过分频时钟影响接收器进程,接收器进程还没法主动影响分频器进程。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。