在组合逻辑电路中,经常会出现一些妨碍电路正常工作的毛刺现象。这种毛刺现象,就叫作竞争冒险。

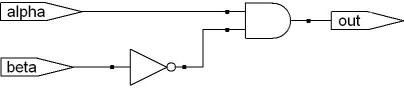

比如我们看图17.1这个电路:

图17.1 竞争与冒险实例图

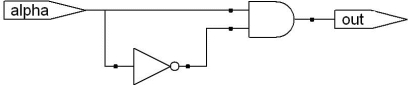

这个电路是把alpha和beta的非进行相与,结果赋值给out。光是这样看,读者可能会不觉得有问题,如果beta和alpha都是一个值呢?如图17.2所示:

图17.2 竞争与冒险实例图

这个电路的描述是“assign out=alpha&(~alpha);”,即alpha和自身的取反相与,结果赋值给out。按理说,一个值和自己的取反相与,应该永远等于0。但是要知道,非门是有延迟的,实际上,上面这个电路的工作波形应该是如下所示:

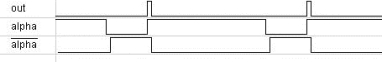

图17.3 竞争与冒险实例工作波形

看图17.3,由于alpha信号经过非门会有信号的延迟,这就导致输出out会产生不需要的尖峰。这个尖峰的宽度和非门的延迟有密切的关系。也就是说,当逻辑电路存在两个互补信号的输入的时候,有可能输出端就会产生意外干扰的脉冲。

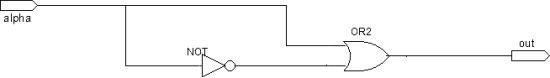

再看下面这个例子。见图17.4。图17.4是用Quartus II软件画出来的。

图17.4 竞争与冒险实例图

上面这个图17.4说的是alpha和自己的非做或运算。一个数和自己的非相或,结果应该永远是1。可是根据我们上面的分析,由于非门的延迟,上面这个电路的输出out应该会有尖峰毛刺的产生。

刚才说的是一个信号经过非门的情况。实际的电路往往不仅仅是非门,器件内部千万个逻辑门、各种连线、各种运算,都会产生延迟,各种制造工艺的不同也会造成延时的不同。之前设计的电路用的是这种器件,延时等特征都符合要求,换了一种电路,可能延时等特征就不符合要求了。甚至包括温度的变化,工作电压的波动等,都会对延迟造成影响。

尖峰毛刺,意味着边沿一定是很陡峭的,意味着这种电路存在着很多高频信号。早期使用分立元件设计逻辑电路的时候,由于可以单独使用电容滤波来滤掉这些高频的尖峰毛刺,所以尖峰毛刺的问题在早期的时候不太突出。另一个原因是早期的分立元件时代的数字电路设计的工作频率都很低,工作频率很多都低于MHz量级,工作频率低直接就抑制了大多数尖峰毛刺的生成。而现代的大规模集成电路,时钟频率很多都是几百MHz的量级。而大规模集成电路内部很少存在寄生电容电感,这就很难抑制尖峰毛刺,导致其不断的生成和继续传播。(https://www.xing528.com)

上面提到的自己和自己的非相与的例子,其数学表达式就是:alpha&(~alpha)。非门的存在导致其必然有尖峰毛刺存在。那么,有一些电路表达式在特殊情况下就会变成上面提到的这个表达式,比如:(alpha|beta)&((~alpha)|gamma)。当beta和gamma都为1时,该表达式就会化简为alpha&(~alpha),进而可能出现竞争与冒险。

当然并不是所有的信号变化都会产生竞争与冒险。对于alpha&(~alpha)这个表达式来说,观察前面的仿真波形图,在alpha从低变高的时候,就会产生毛刺;而alpha从高变低的时候就不会产生毛刺。

读者也可以自行分析alpha与自身的非做或运算的例子(即alpha|(~alpha))。在这个例子里,只有当alpha从高变低的时候,才会产生毛刺;alpha从低变高的时候就不会产生毛刺。

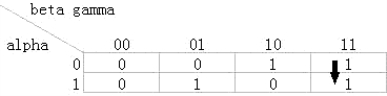

我们也可以从卡诺图上看出是否存在竞争与冒险现象。表达式(alpha|beta)&((~alpha)|gamma)的卡诺图如图17.5所示:

图17.5 竞争与冒险实例卡诺图

当beta和gamma都是1的时候,只要alpha从0变为1,就会产生毛刺。

图17.5{alpha,beta,gamma}从011变为111的时候,就会产生毛刺。读者也可以自行画出alpha与自身的非做或运算的例子(即alpha|(~alpha))的卡诺图,并分析信号如何变化时会产生毛刺。

那么怎么解决竞争与冒险的问题出现呢?在表达式里添加冗余项可不可以?我们知道竞争与冒险的出现是因为信号按照某个顺序变化了,比如上面这张图信号从011变化到了111就会有尖峰信号产生,如果不能永远杜绝信号的这种变化顺序,那么这种抑制竞争与冒险的方法就是失效的。所以添加冗余项这种方式不能够完全的消除竞争与冒险。

还有什么方法可以解决这个问题呢?我们可以考虑在输入信号里加入使能信号,只有输入信号稳定了,使能信号才使能。比如上面仿真波形看到的尖峰,这个尖峰是有宽度的。信号变化以后,等待这个宽度的时间再让使能信号使能,这就能抑制竞争与冒险。

另外还有一种方法可以解决竞争与冒险的问题,那就是使用格雷码。我们知道,尖峰毛刺产生的根本原因就是多个输入信号同时变化,这就会造成系统的不稳定。而格雷码的特征就是:当格雷码从一个数变化为相邻的另一个数时,只有一个数据位有变化,这就意味着它可以尽量避免出现二进制编码电路里经常会有的竞争与冒险现象。

对于某些工作频率不高的FPGA电路,可以采用添加电容的方式,抑制尖峰毛刺。

冒险只出现在信号发生变化的时刻,意味着信号的建立时间是冒险产生的主要时间段,而信号的保持时间则不是冒险产生的主要时间段。因此可以考虑使用采样脉冲来抑制冒险。采样脉冲的使用要用在信号的保持时间。也就是说,要在信号的保持时间才使得采样脉冲有效。这种方法有个缺点,就是必须得在合适的时间施加采样脉冲。使用这种方法意味着每一次面临这种问题都要单独去解决。不具有普遍性。

还有一种方法就是使用D触发器。D触发器是在时钟的触发下工作的,对输入信号的尖峰毛刺不敏感。

在设计电路的时候,为了避免竞争与冒险的问题,需要注意一些基本细节:比如尽量少使用锁存器,而应该尽量使用触发器和寄存器;译码器和比较器经常会产生尖峰毛刺,如果把译码器和比较器的输出作为后续电路的异步输入,意味着就有可能把毛刺导入后一级,这是要注意的;尽量避免使用RS触发器或者隐含的RS触发器,因为RS触发器有反馈支路,这样的反馈支路最容易产生尖峰毛刺;避免在一个模块里使用独立的多时钟,这种多时钟的独立性意味着任何可能性的随时发生,会造成尖峰毛刺的隐患;也要避免在一个模块里同时使用分频前和分频后的多时钟,因为这些时钟之间会有时钟歪斜,这也会造成尖峰毛刺的隐患;如果出现了尖峰毛刺,最好不要想着往延迟小的支路添加延迟线,因为这种延迟线对一个工艺可能可以通过,对另一个工艺可能结果就不一样了;尽量避免对仿真器基于绝对的信任,不要完全相信仿真器能帮你解决竞争与冒险的问题,有些问题它是发现不了的,毕竟仿真器仿真的结果和实际综合的结果并不是一样的。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。