Altera是与Xilinx齐名的FPGA开发领域的头部公司,Altera的Quartus II就是其与Xilinx的ISE齐名的FPGA开发软件。

Quartus II可以在多个平台(包括Windows、Linux以及Unix)上使用,它提供了脚本和完善的用户图形界面的设计方式。和ISE一样,Quartus II平台无论在运行速度、界面集成化、功能使用上都具有很好的用户口碑。Quartus II支持Altera的IP核,可以直接利用其一些宏功能模块库。这些宏功能模块库都是非常成熟的模块,有利于简化Quartus II的设计复杂性和加快其设计速度。Quartus II也支持Altera的SOC设计。除此之外,Quartus II结合了DSP Builder和Matlab/Simulink,极大地方便了各种DSP系统的实现。

使用Quartus II进行FPGA开发,也基本要经历和ISE类似的开发流程,即:源代码输入→源代码编辑→综合→功能仿真→布局布线后仿真→制作电路板→编程下载→调试→出产品。如果过程中有不满意的地方,还需要退回到之前的某个步骤重新走流程。

下面我们就来具体的看一下Quartus II的开发流程。本书介绍的Quartus II版本号为Quartus II 13.0(64-bit),并未安装在虚拟机里,而是直接安装在著者的win7 64位系统下。

首先双击桌面的Quartus II快捷方式,打开Quartus II 13.0。如图15.1所示。

图15.1 桌面Quartus II图标

系统会弹出一个欢迎页,如图15.2所示,点击矩形框1的位置可以创立一个新工程Project。或者如果不喜欢这个欢迎页,可以选中矩形框2,让下次不显示该欢迎页。点击图15.2的右上角符号×可以关闭该欢迎页。我们选择点击右上角×并关闭该欢迎页。

系统会弹出如图15.3所示的主工作界面。矩形框1的区域是菜单栏,这和ISE很类似。可以点击菜单栏相应的菜单,然后选择下一级菜单来做很多别的操作。图15.3的矩形框2区域是工作区,矩形框3的区域是项目导航器,即包括项目架构和源文件列表等,矩形框4的区域是在选中了项目导航器的内容后可以执行的任务的区域,矩形框5是诊断信息区。

图15.2 Quartus II欢迎页

图15.3 Quartus II工作界面

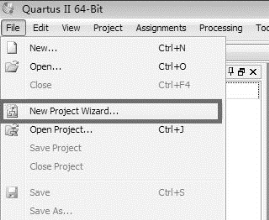

我们依次点击上图的菜单File-New ProjectWizard,如下图15.4所示。

图15.4 新建Quartus II工程

系统会弹出如图15.5所示的新工程向导New ProjectWizard的对话框,这个对话框会说明新工程向导会包含哪些内容。点击Next>,进入下一页。

图15.5 新建Quartus II工程

系统会弹出如图15.6所示的新工程向导的第一页:Directory,Name,Top-Level Entity。我们之前在介绍ISE的时候,介绍了一个点亮LED的例子。那个例子里我们把FPGA的某个管脚连接到了LED上,通过控制FPGA来点亮LED。

图15.6 新建Quartus II工程

那个例子里,仿真的结果显示LED是一直高电平驱动的。我们下面依然要用一个点亮LED的例子来介绍Quartus II,这个例子里会使用脉冲信号来驱动LED,而不是一直使用高电平信号驱动。

在上面这个页面,我们依次设置好工程的路径、输入工程名字、输入顶层模块设计实体的名字,然后点击Next>,进入下一步。系统会弹出如图15.7所示的对话框,问是否要创建刚才设置工程路径的目录,点击Yes。

图15.7 新建Quartus II工程的对话框

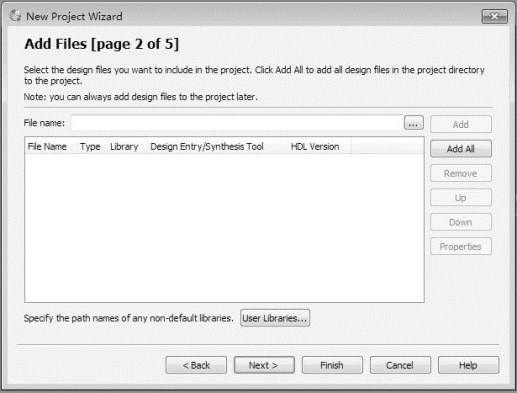

系统会弹出如图15.8所示的第二个页面。如果之前有编写相应的文件,在该页面可以把需要添加到项目的文件添加到该工程,这里我们直接点击Next>,进入下一页。

图15.8 新建Quartus II工程

系统会弹出如下图15.9所示的第三个页面。在这个页面可以设置器件家族、封装、管脚数、速度等级,还可以选择是否让系统自动选择匹配器来确定目标器件。

图15.9 新建Quartus II工程

我们点开其中的器件家族Family下拉菜单,该下拉菜单包含了Altera的很多家族的器件,比如Arria、Cyclone、Hardcopy、MAX、Stratix等系列。我们先在Family下拉菜单选择Stratix II系列,封装Package下拉菜单选择FBGA,管脚数有484、672、780、1020、1508几种,我们选择484管脚。速度等级Speed grade包括3、4、5、any和fastest几种,我们选择5。目标器件Target device选择由匹配器自动器件选择,Companion device选择默认就行。点击Next>。

图15.10 新建Quartus II工程

系统会弹出如图15.10所示的第四个页面。在这个页面可以设置综合工具、仿真工具、验证工具,以及板级的时序、符号、信号完整性和边界扫描。我们可以点击其对应下拉菜单进行选择,仿真器选择ModelSim-Altera。也可以先不选择,到后面建立好工程以后,再选择。点击Next>,进入下一步。

图15.11 新建Quartus II工程

系统会弹出如图15.11所示的第五个页面。这个页面把之前做的设置的信息做了个归纳。如果想修改,可以点击<Back。没问题的话,可以点击Finish,结束该向导。系统就会弹出新建工程的主界面,如图15.12所示。

图15.12 已经建立了工程LED

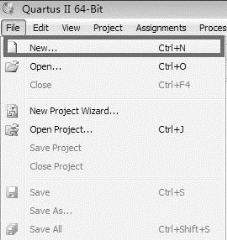

在图15.12,工程导航器左上角立刻显示了已经建立了工程LED,器件类型也按照之前的选择予以确定。如图15.13所示,点击主界面File-New,我们准备建立一个新的LED Verilog HDL源文件。

图15.13 建立新的LED Verilog HDL源文件

如图15.14所示,系统会弹出New对话框,在此需要确定将要建立的文件的类型。用鼠标左键单击Verilog HDL File,点击OK。

图15.14 选择文件的类型

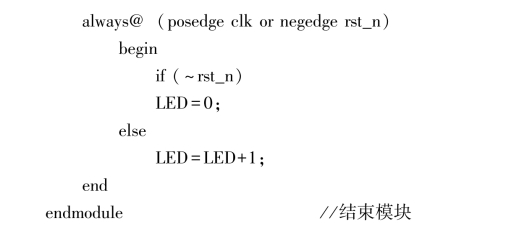

见下图,系统会立刻在主界面的工作区建立一个空白的.v文件等待用户在工作区输入源代码。我们在工作区.v文件输入源代码如下:

源代码输入以后的结果如图15.15所示。

图15.15 源代码输入以后的结果(https://www.xing528.com)

点击左上角保存或全部保存按钮,设置该文件名为LED.v并保存(见图15.15,保存前,系统临时给该文件取名Verilog3.v*)。可以观察一下上面的这一段代码,我们的意图是把LED的驱动信号改为脉冲形式(有别于ISE举的例子,在那个例子里,我们驱动LED的是个恒定高电平)。

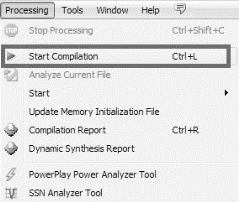

图15.16 编译

如图15.16所示,点击主菜单Processing-Start Compilation,系统会开始进行编译,过一段时间后,会弹出如图15.17所示的弹窗。

弹出的弹窗说的信息是:编译成功。点击OK,关闭弹窗。会看到编译过程留下的编译信息的报告(见图15.17右上角Compilation Report)。编译报告分为两个区域,图15.17左边矩形框区域是内容列表,想看哪一项内容可以点击该内容列表具体项,相关信息会显示在图15.17右边区域(见图15.17中间的矩形框)。

图15.17 编译的信息

编译通过,语法没问题。由此,我们完成了编译的过程。下面进行仿真。我们介绍一下Quartus II的图形仿真过程。

我们想建立图形仿真的界面。点击主界面File-new,会弹出如图15.1的对话框:

图15.18 建立图形仿真

左键单击选中图15.18中的University Program VWF,点击OK,会弹出如下波形编辑页面。系统弹出的是仿真波形编辑器Simulation Waveform Editor。信号列表还是空白,我们下面要做的是把上面源代码的输入输出信号添加到该仿真波形编辑器里去,然后编辑它们(也就是输入激励信号)。

图15.19 仿真波形编辑

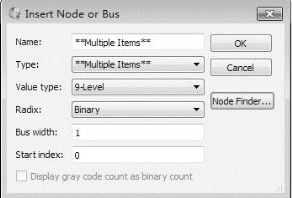

双击图15.19矩形框区域,会弹出如图15.20所示的Insert Node or Bus对话框。

图15.20 仿真波形编辑

单击图15.20的Node Finder按钮,会弹出如图15.21的Node Finder页面。

图15.21 仿真波形编辑

单击上图List按钮会弹出左边的Nodes Found列出的信号,点击上图中间的>>符号,就会在右边矩形框区域看到这些信号被添加进来了,点击OK。会弹出如图15.22所示的页面。

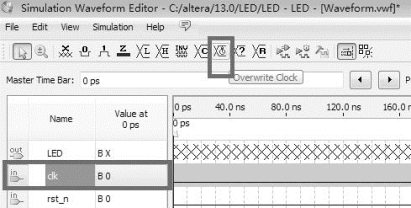

单击图15.22的OK按钮。会弹出图15.23的波形界面,可以看到输入输出信号都被添加到仿真波形编辑器了。接下来就可以设置clk时钟和重置信号rst_n。

图15.22 仿真波形编辑

图15.23 仿真波形编辑

单击图15.23左下角clk信号,选中clk(单击它,它变蓝了就是选中它了),单击上面矩形框区域带时钟的符号,设置clk信号为周期时钟。会弹出如图15.24的时钟设置页面,根据自己需要进行修改,也可以保持默认设置。

图15.24 仿真波形编辑

单击图15.24的OK按钮。这就完成了clk设置为周期时钟。下面设置重置信号rst_n。

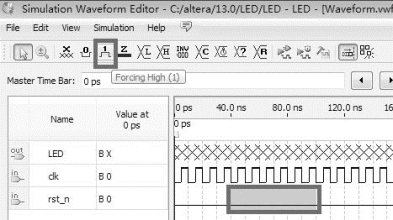

图15.25 仿真波形编辑

图15.25中选中rst_n需要变为高电平的区域(按住鼠标左键向右拖动到一定区域后松手),如图15.25下方的矩形框区域,然后鼠标左键点击图15.25上方矩形框区域带有数字1的符号,设置其为高电平1。类似的我们可以设置rst_n的其他区域为需要的信号(包括x、0、z及其他)。如图15.26所示。

图15.26 仿真波形编辑

设置好之后,单击File-Save as,把刚才设置的波形文件取个名字保存一下,如图15.27所示。

图15.27 保存编辑结果

单击图15.28仿真波形编辑器的菜单Simulation-Run Functional Simulation,系统就会进行功能仿真。

图15.28 运行功能仿真

仿真后的波形如图15.29所示:

图15.29 功能仿真的结果

根据源代码的意思,我们对照仿真波形,可知道功能仿真是正确的。自此,仿真只介绍到这。下面我们看看如何使用Quartus II观察综合的RTL视图。

图15.30 观察RTL视图

如图15.30所示,回到工程主界面,点击主菜单Tools-Netlist Viewers-RTL Viewer,经过短暂运行后,系统会生成如图15.31所示的RTL视图:

图15.31 RTL视图结果

由此,我们完成了使用Quartus II进行编辑、编译、仿真和综合的基本过程。

总体来说,Quartus II和ISE相比,两者能做的事情都差不多,能自己开发的都已经开发了,能调用第三方的都留下了调用接口。但是感觉起来,Quartus II的图形仿真要比ISE图形仿真使用起来麻烦一点。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。