PLD,它的英文全称为Programmable Logic Device,指的是可编程逻辑器件。PLD是一种通用性很强的逻辑电路器件,可以用它来产生任意的逻辑输出。

PLD的集成度非常高,足以满足一般的数字系统的设计需要。与非门和或阵列是PLD最基本的构成。

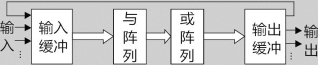

图13.1 PLD器件的基本结构

图13.1是PLD器件的基本结构。它主要由输入缓冲、与(非门)阵列、或阵列和输出缓冲组成。

在一片PLD芯片上,事先规划分配有一定数目的门阵列。设计的过程中需要使用哪些门,就编程把相应的门保留。不需要使用的门则不连通。这样的话,设计人员就可以自行编程,从而把一个数字系统“集成”在一片PLD上。免去了请芯片制造商开发和制作专用的集成电路芯片的繁琐过程。

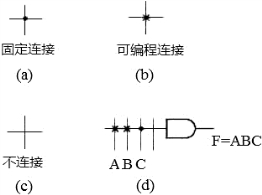

PLD芯片的内部包含的门的数量很大,所以我们在描述PLD的内部连线的情况时,通常会采用一些简化了的描述方法。

从图13.2(a)-(c)可以看出,PLD的门阵列交叉点上的连接方式共分为三种情况:固定连接、可编程连接和不连接。

(1)固定连接:如图13.2(A)所示,两根线的交点用圆点标识,固定连接也叫作硬线连接,是不可以编程改变的。

(2)可编程连接:如图13.2(B)所示,两根线的交点用×标识,开发人员可以通过编程来实现交点的通断。

(3)不连接:如图13.2(C)所示,两线交点处无别的标识,表示两根线处于断开的状态。

(https://www.xing528.com)

(https://www.xing528.com)

图13.2 PLD的连线简化表示方法

图13.2(D)是一个四输入与门。它与我们最开始学数字电路时的画法有点不一样。它是先画一根水平的线,然后画四根竖线表示四个输入端。它的输出为F=ABC。

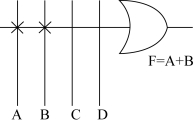

图13.3是一个四输入或门,它的输出为F=A+B。

图13.3 四输入或门的简化画法

历史上来看,PLD可以分为两大类:简单的PLD和复杂的PLD。

简单的PLD分为PROM(可编程只读存储器)、PLA(可编程逻辑阵列)、PAL(可编程阵列逻辑)和GAL(通用阵列逻辑)。它们基本出现在20世纪70年代和80年代。

复杂的PLD分为CPLD(复杂可编程逻辑器件)和FPGA(现场可编程门阵列)。CPLD和FPGA技术一直沿用到今天并不断向前发展。

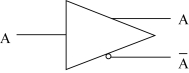

如图13.4所示,是一个简单的PLD的图形表示。它是一个缓冲器。输出端包含了信号A的取反输出。在A上面用一横杠表示。

图13.4 缓冲器的图形表示

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。