我们使用Verilog进行设计的所有模型,其最终目的都是为了对芯片进行编程从而形成真实的电路。对于真实的电流流动,信号都是有延迟的。那么,我们在Verilog设计时,就要体现出这种延迟。同样一段代码,用这种厂家的器件来植入,会有这样的延迟;用那种厂家的器件来植入,可能就会有不一样的延迟。我们在这一章的前几节里,就用到了延迟。下面来具体地介绍一下延迟。先看一句代码:

![]()

这句代码中,#3就表示3个时间单位的延迟。

那么什么是3个时间单位的延迟呢?我们可以使用`timescale指令来定义这个时间单位。比如:

![]()

这句话指的是:我们定义了一个时间的尺度,时间单位是1ns,时间精度是10ps。前一个例子里的#3的3个时间单位的延迟,在这里就表示延迟为3ns。有时候延迟的不一定是整数个时间单位,可能带有小数,比如#3.02,那就表示延迟是3ns+20ps,延迟的最小分辨率为10ps。

通过`timescale语句的定义,我们就从数学上把时间单位与物理世界的时间相联系起来了。通常,`timescale语句被定义在每一个模块的第一行。

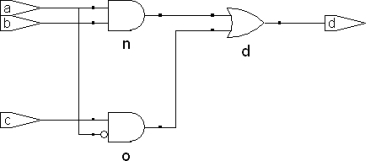

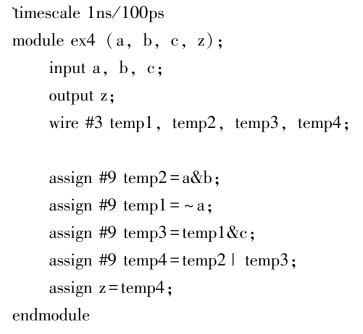

例5.15 在ISE环境下对以下例子进行建模综合和仿真,尝试分析过程中遇到的现象。

图5.11 建模实例图

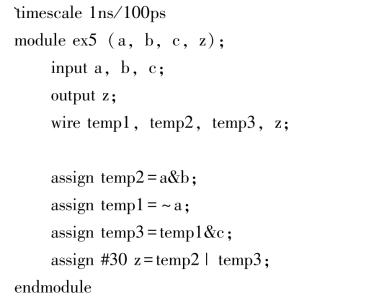

例5.16在ISE环境下对以下例子进行建模综合和仿真,尝试分析过程中遇到的现象。(https://www.xing528.com)

例5.17在ISE环境下对以下例子进行建模综合和仿真,尝试分析过程中遇到的现象。

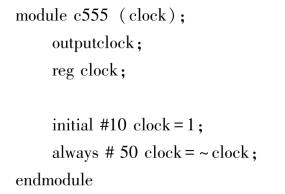

例5.18 产生一个时钟源。

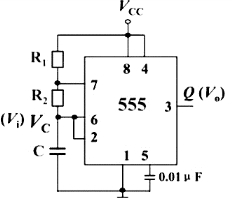

在本科初级阶段的教学中,读者做电子电路实验,设计一个电路如果需要用到时钟源的话,最常用的是采用555定时器来产生需要的脉冲波形,如图5.12所示,通过控制电路参数,就可以控制输出的矩形脉冲波形。

图5.12 555定时器

我们在前面说过,如上所示的技术已经逐步逐步淘汰。目前的趋势是把所有的模块功能都集成到一个芯片来实现,而不是使用单独的时钟源。最多是芯片外加个晶振形成时钟。下面我们来设计一个FPGA时钟源。

上面这个例子,我们建立了一个c555时钟模块,这模块没有输入,只有输出。语句initial#10clock=1表示最开始的10个时间单位,clock的信号是未知的。到了第10个时间单位,给clock赋值为1。然后从这时刻往后再数50个时间单位,clock的值翻了一下,赋值给自己;之后每过50个时间单位,clock的值都取反再赋值给自己。所以clock的周期就是100个时间单位。至于1个时间单位是多少,我们在之前的好几个例子都遇到过,就是在程序的开头用`timescale语句来定义。在这个程序里未给出。后面的章节里会详细地介绍到。

大家在ISE环境下对这个例子进行综合和仿真,尝试分析过程中遇到的现象。提示:尤其注意其综合的结果,看是否能正确综合。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。