【摘要】:例5.8:对四选一多路选择器进行门级建模。例5.9:对2-4译码器进行门级建模。图5.7门级建模示例看上图,比如,输入的数据是8个1,那么经过u0~u6共7个异或门后,输出的偶校验位out_even就为0。例5.11:半加器的门级描述。图5.8门级建模示例例5.12:实例调用上面这个门级的半加器来实现一个全加器。图5.10门级建模示例例5.14:下面这个例子是两个数alpha和beta之间做比较,alpha和beta都各有两位。

5.1节,我们介绍到门级建模时,只是举了那么几个简单的例子,知道了大概那么回事,这一节我们将详细的介绍门级建模。

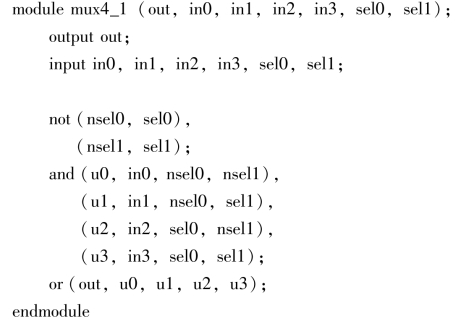

例5.8:对四选一多路选择器进行门级建模。

下图是综合以后的电路。

图5.5 门级建模示例

反过来,给你门级的电路图,你得会编写源代码对其进行门级建模。

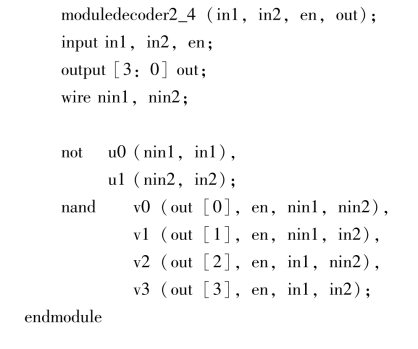

例5.9:对2-4译码器进行门级建模。

下图是综合后的结果。

图5.6 门级建模示例

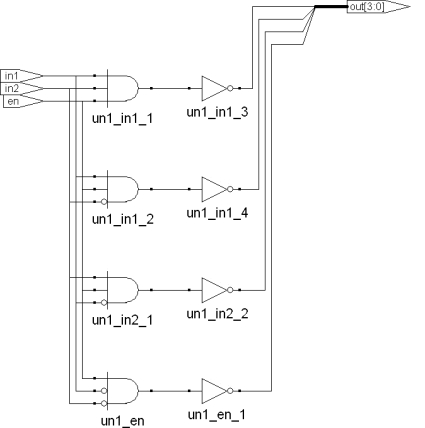

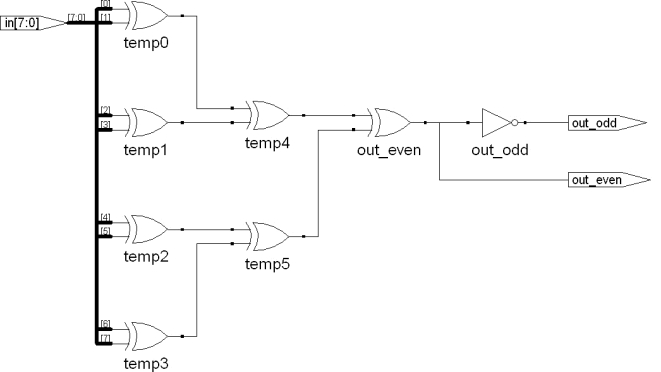

例5.10:对八位的奇偶校验发生器进行门级建模。

有些时候在传送数据的过程中,会出错。接收端为了判别接收到的数据有没有错,会要求发送端在被传送的数据之后,多添加一个比特位的数据。根据奇校验还是偶校验来决定这一位是0还是1。

下图是综合以后的结果。

图5.7 门级建模示例

看上图,比如,输入的数据是8个1,那么经过u0~u6共7个异或门后,输出的偶校验位out_even就为0。(https://www.xing528.com)

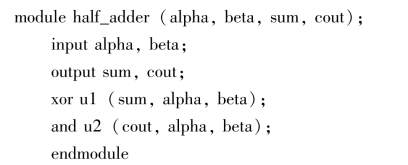

例5.11:半加器的门级描述。

生成的门级电路如下。

图5.8 门级建模示例

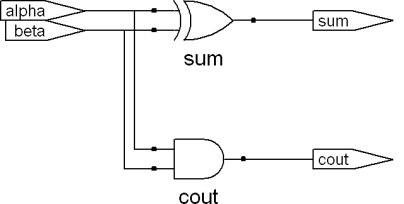

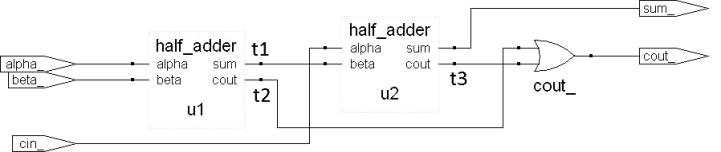

例5.12:实例调用上面这个门级的半加器来实现一个全加器。

![]()

它的实例调用可以参考下面这个图。

图5.9 门级建模示例

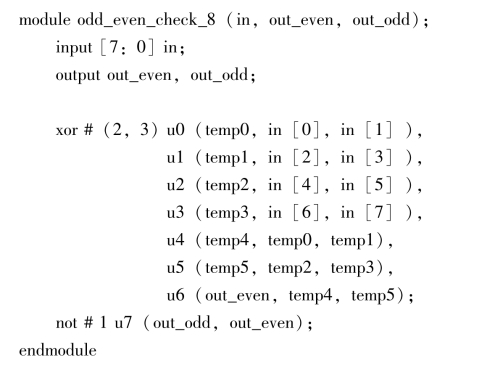

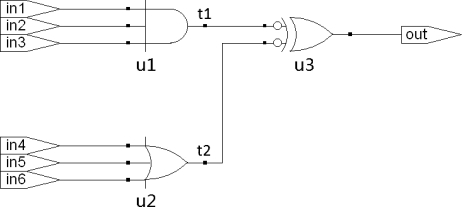

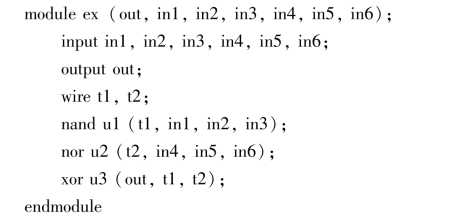

例5.13:完成对下面这个门电路的实例调用描述。

图5.10 门级建模示例

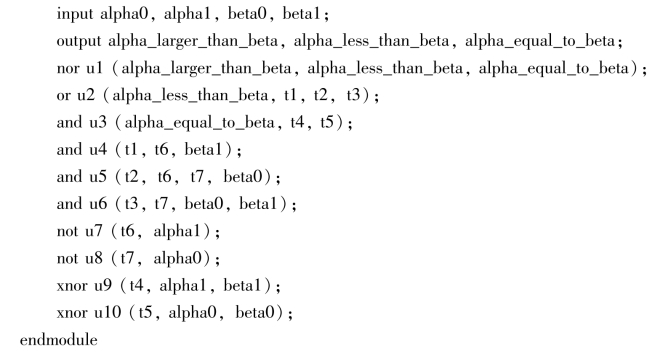

例5.14:下面这个例子是两个数alpha和beta之间做比较,alpha和beta都各有两位。module compare_2bit(alpha_larger_than_beta,alpha_less_than_beta,alpha_equal_to_beta,alpha0,alpha1,beta0,beta1);

请读者试着画出上面这段程序的原理图。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。