数据流的行为模型的建立,可以使用连续性赋值语句。连续性赋值语句指的就是assign这样的赋值语句。

连续赋值语句可以对wire类型的信号进行赋值,不能对寄存器进行赋值。比如下面这个语句:

上面这个语句,只要右边表达式(b和c)有变化,就立刻计算右边表达式的值,然后赋值给左边a。那么什么叫作只要右边表达式有变化呢?这就意味着这种连续赋值语句一定是对应的组合逻辑电路,因为它不需要时钟触发。组合逻辑的意思就是,电路连好了,电路时刻运行,只要输入的信号来了,就立刻计算输出值。它是不需要在时钟的控制下工作的。

连续赋值语句的赋值对象不能是寄存器,一般可以是标量的线网信号(也就是一根线)、向量的线网信号(多根线)、向量的线网信号的其中一位或几位、矩阵的某个元素,或者以上涉及的信号的组合。

比如有个加法器,输入in1、in2和输入的进位位cin,输出out和输出的进位位cout,那么我们可以在连续赋值语句中使用拼接运算符,如下:assign{cout,out}=in1+in2+cin;

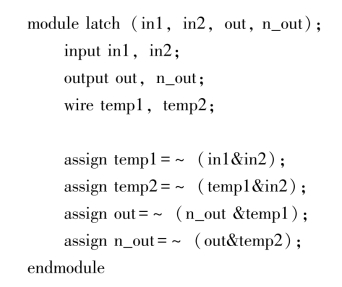

看一个数据流建模的例子。

例5.5:

下面这个例子:

![]()

该连续赋值语句没有指定延迟,对于所有的这种情况,当执行到这条语句时,立即计算右边的表达式,立即把右边的结果赋值给左边。无延迟,也就是延迟为0。

下面这个例子:

![]() (https://www.xing528.com)

(https://www.xing528.com)

该连续赋值语句指定了延迟为3个时间单位,指的是当右边表达式的b或c发生了变化,从发生变化这一刻开始(假设为t时刻),立刻计算右边表达式的值,在t+3时刻把右边表达式的值赋值给左边。

读者也许会问,如果在t+2时刻,b或c发生了变化,那么是把t时刻计算的值赋值给左边,还是把t+2时刻的值赋值给左边?

这就涉及一个叫作惯性延迟的概念。惯性延迟指的是,右边的表达式计算好了后,在把右边的计算结果赋值给左边之前的这一段时间(比如这个例子的t到t+3时刻),右边的表达式其参量应该要保持不变。如果在这段时间,右边的表达式的参量发生了变化,则刚才的计算无效。

例5.6:将下面这个电路进行Verilog连续赋值描述。

图5.4 数据流建模示例

我们先来看如下一个语句:

![]()

这个语句说的是:alpha等于beta吗?等的话,把in1赋值给out;不等的话,把in2赋值给out。

例5.7:四选一多路选择器。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。