【摘要】:通常,我们可以从好几个不同的角度对一个模型进行HDL描述。如图5.1所示,分为5个级别。图5.1HDL的5个层级描述系统级:主要使用HDL语言描述电路系统的外部性能,不涉及系统的内部细节。它是从RTL级别进行的综合,就依然是RTL综合的结果。如果从源代码的赋值的方式上区分,HDL的建模有3个大类的区别:行为级建模、数据流级建模和门级建模。

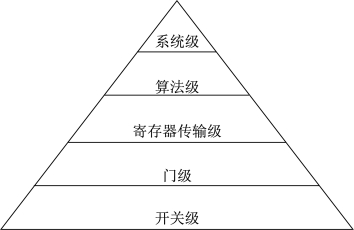

通常,我们可以从好几个不同的角度对一个模型进行HDL描述。如图5.1所示,分为5个级别。依次分为系统级、算法级、寄存器传输级、门级、开关级。

图5.1 HDL的5个层级描述

系统级:主要使用HDL语言描述电路系统的外部性能,不涉及系统的内部细节。

算法级:主要使用HDL语言对待设计的电路模型的运行算法进行描述。

先看一个算法级描述的例子。

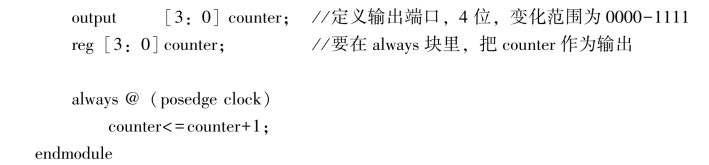

例5.1:四位计数器。

假设我们要设计一个四位的计数器,每来一个时钟,就记一个数,4位意味着总共可以计2的4次方共16个数,输出端口为4位:

在这个例子里,clock上升沿触发计数器,每来一个上升沿,计数器加1给输出。

寄存器传输级(register transfer level):也叫作RTL级,顾名思义,这个级别主要从信号如何在寄存器之间来回传输的这个角度进行描述。

来看一个寄存器传输级的例子。(https://www.xing528.com)

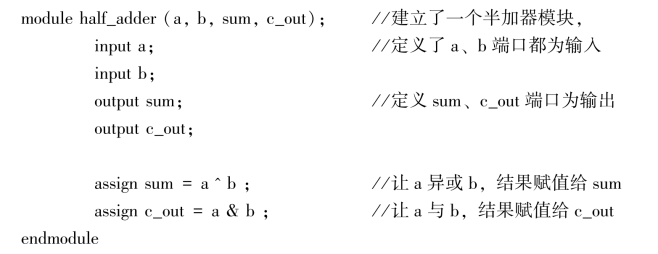

例5.2:半加器

如下图所示,它实际上有4个端口。两个输入a、b。两个输出,一个是加法的低位sum,另一个是进位位c_out。

图5.2 寄存器传输级的例子

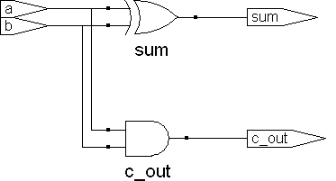

下图是它RTL综合后实现的电路结构:

图5.3 寄存器传输级示例的综合结果

有些源代码综合以后,本身就没有寄存器,那你也不能强迫它出现寄存器。它是从RTL级别进行的综合,就依然是RTL综合的结果。

门级:主要使用HDL语言描述门与门之间的逻辑连接。

开关级:主要使用HDL语言描述三极管和节点之间的连接关系。

如果从源代码的赋值的方式上区分,HDL的建模有3个大类的区别:行为级建模、数据流级建模和门级建模。下面我们依次进行介绍。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。