上面,我们开发了LED电路的源代码,仿真结果显示LED管脚确实能产生我们要求的信号。如果我们把以上这段程序编译以后,下载到FPGA芯片,在FPGA芯片里配置出相应的电路,只要我们把LED输出信号指定到FPGA芯片的某个管脚,然后在焊接电路板时把这个管脚连接到之前的LED接地电路,那么,我们就可以实现这个项目了。

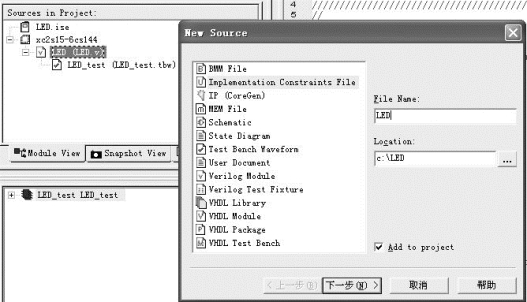

下面,我们要做的事就是在FPGA芯片里指定这个LED管脚。这就是管脚约束。鼠标右键点击ISE主界面左上角的LED.v文件,在弹出的对话框里选择New Source。如下图2.40所示,在New Source对话框里左边一列选择植入限制文件Implementation Constraints File,文件名可以输入LED,位置可以保留默认。

图2.40 新建管脚约束文件

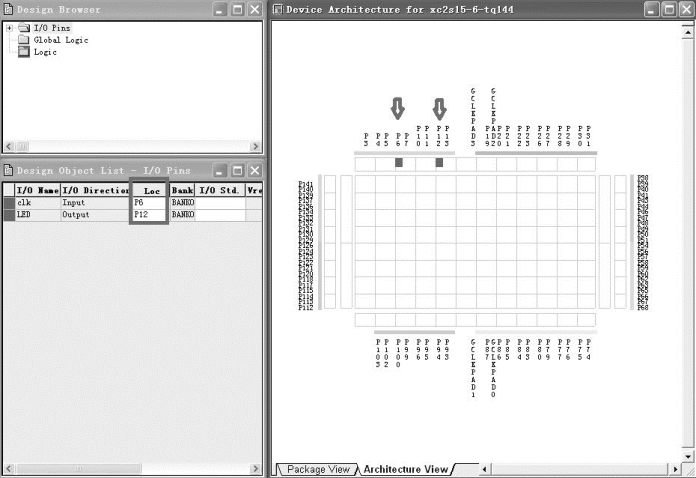

点击“下一步->完成”。主界面左上角会变成如图2.41所示。新生成了一个LED.ucf文件。注意此时的文件结构。因为管脚约束文件LED.ucf是用来对LED.v文件对应的电路进行约束的,所以LED.ucf被建立在LED.v的结构之下。

如图2.41所示,点击进程视图页签,可以看到在用户约束user Constraints这一区域,主要可以做4件事:创造定时约束、指定封装管脚Assign Package Pins、创造面积约束和文本形式进行约束编辑。我们下面来重点讲解指定封装管脚。

图2.41 指定封装管脚

不同的封装会有不同的界面。为了便于叙述,这里我们做一下调整,把封装改为tq144。双击图2.41Assign Package Pins。系统会弹出一个设计浏览器如图2.42。图2.42左下角就是各个输入输出管脚的列表和设置区,右边就是器件管脚的布置结构。(https://www.xing528.com)

先看图2.42左下角区域。这个电路所有的输入和输出端口都列在I/OName。I/O Direction是它们的输入或者输出的属性。Loc就是我们要标注的物理映射,也就是说,Loc就是用来指定哪个端口对应到FPGA芯片的哪个管脚上。它的格式如下:Pxxx(P代表pin,xxx是对应的管脚数)。看右边的箭头部分。例如在这个项目里,我们指定clk为P6管脚,LED为P12管脚。下图的右边区域就是该FPGA芯片的管脚布置图。操作时可以放大或缩小进行观察。

图2.42 指定封装管脚

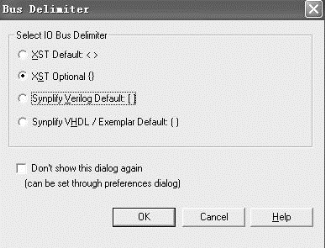

单击保存,系统会弹出下面的对话框:

图2.43 设置XST Optional

图2.43,选择XST Optional选项,点击OK。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。