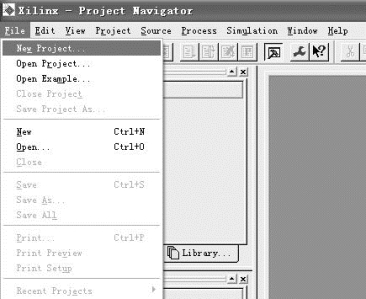

打开已经安装好的虚拟机,启动ISE。点击主菜单栏File->New Project。如图2.13所示。

图2.13 新建工程

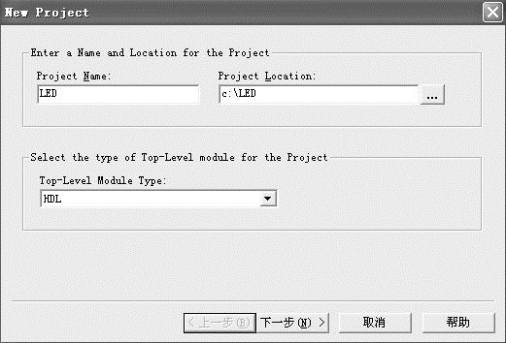

会弹出如图2.14所示对话框,在项目名Project Name一栏输入项目的名字,随便起一个,比如LED,默认的路径Project Location为C:\\LED,也可以自己设置项目的保存位置,顶层模块类型Top-Level Module Type设置为默认的HDL,如图2.14所示:

图2.14 新建工程

通常来说,我们在开发FPGA的电路时,通常会把一个电路写为一个模块。FPGA的开发会有不同的层级,一般采用由顶向下的开发方法。最上面的一级就叫顶层。

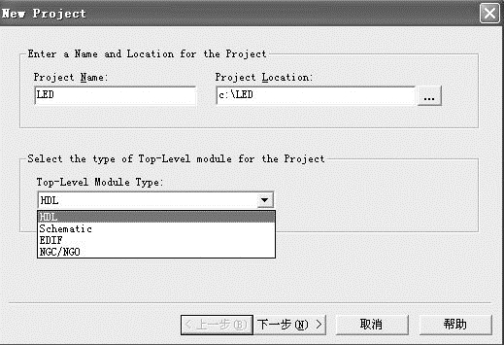

看图2.15。

顶层的模块类型可以有很多形式,比如可以用硬件描述语言HDL来编写。

图2.15 新建工程

也可以像早期开发模拟电路那样用原理图输入的方法。Schematic原理图输入指的就是自己往程序主界面拖动电阻、电容、放大器等原件,用线连接起来形成原理图。电路复杂的时候这种方法就不适合了。

EDIF指的是顶层源代码是由Synplify综合之后的网表文件,其文件后缀名为.edf.

NGC/NGO表示顶层源代码是由ISE自带的综合工具XST生成的网表文件。

点击“下一步”。

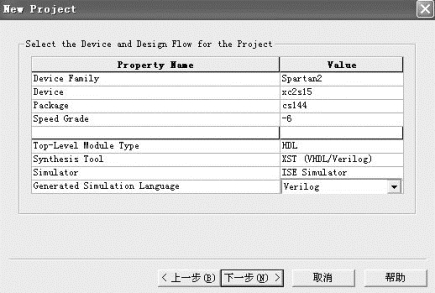

图2.16 新建工程

图2.16这个弹出的对话框就是对所要使用的FPGA芯片的器件型号进行配置。根据最后做电路硬件时要使用的芯片来选择器件家族,这里先暂时选Spartan2,器件选xc2s15,封装选cs144,速率等级选-6。顶层模块类型选HDL,综合工具选ISE自带的XST,仿真器选ISE自带的仿真器,生成的仿真语言选Verilog。我们在本书中编写的源代码全部使用Verilog HDL。

点击“下一步”。

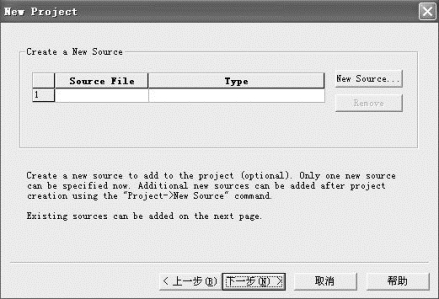

图2.17 新建工程

图2.17这一步是要创建一个项目里的新的源文件。如果不想在这里创建,可以直接点击“下一步”。

(https://www.xing528.com)

(https://www.xing528.com)

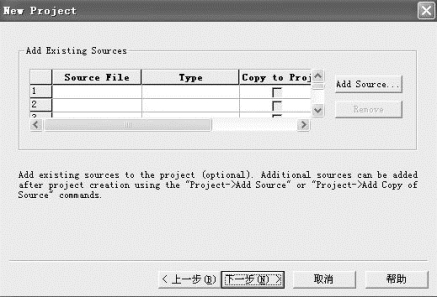

图2.18 新建工程

如果之前有项目相关的文件,图2.18这一步会提示添加到项目中来。这里不添加,点击“下一步”。

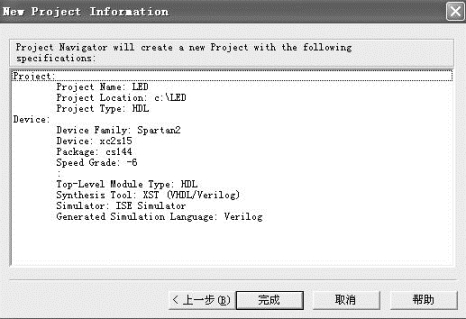

图2.19 新建工程

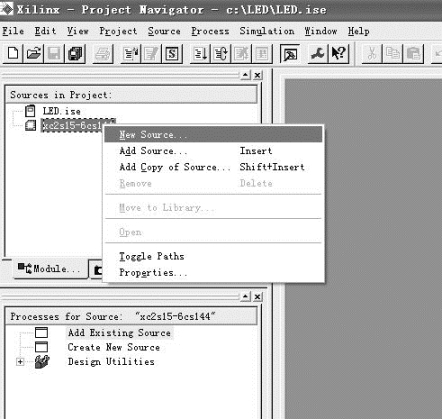

图2.19这一步弹出了项目相关的信息。确认无误后,点击“完成”。如图2.20所示,系统弹出了项目的主界面。在主界面右键点击器件型号,选择“New Source...”。

图2.20 启动新建工程

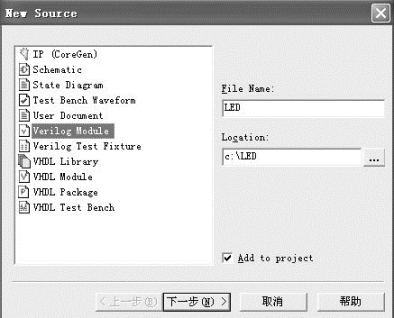

在图2.21弹出的“New Source”对话框中,左边选择Verilog Module,右边文件名填入“LED”,路径可以选择默认路径,点击“下一步”。

图2.21 添加新的源文件

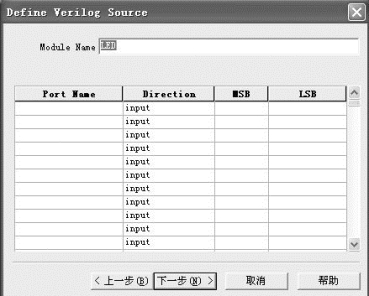

如下图2.22所示,弹出“Define Verilog Source”对话框。不做修改,点击“下一步”。

图2.22 定义源文件

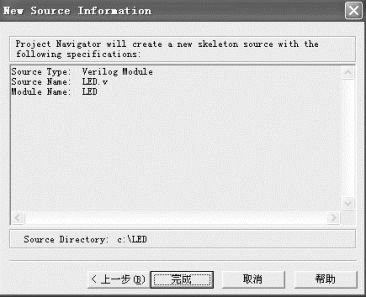

会弹出如下图2.23所示“New Source In formation”对话框,点击完成。

图2.23 新的源文件的信息

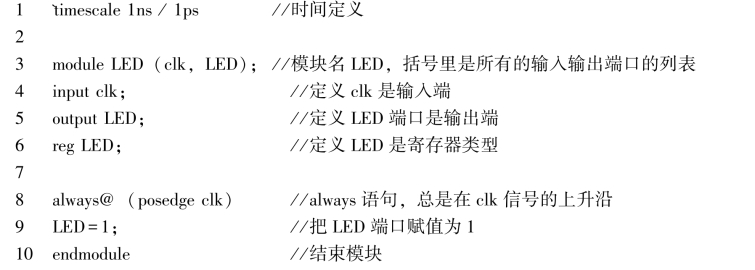

双击打开主界面的“LED.v”文件,手动输入源代码:

其中,第1行是对项目的时间单位和精度进行定义。第3行和第10行是一对,写了module,就要立刻中间回车空几行,写下结束模块endmodule。第3行LED是模块名,括号里是这个模块的所有的输入端口和输出端口的列表,各个端口之间用英文逗号隔开。第3行用英文分号结尾。第4行定义clk是输入时钟。第5行定义LED是输出端口。我们后面要使用always块语句,由于Verilog HDL这种语言的语法规则,在always块语句里被赋值的信号要先定义为寄存器类型。于是,我们在第6行把LED定义为寄存器类型reg。第8-9行的意思是总是在clk信号的上升沿的时候,把LED端口赋值为1。第10行结束模块。

每一行之前的数字编号是为了方便叙述,加上去的。大家在输入源代码的时候,不需要把每一行的编号输入进去。每一行之后的双反斜杠是注释,Verilog HDL的注释不会被编译。

上面这段程序我们使用的是Verilog HDL语言。后面我们会专门针对其细节进行有针对性的讲解。无论是编写什么语言的程序,大家要养成良好的编程习惯,该上下对齐的地方要对齐,该有注释的地方要有注释。

刚开始学习编写Verilog HDL源代码的时候,容易犯一些基本的语法错误。比如把英文的标点写成中文的标点,英文的括号写成中文的括号,等等。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。