DS12C887是美国DALLAS公司推出的并行接口实时时钟/日历芯片,采用CMOS技术制成,具有内部晶振和时钟芯片备份锂电池,同时它与计算机常用的时钟芯片MC146818和DS12887引脚兼容,可直接替换。采用DS12C887芯片设计的时钟电路无需任何外围电路和器件,并且有良好的微机接口。DS12C887芯片有微功耗,外围接口简单,精度高,工作稳定可靠等优点,广泛用于各种需要较高精度的实时时钟系统中。

DS12C887主要功能如下:

1)内含一个锂电池,断电后运行十年以上不丢失数据;

2)可计算到2100年前的秒、分、时、天、星期、日、月、年,并有闰年补偿功能;

3)二进制数码或BCD码表示时间、日历和定时闹钟;

4)12h或24h制,12h时钟模式带有PM和AM指示,有夏令时功能;

5)Motorola和Intel总线时序选择;(https://www.xing528.com)

6)有128B RAM单元与软件接口,其中15B作为时钟和控制寄存器,113B为通用RAM,所有RAM单元数据都具有掉电保护功能;

7)可编程方波信号输出;

8)中断信号输出(IRQ)和总线兼容、定时闹钟中断、周期性中断、时钟更新周期、结束中断可分别由软件屏蔽,也可分别进行测试。

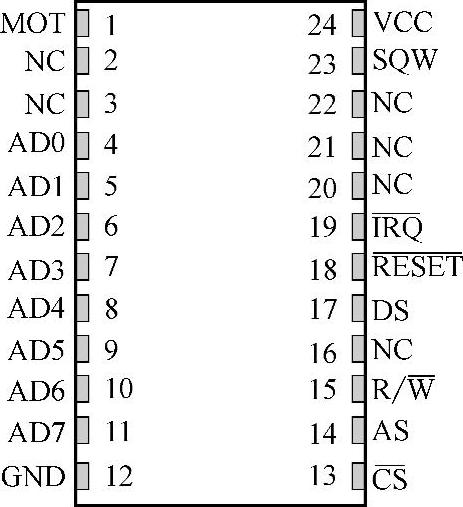

DS12C887的引脚如图10-1所示,其中VCC接+5V输入,GND接地,当VCC的输入小于+4.25V时,禁止用户对内部RAM进行读、写操作;当VCC的输入小于+3V时,DS12C887会自动将电源转换到内部自带的锂电池上,以保证内部电路能够正常工作。DS12C887通过MOT进行模式选择,当MOT接VCC时,选用的工作模式是Motorola模式,当MOT接GND或不接时,用的是Intel模式。当供电电压VCC大于4.25V时,SQW引脚可进行方波输出,此时用户可以通过对控制寄存器编程来得到13种方波信号的输出。AD0~AD7是双向复用地址/数据总线,在总线周期的前半部分,出现在AD0~AD7上的是地址信息,可用以选通DS12C887内的RAM,总线周期的后半部分出现在AD0~AD7上的是数据信息。AS为地址选通输入引脚,在进行读写操作时,AS的上升沿将AD0~AD7上出现的地址信息锁存到DS12C887中,而下一个下降沿清除AD0~AD7上的地址信息,不论是否有效,DS12C887都将执行该操作。DS是数据选通/读取输入引脚,该引脚有两种工作模式,当MOT接VCC时,选用Motorola工作模式,在这种工作模式中,每个总线周期后一部分的DS为高电平,被称为数据选通。在读操作中,DS的上升沿使DS12C887将内部数据送往总线AD0~AD7,以供外部读取。在写操作中,DS的下降沿将使总线AD0~AD7上的数据锁存在DS12C887中;当MOT接GND或不接时,选用Intel模式,在该模式中,该引脚是读允许输入引脚,即Read Enable。R/W是读/写输入引脚,该引脚也有两种工作模式,当MOT接VCC时,R/W工作在Motorola模式。此时,该引脚的作用是区分进行的是读操作还是写操作,当R/W为高电平时为读操作,R/W为低电平时为写操作;当MOT接GND或不接时,该脚工作在Intel模式,此时该引脚作为写允许输入,即Write Enable。CS是片选输入引脚,低电平有效。IRQ是中断请求输出引脚,低电平有效,该引脚有效对DS12C887内的时钟、日历和RAM中的内容没有任何影响,仅对内部的控制寄存器有影响。RESET是复位输入引脚,在典型应用中,RESET可以直接接VCC,这样可以保证DS12C887在掉电时,其内部控制寄存器不受影响。

图10-1 DS12C887引脚图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。