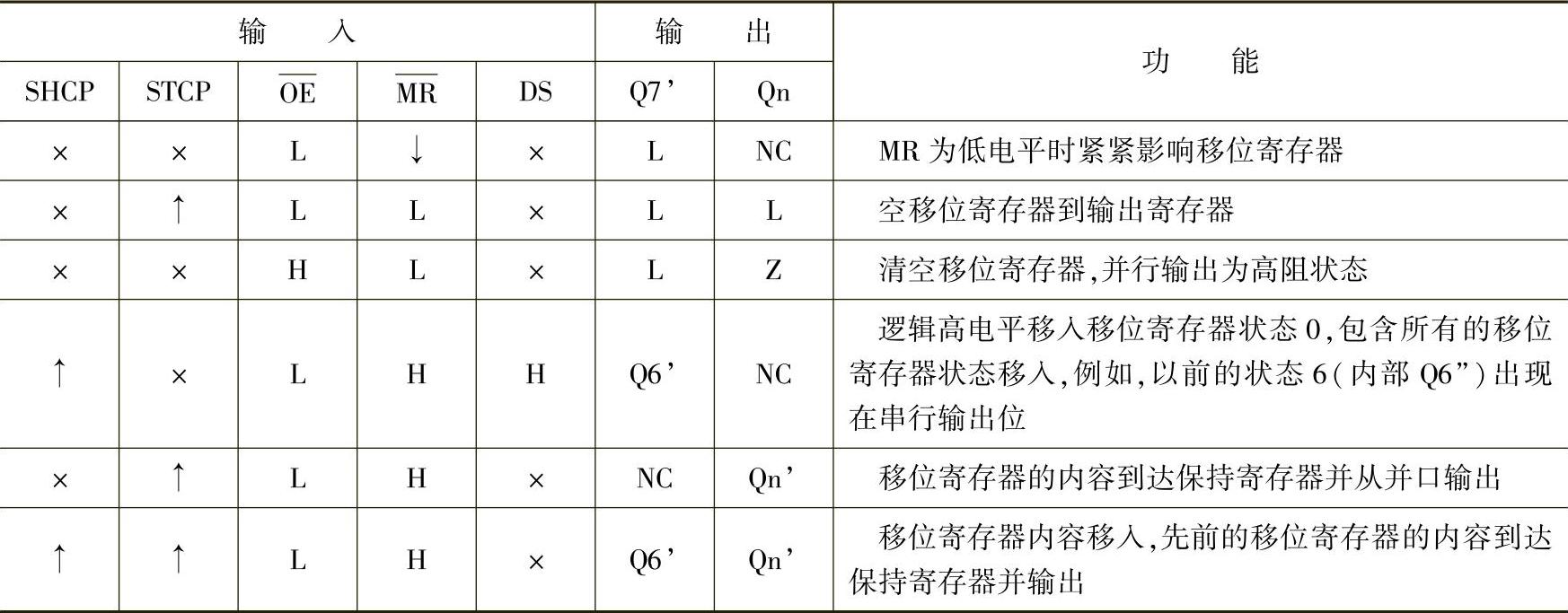

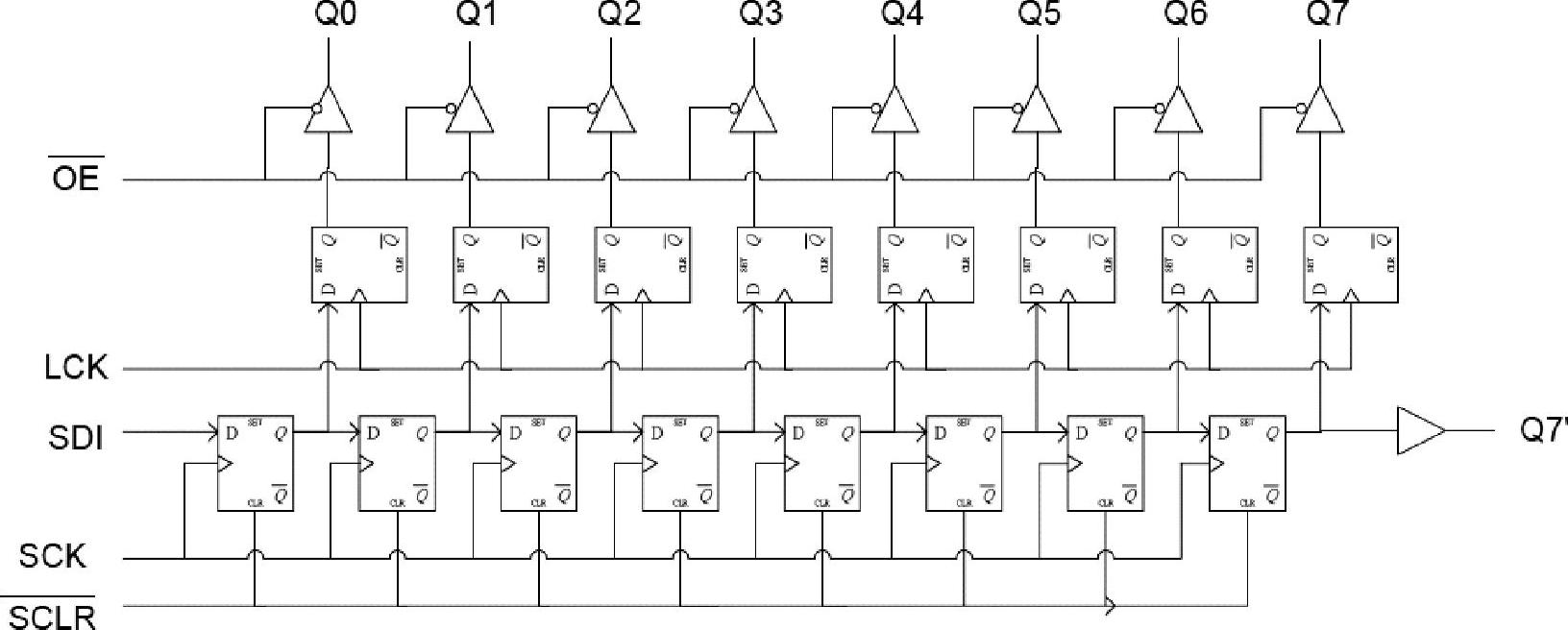

【摘要】:本实例主要应用到了74HC595移位寄存器,其实物如图6-1所示。图6-1 74HC595的实物图74HC595引脚说明见表6-1。74HC595是一个8位串行输入、并行输出的移位寄存器:并行输出为三态输出。表6-2 74HC595功能表注:H=高电平状态;L=低电平状态;↑=上升沿;↓=下降沿;Z=高阻;NC=无变化;×=无效。74HC595移位寄存器是由D触发器构成的,其具体的实现过程在数字电路中已经详细讲解,这里我们只给出其内部的功能框图,如图6-2所示。

本实例主要应用到了74HC595移位寄存器,其实物如图6-1所示。

74HC595的特点如下:

1)8位串行输入;

2)8位串行或并行输出;

3)存储状态寄存器,3种状态;

4)输出寄存器可以直接清除;

5)移位频率为100MHz;

6)工作电压为2~6V;

7)很短的传递延迟时间,可支持高速串行连接;

8)强化的平行输出端的灌电流;

9)增强的静电防护(ESD)能力。

(https://www.xing528.com)

(https://www.xing528.com)

图6-1 74HC595的实物图

74HC595引脚说明见表6-1。74HC595是一个8位串行输入、并行输出的移位寄存器:并行输出为三态输出。在SCK的上升沿,串行数据由SDI输入到内部的8位移位缓存器,并由Q7’输出。

表6-1 74HC595引脚说明

而并行输出,则是在LCK的上升沿,将在8位位移缓存器的数据存入8位并行输出缓存器;当 的控制信号为低电平时,并行输出端的输出值等于并行输出缓存器所存储的值;当

的控制信号为低电平时,并行输出端的输出值等于并行输出缓存器所存储的值;当 的控制信号为高电位时,也就是输出关闭时,并行输出端会维持在高阻抗状态。当

的控制信号为高电位时,也就是输出关闭时,并行输出端会维持在高阻抗状态。当 为高电平,

为高电平, 为低电平时,数据在SHCP上升沿进入移位寄存器,在STCP上升沿输出到并行端口,见表6-2。

为低电平时,数据在SHCP上升沿进入移位寄存器,在STCP上升沿输出到并行端口,见表6-2。

表6-2 74HC595功能表

注:H=高电平状态;L=低电平状态;↑=上升沿;↓=下降沿;Z=高阻;NC=无变化;×=无效。

74HC595移位寄存器是由D触发器构成的,其具体的实现过程在数字电路中已经详细讲解,这里我们只给出其内部的功能框图,如图6-2所示。74HC595的时序图如图6-3所示。

图6-2 功能框图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。