中断是指当CPU正在执行程序A时,如果有外部事件B请求CPU处理,则CPU暂时中断当前正在执行的程序A,转去执行程序B,并在处理完程序B之后,立即返回到原来被中止的程序A的间断处继续执行;为实现中断功能而设定的各种硬件和软件统称为中断系统。

MCS-51系列单片机有5个中断源:外部中断INT0、INT1,定时器/计数器0、1溢出中断和串口中断。

1.中断源

中断源是指引发中断的原因,MCS-51单片机中断系统中断源如下:

1)INT0:外部中断0请求,低电平有效。通过MCS-51单片机P3.2引脚输入。

2)INT1:外部中断1请求,低电平有效。通过MCS-51单片机P3.3引脚输入。

3)T0:定时器/计数器0溢出中断请求。

4)T1:定时器/计数器1溢出中断请求。

5)TX/RX:串行中断请求。当串口完成一帧数据发送或接收时,请求中断。

2.中断控制方式

MCS-51系列单片机对中断系统的控制主要包括4个特殊功能寄存器:定时器控制寄存器TCON、串口控制寄存器SCON、中断允许寄存器IE和中断优先级寄存器IP。

(1)TCON

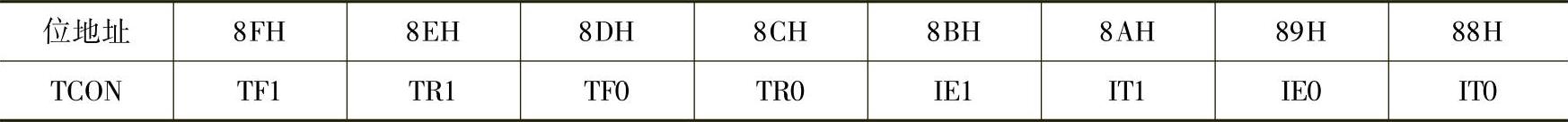

TCON为定时器/计数器T0和T1的控制寄存器,同时也锁存T0和T1的溢出中断标志及外部中断0和1的中断标志等。与中断有关的位见表3-1。

表3-1 TCON寄存器位定义

TF1:定时器/计数器T1的溢出中断请求标志位。允许T1计数后,T1从初值开始进行加1计数,计数器最高位产生溢出时,由硬件将TF1置“1”,并向CPU发出中断请求。当CPU响应中断时,硬件自动将TF1清0。

TF0:定时器/计数器T0的溢出中断请求标志位,其含义与TF1相似。

IE1:外部中断1的中断请求标志位。当检测到外部中断引脚1上存在有效的中断请求信号时,由硬件将IE1置“1”。当CPU响应该中断请求时,由硬件将IE1清“0”。

IE0:外部中断1的中断请求标志位。其含义与IE1相似。

IT1:外部中断1的中断触发方式控制位。IT1为0时,外部中断1为电平触发方式,若外部中断1请求为低电平,则使IE1置1。IT1为1时,外部中断1为边沿触发方式,若CPU检测到外部中断1的引脚有由高到低的负跳变沿时,则使IE1置1。

IT0:外部中断1的中断触发方式控制位。其含义与IT1相似。

TR1:为1时启动定时器/计数器T1;为0时停止定时器/计数器T1。

TR0:为1时启动定时器/计数器T0;为0时停止定时器/计数器T0。

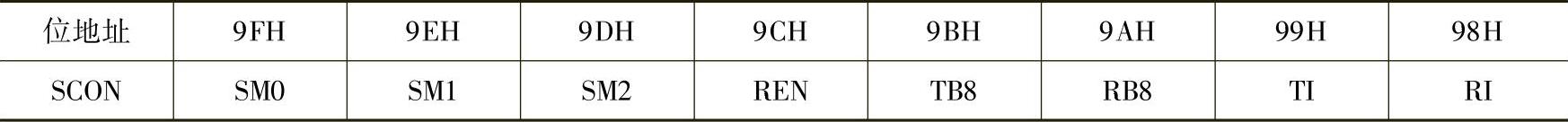

(2)SCON

SCON为串口控制寄存器,其低2位TI和RI锁存串口的接收中断和发送中断。SCON中TI和RI的格式及含义见表3-2。

表3-2 SCON寄存器位定义

TI:串口发送中断请求标志位。CPU将一个数据写入发送缓冲器SBUF时,就启动发送,每发送完一帧串行数据后,硬件置位TI。但CPU响应中断时,并不清除TI,必须在中断服务程序中由软件对TI清0。

RI:串口接收中断请求标志。在串口允许接收时,每接收完一个串行帧,硬件置位RI。同样,CPU响应中断时不会清除RI,必须用软件清0。(https://www.xing528.com)

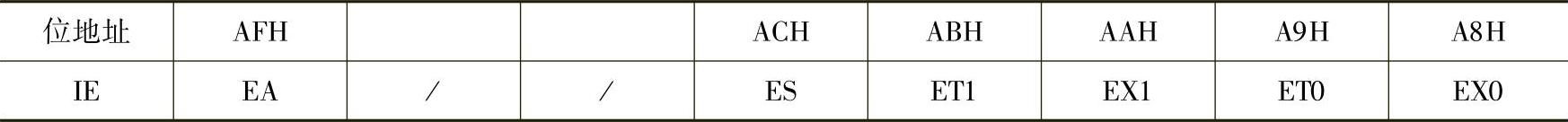

(3)IE

MCS-51对中断请求源的开放或屏蔽是由中断允许寄存器IE控制的,IE的格式见表3-3。

表3-3 IE寄存器位定义

中断允许寄存器IE对中断的开放和关闭实现两级控制。所谓两级控制就是有一个总的开关中断控制位EA(IE.7),当EA=0时,关闭所有的中断申请,即任何中断申请都不接受;当EA=1时,CPU开放中断,但5个中断源还要由IE的低5位的各对应控制位的状态进行中断允许控制。IE中各位的含义如下:

EA:中断允许控制位。EA=0,屏蔽所有中断请求;EA=1,CPU开放中断。对各中断源的请求中断是否允许,还要取决于各中断源的中断允许控制位的状态。

ES:串口中断允许位。ES=0,禁止串口中断;ES=1,允许串口中断。

ET1:定时器/计数器T1的溢出中断允许位。ET1=0,禁止T1中断;ET1=1,允许T1中断。

EX1:外部中断1中断允许位。EX1=0,禁止外部中断1中断;EX1=1,允许外部中断1中断。

ET0:定时器/计数器T0的溢出中断允许位。ET1=0,禁止T0中断;ET1=1,允许T0中断。

EX0:外部中断0中断允许位。EX0=0,禁止外部中断0中断;EX0=1,允许外部中断0中断。

(4)IP

MCS-51有两个中断优先级。对于每一个中断源可编程为高优先级中断或者低优先级中断。MCS-51片内中断优先级控制寄存器IP格式见表3-4。

表3-4 IP寄存器位定义

IP中的低5位为各中断源优先级的控制位,可用软件来设定,各位的含义如下:

PS:串口中断优先级控制位。

PT1:定时器/计数器T1中断优先级控制位。

PX1:外部中断1中断优先级控制位。

PT0:定时器/计数器T0中断优先级控制位。

PX0:外部中断0中断优先级控制位。

若某一控制位为1,则相应的中断源就规定为高级中断;反之,若某一控制位为0,则相应的中断源就规定为低级中断。

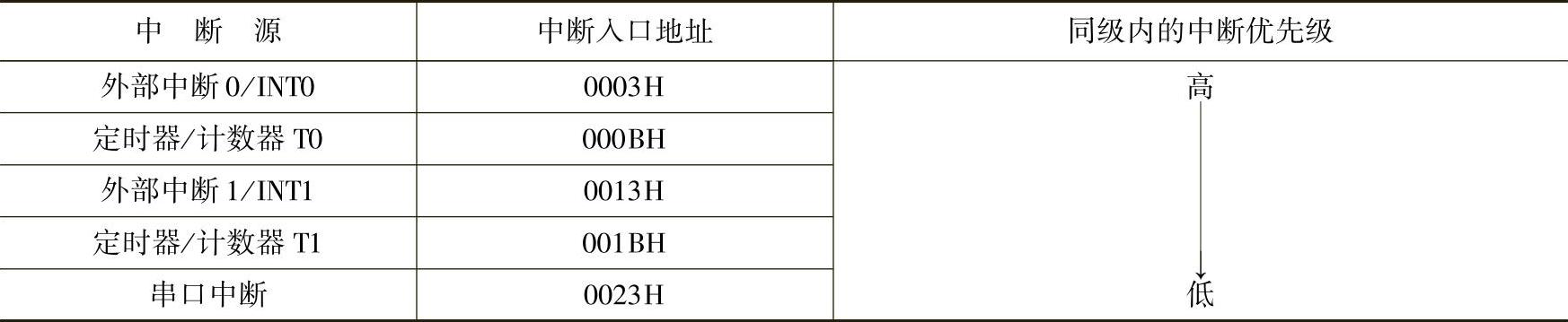

3.中断优先级

MCS-51系列单片机有5个中断源,当两个及两个以上中断源同时向CPU申请中断时,CPU必须确定首先响应哪个,即不同的中断源有不同的优先级。在MCS-51中每一个中断源有程序控制为允许中断或禁止中断。当CPU执行关中断指令(或系统复位)后,将屏蔽所有的中断请求;当CPU执行开中断指令以后才有可能接收中断请求。每一个中断源可编程控制为最高优先级中断或低优先级中断,能实现两级中断嵌套。

当同时收到几个同一优先级的中断请求时,响应哪一个中断源则取决于内部硬件查询顺序。其优先级顺序排列见表3-5。

表3-5 中断优先级顺序

中断处理结束返回主程序后,至少要执行一条指令,才能响应新的中断请求。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。