【摘要】:DM9000A支持IEEE 802.3x全双工流量控制。DM9000A的处理器接口用来连接各种处理器,它的寻址方式有两种:一种是INDEX端口,一种是DATA端口。DM9000A集成有接收缓冲区,以便在接收到数据时能把数据放到这个缓冲区中,然后由数据链路层直接从该缓冲区里取走数据。DM9000A还提供了DMA功能,简化了内部存储器的访问。DM9000A的主要特性如下:一个通用主机接口,用来连接各种处理器。DM9000A的主要寄存器见表13-1~表13-6。

DM9000A是一款高度集成的单芯片快速以太网MAC控制器,它包含一个通用处理器接口、一个10/100M PHY和一个4KB大小的双字节SRAM。DM9000A支持IEEE 802.3x全双工流量控制。DM9000A的处理器接口用来连接各种处理器,它的寻址方式有两种:一种是INDEX端口,一种是DATA端口。当管脚CMD为1,当前访问DATA端口,否则访问INDEX端口。INDEX端口的内容就是DATA端口的寄存器地址。DM9000A集成有接收缓冲区,以便在接收到数据时能把数据放到这个缓冲区中,然后由数据链路层直接从该缓冲区里取走数据。DM9000A还提供了DMA功能,简化了内部存储器的访问。DM9000A的主要特性如下:

(1)一个通用主机接口,用来连接各种处理器。

(2)集成10/100M物理层(PHY)接口。

(3)内部带有16KB的SRAM,用作接收发送的FIFO缓存。

(4)支持8/16bit两种主机工作模式。

(5)集成了EEPROM,用来保存初始化参数,实现自动配置。

(6)一个MII接口,用于连接HPNA设备或其他支持MII的收发器。

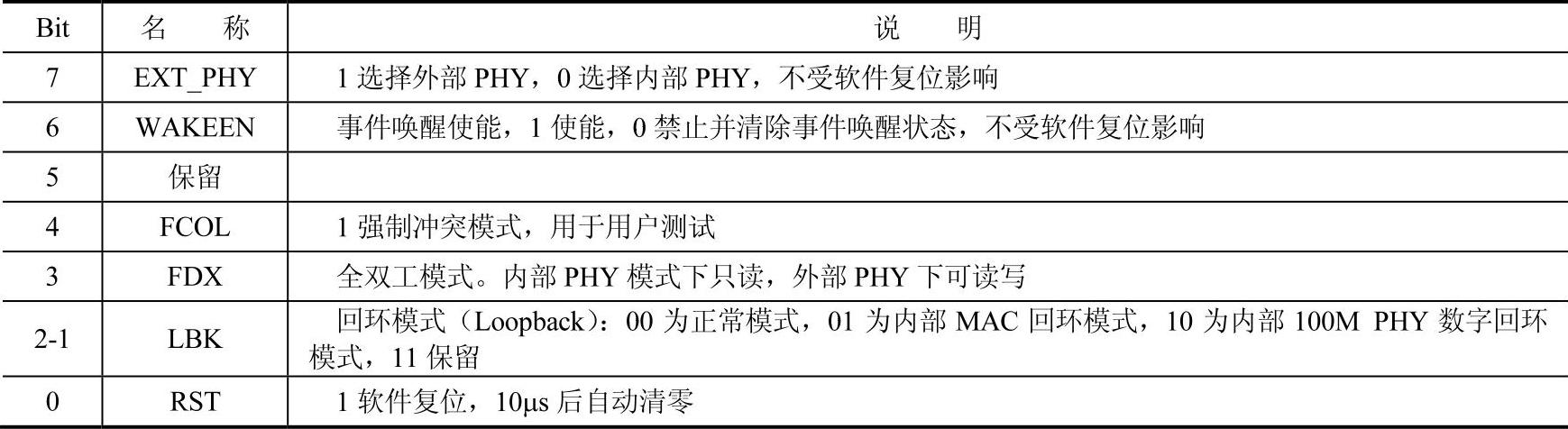

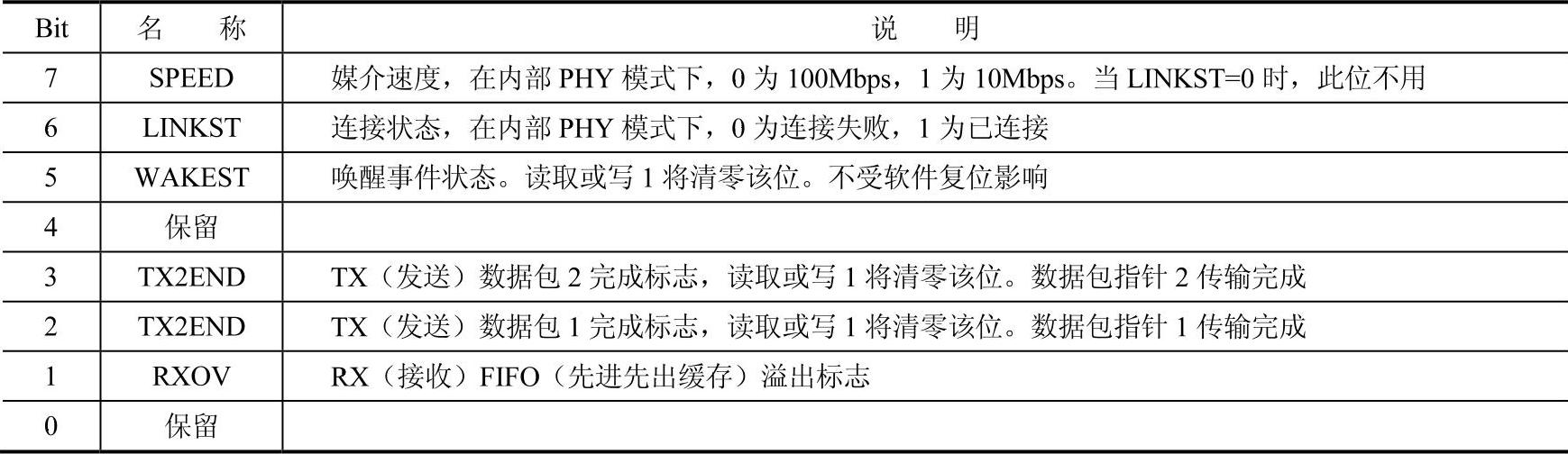

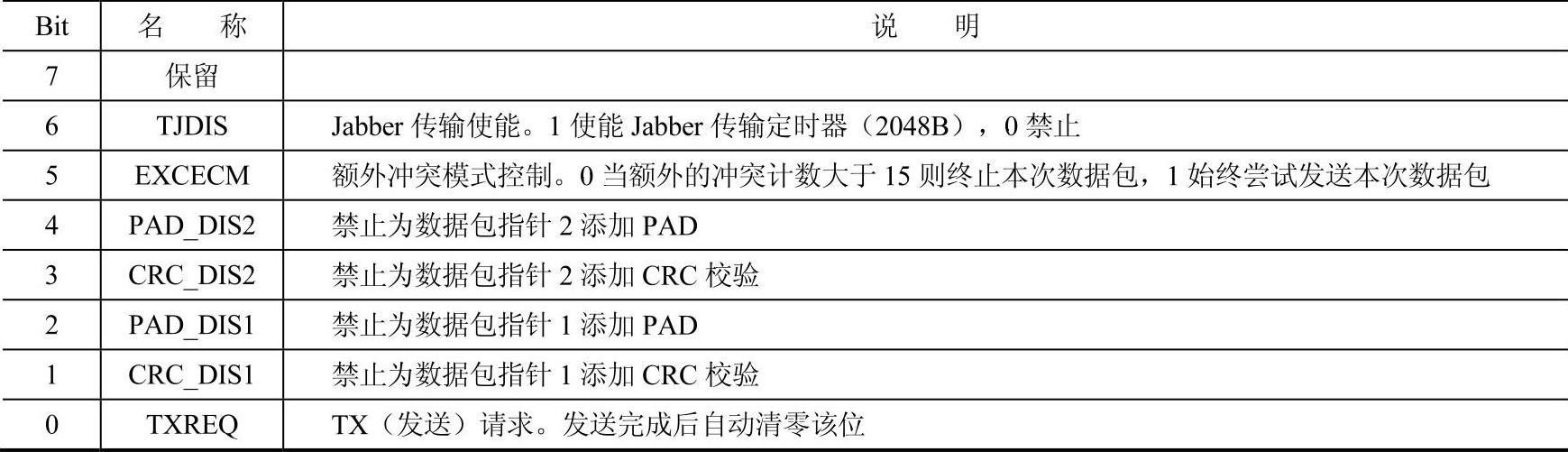

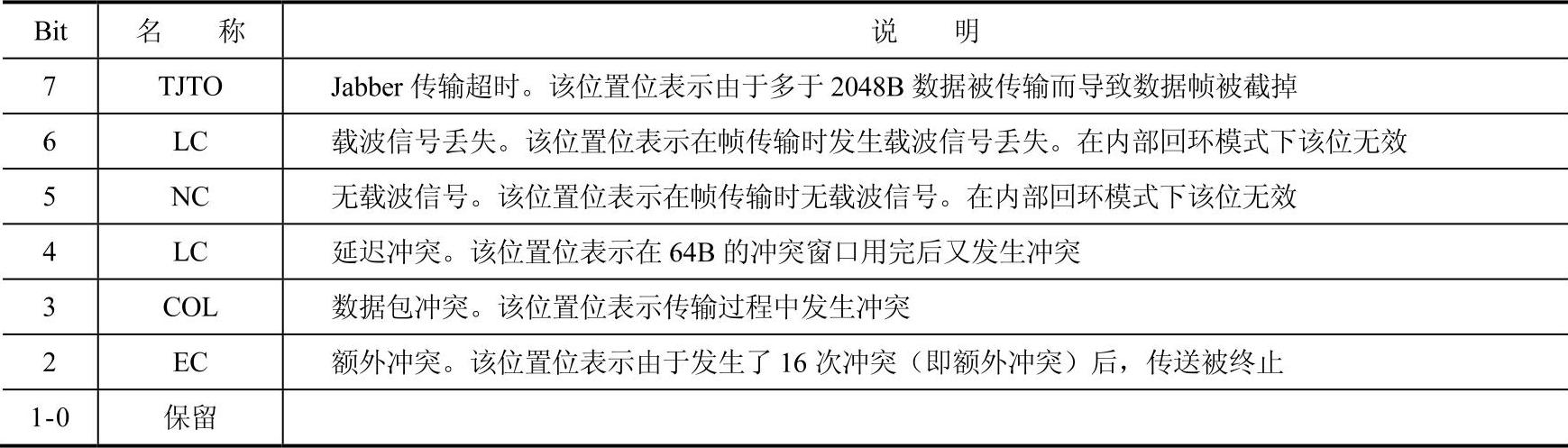

DM9000A的主要寄存器见表13-1~表13-6。

表13-1 网络控制寄存器DM_NCR(0x00)

表13-2 网络状态寄存器DM_NSR(0x01)(https://www.xing528.com)

表13-3 发送控制寄存器DM_TCR(0x02)

表13-4 数据包指针的发送状态寄存器1 TSR_I(03H)与2 TSR_I(04H)

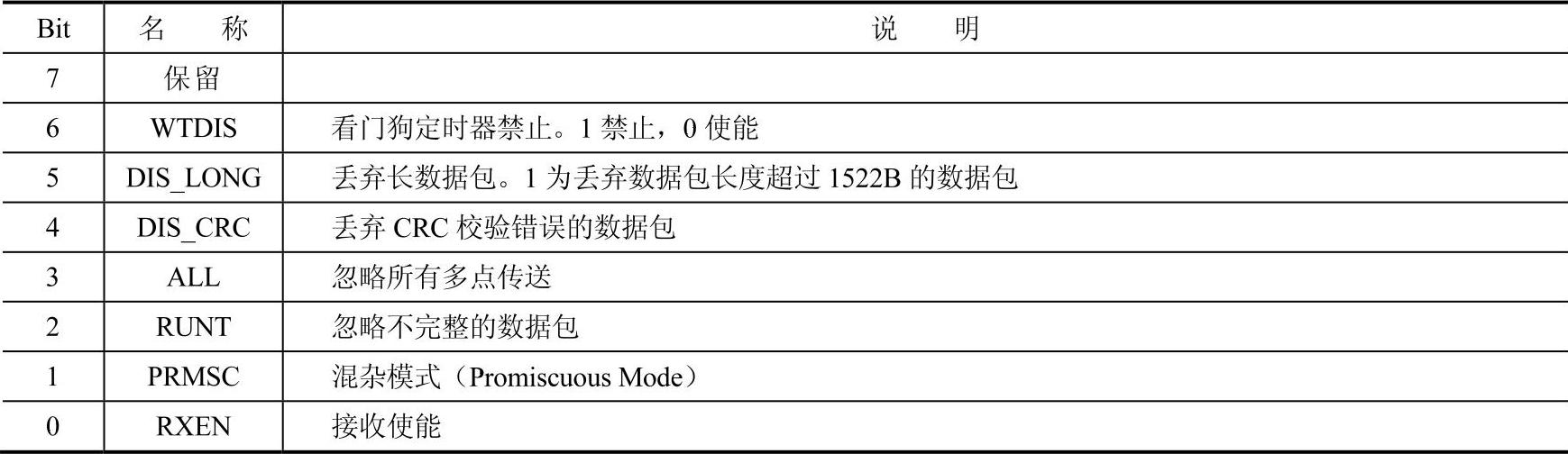

表13-5 接收控制寄存器RCR(05H)

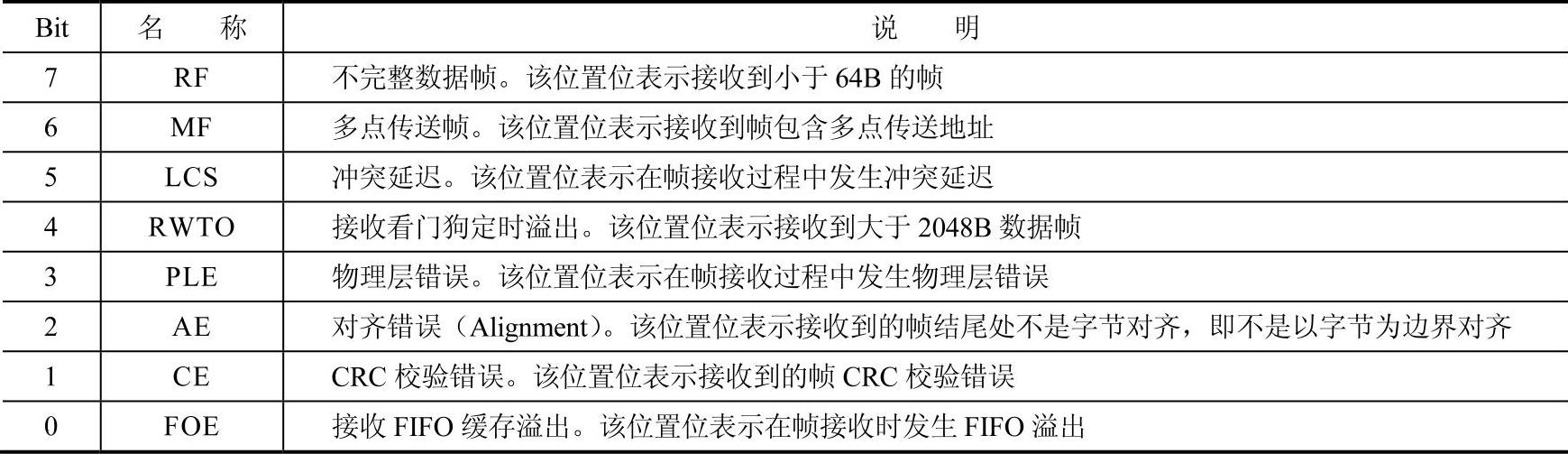

表13-6 接收状态寄存器RSR(06H)

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。