I2C(Inter-Integrated Circuit)总线是一种由Philips公司开发的两线式串行总线,用于连接微控制器及其外围设备。在物理结构上,I2C总线由数据线SDA和时钟SCL构成,每个器件都有一个唯一的地址识别。发送数据到总线的器件叫作发送器,从总线接收数据的器件叫作接收器。初始化发送产生时钟信号和终止发送的器件叫作主机,被主机寻址的器件叫作从机。

I2C总线最主要的优点是简单性和有效性。由于接口集成在组件之上,因此I2C总线占用的空间非常小,减少了电路板的空间和芯片管脚的数量,降低了互联成本。总线的长度可达25ft(7.62m),并且能够以10kbit/s的最大传输速率支持40个组件。

I2C总线的另一个优点是支持多主控制,其中任何能够进行发送和接收的设备都可以成为主总线。I2C总线上在任何时刻只能有一个主机,主机能够控制信号的传输和时钟频率。当有多于一个主机尝试控制总线时,通过仲裁只使能其中一个控制总线并使报文不被破坏。仲裁原则是当多个主器件同时想占用总线时,如果某个主器件发送高电平,而另一个主器件发送低电平,则发送电平与此时SDA总线电平不符的那个器件将自动关闭其输出级。总线竞争的仲裁是在两个层次上进行的。首先是地址位的比较,如果主器件寻址同一个从器件,则进入数据位的比较,从而确保了竞争仲裁的可靠性。由于是利用I2C总线上的信息进行仲裁,因此不会造成信息的丢失。

这里以AT24Cxx EEPROM为例说明I2C设备原理。AT24Cxx系列EEPROM是由美国Microchip公司出品的支持I2C总线数据传送协议的串行E2PROM,可用电擦除,自动擦除时间不超过10ms。串行E2PROM一般具有两种写入方式,一种是字节写入方式,另一种是页写入方式。允许在一个写周期内同时对1个字节到一页的若干字节的编程写入,单页的大小取决于芯片内页寄存器的大小。AT24C02具有16B数据的页面写能力。

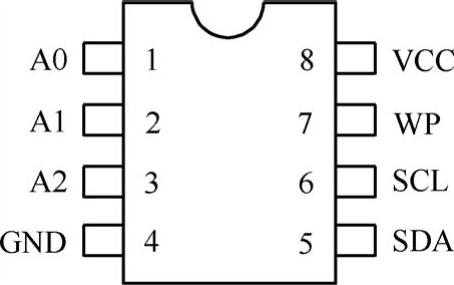

AT24C02包含8个管脚,SCL为串行时钟,SDA为串行数据/地址,A0、A1、A2为器件地址输入端;WP为写保护脚,电平为高则芯片只读,Vcc为电源。如图7-1所示。

图7-1 AT24Cxx系列EEPROM管脚

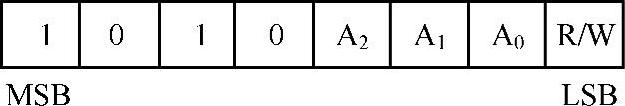

AT24Cxx系列EEPROM的8位I2C地址的计算方法是前四位为固定的1010,后面三位由A2、A1、A0管脚决定,最后一位代表读写,为1表示读,为0表示写。如图7-2所示。

图7-2 AT24Cxx的I2C地址

下面具体说明AT24Cxx的I2C总线时序。

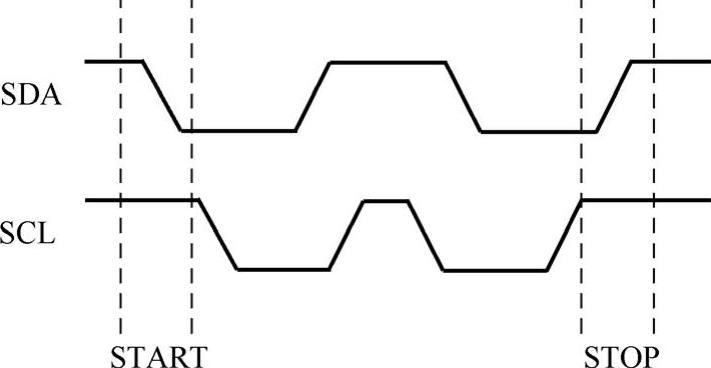

(1)开始条件(START)

在SCL线处于高电平时,SDA线从高电平向低电平切换,表示一个开始信号。

(2)停止条件(STOP)

当SCL线处于高电平时,SDA线由低电平向高电平切换,表示一个停止条件。

开始和停止条件如图7-3所示。(https://www.xing528.com)

图7-3 开始和停止条件

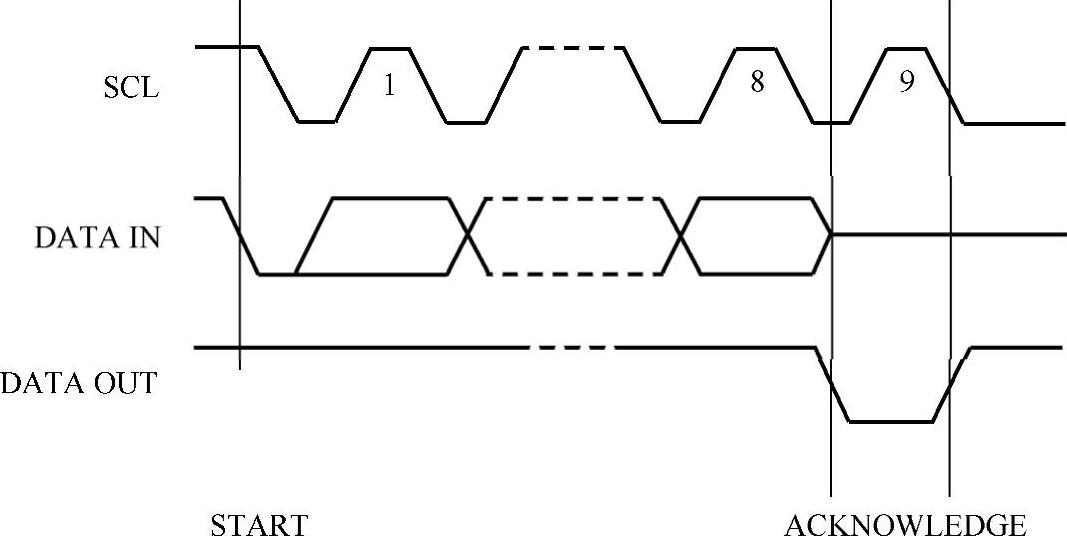

(3)数据传输

SDA线上的数据必须在时钟的高电平周期保持稳定,数据线的高或低电平状态只有在SCL线的时钟信号是低电平时才能改变,否则将代表开始和停止条件出现。总线在起始条件后被认为处于忙的状态,在停止条件的某段时间后总线被认为再次处于空闲状态。

发送到SDA线上的每个字节必须为8bit。每次传输可以发送的字节数量不受限制。每个字节后必须跟一个响应位(ACK)。首先传输的是数据的最高位MSB。在响应时钟脉冲期间,接收器必须将SDA线拉低,使它在这个时钟脉冲的高电平期间保持稳定的低电平。图7-4是I2C数据传送时序图。

图7-4 I2C数据传送时序

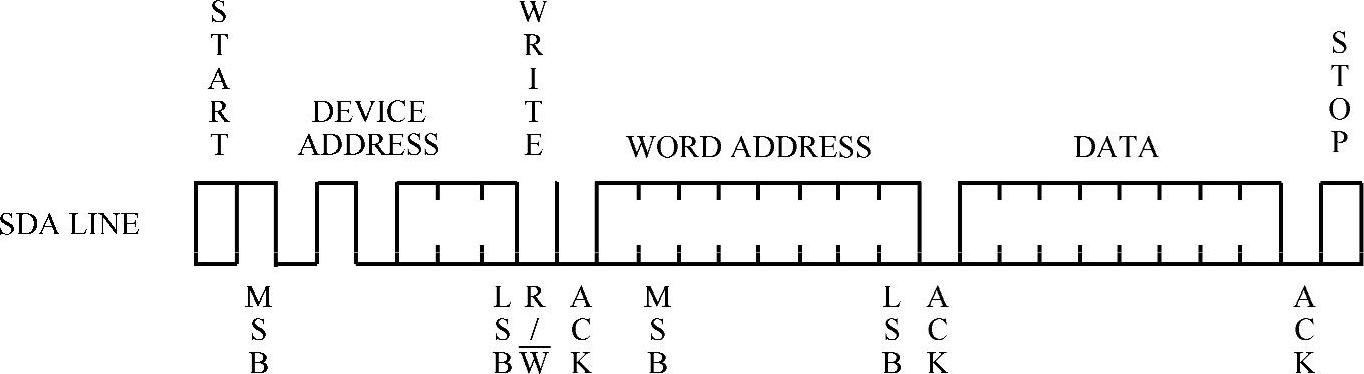

(4)单字节写

单字节写的流程是开始条件后发送器件写地址,然后发送器件内部地址,最后发送数据,每发送一个字节都要有应答。图7-5是I2C单字节写时序图。

图7-5 I2C单字节写时序

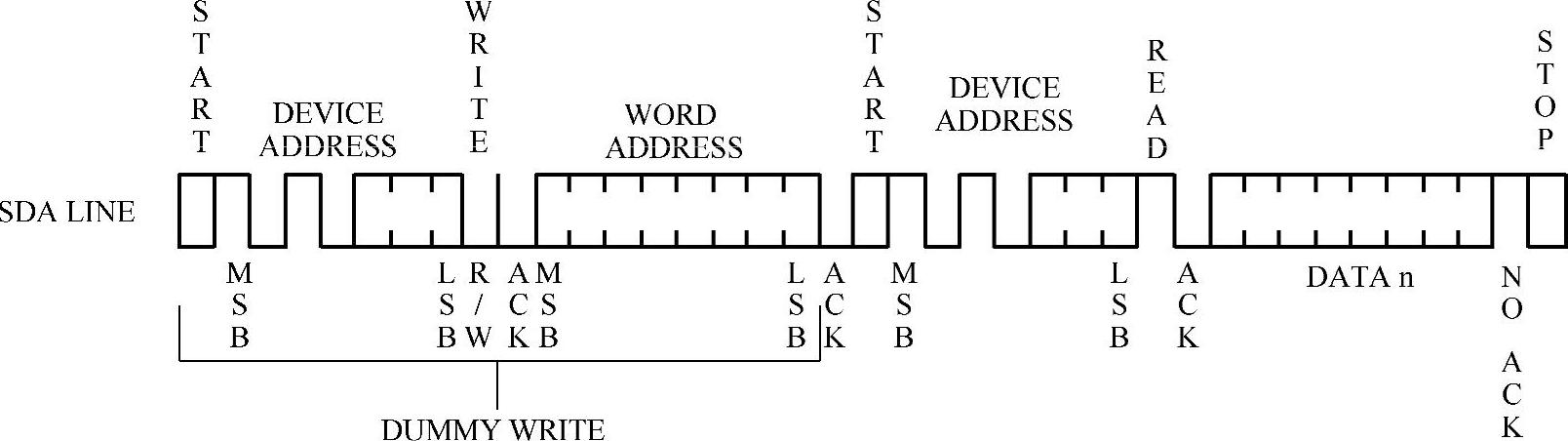

(5)单字节读

单字节读的流程是开始条件后发送器件写地址,然后发送器件内部地址,结束后再发一个开始条件,接着发送器件读地址,最后接收数据,每发送一个字节都要有应答。图7-6是I2C单字节读时序图。

图7-6 I2C单字节读时序

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。