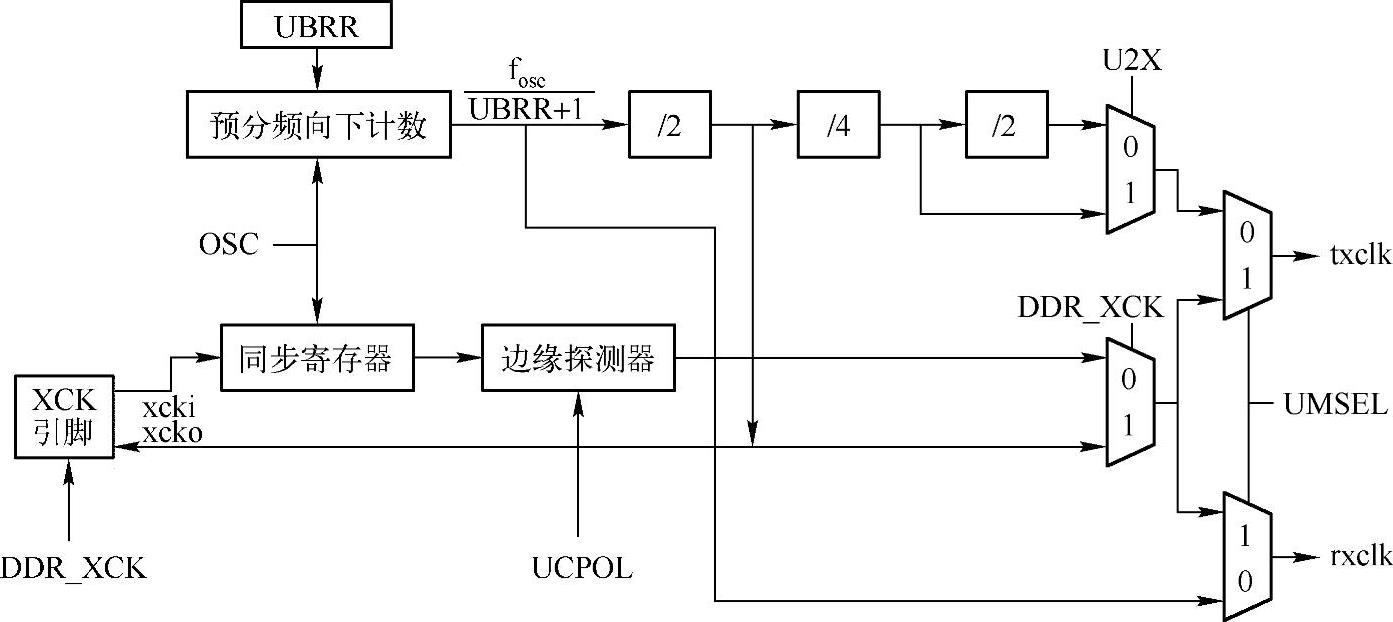

时钟产生逻辑为发送器和接收器产生基础时钟。USART支持4种模式的时钟:正常的异步模式、倍速的异步模式、主机同步模式,以及从机同步模式。USART控制位UMSEL和状态寄存器C(UCSRC)用于选择异步模式和同步模式。倍速模式(只适用于异步模式)受控于UCSRA寄存器的U2X。使用同步模式(UMSEL=1)时,XCK的数据方向寄存器(DDR_XCK)决定时钟源是由内部产生(主机模式)还是由外部产生(从机模式)。仅在同步模式下XCK有效。

图10-6为时钟产生逻辑的框图。

●Txclk:发送器时钟(内部信号)。

●rxclk:接收器基础时钟(内部信号)。

●xcki:XCK引脚输入(内部信号),用于同步从机操作。

●xcko:输出到XCK引脚的时钟(内部信号),用于同步主机操作。

●fosc:XTAL频率(系统时钟)。

图10-6 USART时钟产生逻辑框图

1.片内时钟产生——波特率发生器

内部时钟用于异步模式与同步主机模式,如图10-6所示。USART的波特率寄存器UBRR和降序计数器相连接,一起构成可编程的预分频器或波特率发生器。降序计数器对系统时钟计数,当其计数到零或UBRRL寄存器被写时,会自动装入UBRR寄存器的值。当计数到零时产生一个时钟,该时钟作为波特率发生器的输出时钟,输出时钟的频率为fosc/(UBRR+1)。发生器对波特率发生器的输出时钟进行2、8或16的分频,具体情况取决于工作模式。波特率发生器的输出被直接用于接收器与数据恢复单元。数据恢复单元使用了一个有2、8或16个状态的状态机,具体状态数由UMSEL、U2X与DDR_XCK位设定的工作模式决定。

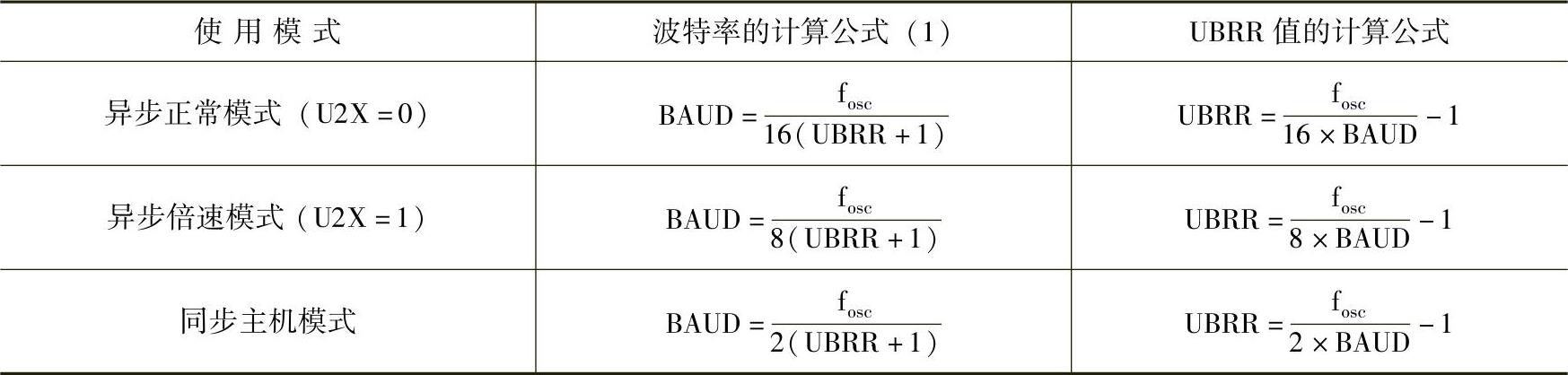

表10-5给出了计算波特率(bit/s)以及计算每一种使用内部时钟源工作模式的UBRR值的公式。

表10-5 波特率计算公式

注意:波特率定义为每秒的位传输速度(bit/s)

表中符号定义如下:

●波特率(bit/s)。

●fosc系统时钟频率。

●UBRR、UBRRH与UBRRL的数值(0~4095)。

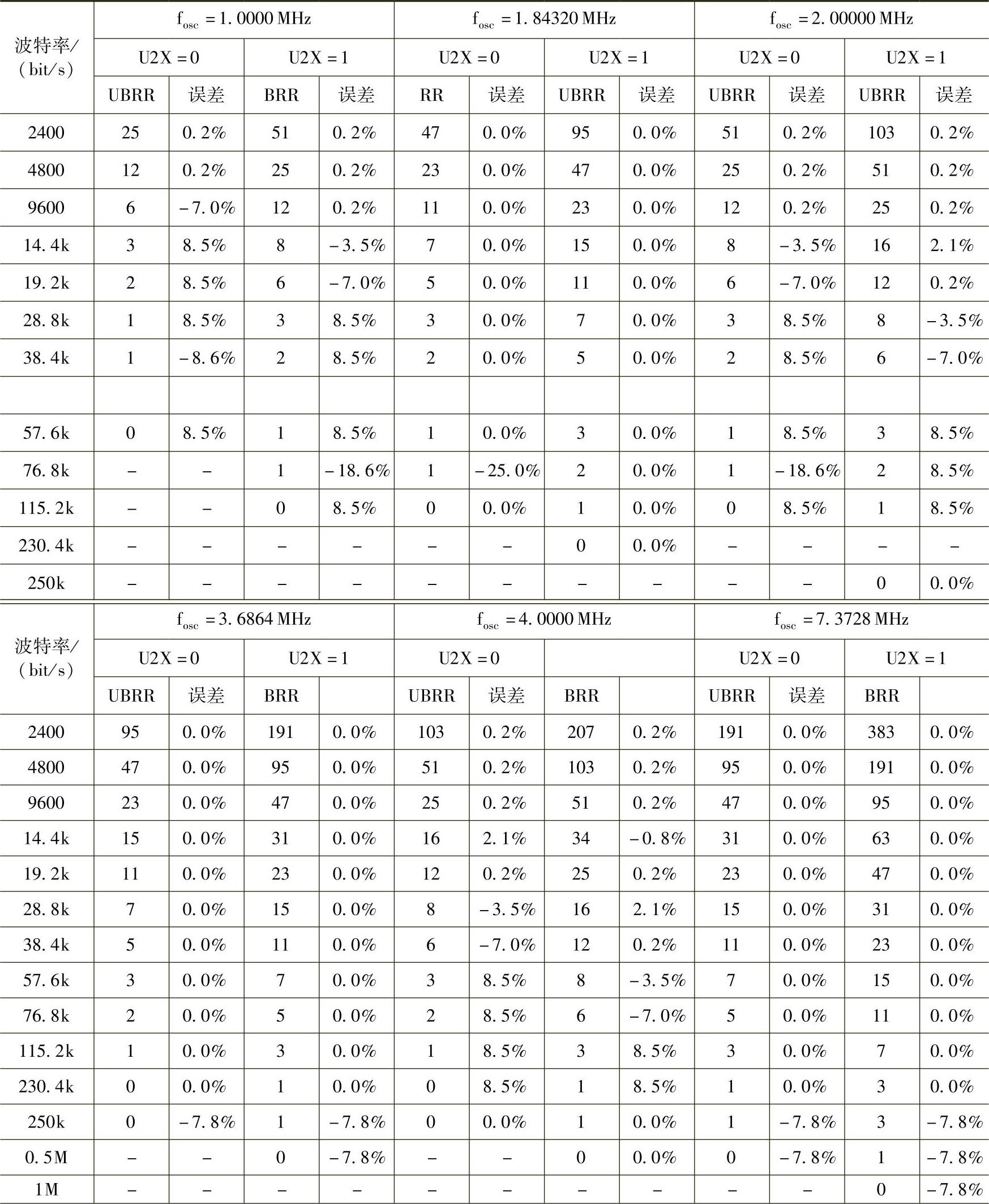

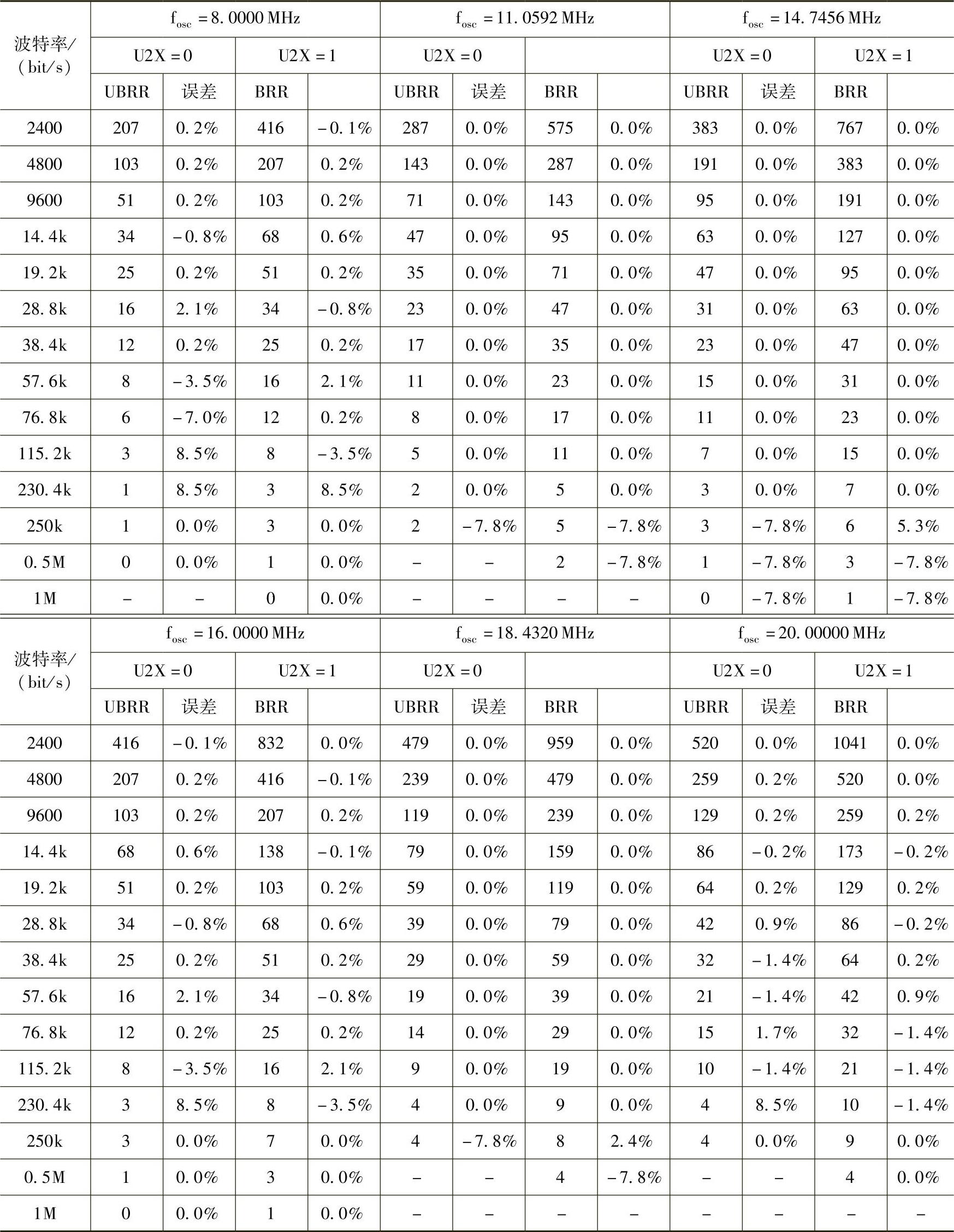

表10-6给出了在某些系统时钟频率下对应的UBRR数值。

表10-6 钟频率和对应的UBRR数值

(续)

2.倍速工作模式(U2X)

通过设定UCSRA寄存器的U2X可以使传输速率加倍。该位只对异步工作模式有效。当工作在同步模式时,设置该位为“0”。设置该位把波特率分频器的分频值从16降到8,使异步通信的传输速率加倍。此时接收器只使用一半的采样数对数据进行采样及时钟恢复,因此在该模式下需要更精确的系统时钟与更精确的波特率设置。发送器则没有这个要求。

3.外部时钟

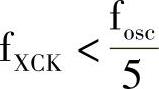

同步从机操作模式由外部时钟驱动,如图10-6所示。输入到XCK引脚的外部时钟由同步寄存器进行采样,用以提高稳定性。同步寄存器的输出通过一个边沿检测器,然后应用于发送器与接收器。这一过程引入了两个CPU时钟周期的延时,因此外部XCK的最大时钟频率由以下公式限制:

要注意fosc由系统时钟的稳定性决定,为了防止因频率漂移而丢失数据,建议保留足够的裕量。

4.同步时钟操作(https://www.xing528.com)

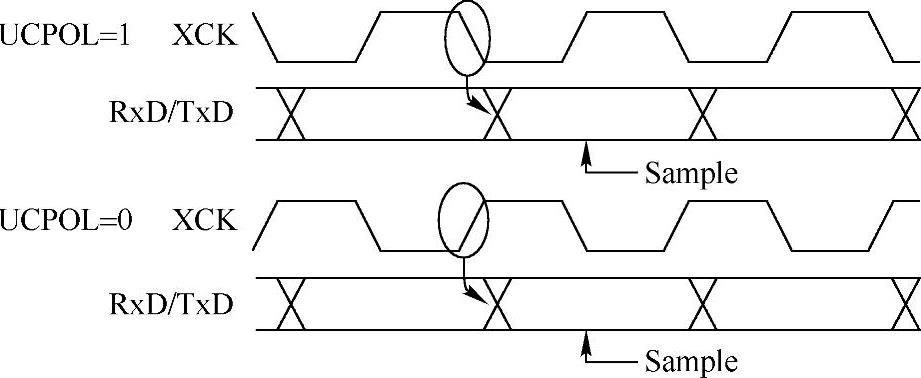

使用同步模式时(UMSEL=1)XCK引脚被用于时钟输入(从机模式)或时钟输出(主机模式)。时钟的边沿、数据的采样与数据的变化之间的关系的基本规律是:在改变数据输出端TxD的XCK时钟的相反边沿对数据输入端RxD进行采样。

UCRSC寄存器的UCPOL位确定使用XCK时钟的哪个边沿对数据进行采样和改变输出数据。如图10-7所示,当UCPOL=0时,在XCK的上升沿改变输出数据,在XCK的下降沿进行数据采样;当UCPOL=1时,在XCK的下降沿改变输出数据,在XCK的上升沿进行数据采样。

图10-7 同步模式时的XCK时序

5.帧格式

串行数据帧由数据字加上同步位(开始位与停止位)以及用于纠错的奇偶校验位构成。USART接受以下30种组合的数据帧格式:

●1个起始位。

●5~9个数据位。

●无校验位、奇校验或偶校验位。

●1或2个停止位。

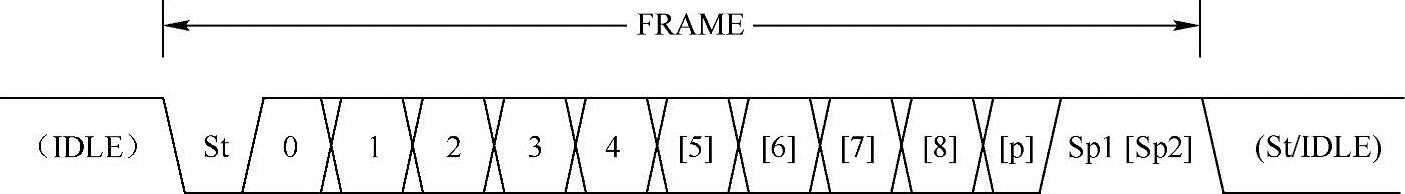

数据帧以起始位开始;紧接着是数据字的最低位,数据字最多可以有9个数据位,以数据的最高位结束。如果使能了校验位,校验位将紧接着数据位,最后是结束位。当一个完整的数据帧传输后,可以立即传输下一个新的数据帧,或使传输线处于空闲状态。

图10-8所示为可能的数据帧结构组合。括号中的位是可选的。

图10-8 数据帧格式

符号说明:

●St起始位,总是为低电平。

●(n)数据位(0~8)。

●P校验位,可以为奇校验或偶校验。

●Sp停止位,总是为高电平。

●IDLE通信线上没有数据传输(RxD或TxD),线路空闲时必须为高电平。

数据帧的结构由UCSRB和UCSRC寄存器中的UCSZ[2∶0]、UPM[1∶0]、USBS设定。接收与发送使用相同的设置。设置的任何改变都可能破坏正在进行的数据传送与接收。

USART的字长位UCSZ[2∶0]确定了数据帧的数据位数;校验模式位UPM[1∶0]用于使能与决定校验的类型;USBS位设置帧有一位或两位结束位。接收器忽略第二个停止位,因此帧错误(FE)只在第一个结束位为“0”时被检测到。

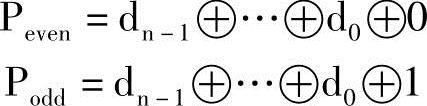

6.校验位的计算

校验位的计算是对数据的各个位进行异或运算。如果选择了奇校验,则异或结果还需要取反。校验位与数据位的关系如下:

●Peven偶校验结果。

●Podd奇校验位结果。

●dn第n个数据位。

校验位处于最后一个数据位与第一个停止位之间。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。